Programs: BC (CS), BS(SE), BS(TELC) Subject: Digital Logic Design Major Assignment Mid-Term Course Code: CSC-201 EDP Code: 102007016 Summer Semester 2020

## **Q.1** Convert each of the following:

- a. 45.25<sub>10</sub> = (?)<sub>2</sub>

- b.  $1000000.1010_2 = (?)_{10}$

- c.  $4D7F_{16} = (?)_{10}$

- d.  $128_{10} = (?)_{16}$

- e.  $3A6F_{16} = (?)_2$

- f.  $1100001111100101_2 = (?)_{16}$

- g.  $6173_8 = (?)_{10}$

- h.  $169_{10} = (?)_8$

- i.  $2A7D_{16} = (?)_8$

- j.  $11111111_2 = \pm (?)_{10}$

- k.  $-12_{10} = (?)_2$

- I. 198 = (?)<sub>BCD</sub>

- m.  $100001110000_{BCD} = (?)_{10}$

- n.  $1001010_2 = (?)_{Gray}$

- 0.  $10101111_{Gray} = (?)_2$

- p. 0100 0001 = (?)<sub>ASCII</sub>

- q. 111000 = (?111000)<sub>Even parity</sub>

hint: [use 2's complement form] hint: [use 2's complement form] Q.2 Calculate each of the following:

| a. | $01111111_2 - 00000111_2$                       | hint: [use 2's complement form]       |

|----|-------------------------------------------------|---------------------------------------|

| b. | 01101010 <sub>2</sub> × 11110001 <sub>2</sub>   | hint: [use 2's complement form]       |

| c. | $10001000_2 \div 00100010_2$                    | hint: [use 2's complement form]       |

| d. | $6D_{16} - 3F_{16}$                             | hint: [use 2's complement form]       |

| e. | $00010110_{BCD} + 0001 \ 0101_{BCD} = (?)_{10}$ | hint: [take care of invalid BCD code] |

- **Q.3** Apply CRC to the data bits 11010011<sub>2</sub> using the generator code 1010<sub>2</sub> to produce the transmitted CRC code.

- **Q.4** Assume that the code produced in problem Q.3 incurs an error in the most significant bit during transmission. Apply CRC to detect the error.

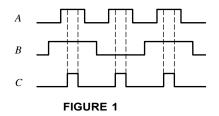

- **Q.5** The input waveforms in Figure 1 is applied to a 3-input AND gate. Show the output waveform in proper relation to the inputs with a timing diagram.

- **Q.6** Repeat Q.5 for a 3-input OR gate.

- **Q.7** Repeat Q.5 for a 3-input NAND gate.

- **Q.8** Repeat Q.5 for a 3-input NOR gate.

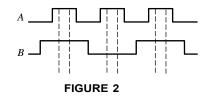

- **Q.9** The input waveforms in Figure 2 is applied to a XOR gate. Show the output waveform in proper relation to the inputs with a timing diagram.

- **Q.10** Repeat Q.9 for XNOR gate.

- Q.11 Using Boolean algebra techniques, simplify the following expressions as much as possible:

$$\overline{AB} + \overline{ABC} + \overline{ABCD} + \overline{ABCDE}$$

- **Q.12** Convert the following expressions to saturdard SOP forms:  $(C + D)(\overline{A} + D)$

- **Q.13** Write the standard POS expression using the standard SOP expression obtained in Q.12.

- **Q.14** Draw a single truth for both the standard POS and standard SOP expression obtained in Q.12 and Q.13.

- **Q.15** Use a Karnaugh map to simplify the following expression to a minimum SOP form:  $\overline{ABC} + \overline{ABC} + \overline{ABC} + \overline{ABC}$

- **Q.16** Obtain the minimum POS expression form the Karnaugh map used in Q.15.

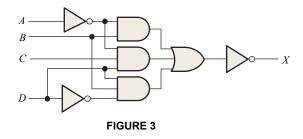

- **Q.17** Write the output expression for circuit in Figure 3.

**Q.18** Implement a logic circuit for the truth table in Table 1.

| TABLE 1 |   |   |        |   |  |

|---------|---|---|--------|---|--|

| Inputs  |   |   | Output |   |  |

| A       | В | С | D      | X |  |

| 0       | 0 | 0 | 0      | 0 |  |

| 0       | 0 | 0 | 1      | 0 |  |

| 0       | 0 | 1 | 0      | 1 |  |

| 0       | 0 | 1 | 1      | 1 |  |

| 0       | 1 | 0 | 0      | 1 |  |

| 0       | 1 | 0 | 1      | 0 |  |

| 0       | 1 | 1 | 0      | 0 |  |

| 0       | 1 | 1 | 1      | 0 |  |

| 1       | 0 | 0 | 0      | 1 |  |

| 1       | 0 | 0 | 1      | 1 |  |

| 1       | 0 | 1 | 0      | 1 |  |

| 1       | 0 | 1 | 1      | 1 |  |

| 1       | 1 | 0 | 0      | 0 |  |

| 1       | 1 | 0 | 1      | 0 |  |

| 1       | 1 | 1 | 0      | 0 |  |

| 1       | 1 | 1 | 1      | 1 |  |