# Boolean Algebra and Logic Simplification

#### **CHAPTER OUTLINE**

- 4–1 Boolean Operations and Expressions

- 4-2 Laws and Rules of Boolean Algebra

- 4-3 DeMorgan's Theorems

- 4-4 Boolean Analysis of Logic Circuits

- 4–5 Logic Simplification Using Boolean Algebra

- 4-6 Standard Forms of Boolean Expressions

- 4–7 Boolean Expressions and Truth Tables

- 4–8 The Karnaugh Map

- 4–9 Karnaugh Map SOP Minimization

- 4-10 Karnaugh Map POS Minimization

- 4-11 The Quine-McCluskey Method

- **4–12** Boolean Expressions with VHDL Applied Logic

#### **CHAPTER OBJECTIVES**

- Apply the basic laws and rules of Boolean algebra

- Apply DeMorgan's theorems to Boolean expressions

- Describe gate combinations with Boolean expressions

- Evaluate Boolean expressions

- Simplify expressions by using the laws and rules of Boolean algebra

- Convert any Boolean expression into a sumof-products (SOP) form

- Convert any Boolean expression into a product of-sums (POS) form

- Relate a Boolean expression to a truth table

- Use a Karnaugh map to simplify Boolean expressions

- Use a Karnaugh map to simplify truth table functions

- Utilize "don't care" conditions to simplify logic functions

- Use the Quine-McCluskey method to simplify Boolean expressions

- Write a VHDL program for simple logic

Apply Boolean algebra and the Karnaugh map method in an application

#### **KEY TERMS**

Key terms are in order of appearance in the chapter.

- Variable

- Complement

- Sum term

- Product term

- Sum-of-products (SOP)

- Product-of-sums (POS)

- Karnaugh map

- Minimization

- "Don't care"

#### **VISIT THE WEBSITE**

Study aids for this chapter are available at http://www.pearsonglobaleditions.com/floyd

#### INTRODUCTION

In 1854, George Boole published a work titled *An Investigation of the Laws of Thought, on Which Are Founded the Mathematical Theories of Logic and Probabilities.* It was in this publication that a "logical algebra," known today as Boolean algebra, was formulated. Boolean algebra is a convenient and systematic way of expressing and analyzing the operation of logic circuits. Claude Shannon was the first to apply Boole's work to the analysis and design of logic circuits. In 1938, Shannon wrote a thesis at MIT titled *A Symbolic Analysis of Relay and Switching Circuits*.

This chapter covers the laws, rules, and theorems of Boolean algebra and their application to digital circuits. You will learn how to define a given circuit with a Boolean expression and then evaluate its operation. You will also learn how to simplify logic circuits using the methods of Boolean algebra, Karnaugh maps, and the Quine-McCluskey method.

Boolean expressions using the hardware description language VHDL are also covered.

# **4–1** Boolean Operations and Expressions

Boolean algebra is the mathematics of digital logic. A basic knowledge of Boolean algebra is indispensable to the study and analysis of logic circuits. In the last chapter, Boolean operations and expressions in terms of their relationship to NOT, AND, OR, NAND, and NOR gates were introduced.

After completing this section, you should be able to

- Define variable

- Define literal

- Identify a sum term

- Evaluate a sum term

- Identify a product term

- Evaluate a product term

- Explain Boolean addition

- Explain Boolean multiplication

*Variable, complement,* and *literal* are terms used in Boolean algebra. A **variable** is a symbol (usually an italic uppercase letter or word) used to represent an action, a condition, or data. Any single variable can have only a 1 or a 0 value. The **complement** is the inverse of a variable and is indicated by a bar over the variable (overbar). For example, the complement of the variable A is  $\overline{A}$ . If A = 1, then  $\overline{A} = 0$ . If A = 0, then  $\overline{A} = 1$ . The complement of the variable A is read as "not A" or "A bar." Sometimes a prime symbol rather than an overbar is used to denote the complement of a variable; for example, B' indicates the complement of B. In this book, only the overbar is used. A **literal** is a variable or the complement of a variable.

#### **Boolean Addition**

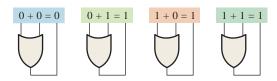

Recall from Chapter 3 that **Boolean addition** is equivalent to the OR operation. The basic rules are illustrated with their relation to the OR gate in Figure 4–1.

#### FIGURE 4-1

In Boolean algebra, a **sum term** is a sum of literals. In logic circuits, a sum term is produced by an OR operation with no AND operations involved. Some examples of sum terms are A + B,  $A + \overline{B}$ ,  $A + B + \overline{C}$ , and  $\overline{A} + B + C + \overline{D}$ .

A sum term is equal to 1 when one or more of the literals in the term are 1. A sum term is equal to 0 only if each of the literals is 0.

# InfoNote

In a microprocessor, the arithmetic logic unit (ALU) performs arithmetic and Boolean logic operations on digital data as directed by program instructions. Logical operations are equivalent to the basic gate operations that you are familiar with but deal with a minimum of 8 bits at a time. Examples of Boolean logic instructions are AND, OR, NOT, and XOR, which are called *mnemonics*. An assembly language program uses the mnemonics to specify an operation. Another program called an assembler translates the mnemonics into a binary code that can be understood by the microprocessor.

The OR operation is the Boolean equivalent of addition.

#### **EXAMPLE 4-1**

Determine the values of A, B, C, and D that make the sum term  $A + \overline{B} + C + \overline{D}$  equal to 0.

#### **Solution**

For the sum term to be 0, each of the literals in the term must be 0. Therefore,  $A = \mathbf{0}$ ,  $B = \mathbf{1}$  so that  $\overline{B} = 0$ ,  $C = \mathbf{0}$ , and  $D = \mathbf{1}$  so that  $\overline{D} = 0$ .

$$A + \overline{B} + C + \overline{D} = 0 + \overline{1} + 0 + \overline{1} = 0 + 0 + 0 + 0 = 0$$

#### **Related Problem\***

Determine the values of A and B that make the sum term  $\overline{A} + B$  equal to 0.

\*Answers are at the end of the chapter.

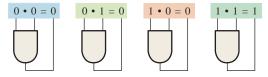

## **Boolean Multiplication**

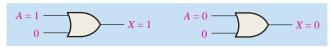

Also recall from Chapter 3 that **Boolean multiplication** is equivalent to the AND operation. The basic rules are illustrated with their relation to the AND gate in Figure 4–2.

The AND operation is the Boolean equivalent of multiplication.

#### FIGURE 4-2

In Boolean algebra, a **product term** is the product of literals. In logic circuits, a product term is produced by an AND operation with no OR operations involved. Some examples of product terms are AB,  $A\overline{B}$ , ABC, and  $A\overline{B}C\overline{D}$ .

A product term is equal to 1 only if each of the literals in the term is 1. A product term is equal to 0 when one or more of the literals are 0.

#### **EXAMPLE 4-2**

Determine the values of A, B, C, and D that make the product term  $A\overline{B}C\overline{D}$  equal to 1.

#### Solution

For the product term to be 1, each of the literals in the term must be 1. Therefore, A = 1, B = 0 so that  $\overline{B} = 1$ , C = 1, and D = 0 so that  $\overline{D} = 1$ .

$$A\overline{B}C\overline{D} = 1 \cdot \overline{0} \cdot 1 \cdot \overline{0} = 1 \cdot 1 \cdot 1 \cdot 1 = 1$$

#### **Related Problem**

Determine the values of A and B that make the product term  $\overline{A}\overline{B}$  equal to 1.

#### SECTION 4-1 CHECKUP

Answers are at the end of the chapter.

- 1. If A = 0, what does  $\overline{A}$  equal?

- **2.** Determine the values of A, B, and C that make the sum term  $\overline{A} + \overline{B} + C$  equal to 0.

- 3. Determine the values of A, B, and C that make the product term  $A\overline{B}C$  equal to 1.

# 4-2 Laws and Rules of Boolean Algebra

As in other areas of mathematics, there are certain well-developed rules and laws that must be followed in order to properly apply Boolean algebra. The most important of these are presented in this section.

After completing this section, you should be able to

- Apply the commutative laws of addition and multiplication

- Apply the associative laws of addition and multiplication

- Apply the distributive law

- Apply twelve basic rules of Boolean algebra

## Laws of Boolean Algebra

The basic laws of Boolean algebra—the **commutative laws** for addition and multiplication, the **associative laws** for addition and multiplication, and the **distributive law**—are the same as in ordinary algebra. Each of the laws is illustrated with two or three variables, but the number of variables is not limited to this.

#### **Commutative Laws**

The commutative law of addition for two variables is written as

$$A + B = B + A$$

Equation 4–1

This law states that the order in which the variables are ORed makes no difference. Remember, in Boolean algebra as applied to logic circuits, addition and the OR operation are the same. Figure 4–3 illustrates the commutative law as applied to the OR gate and shows that it doesn't matter to which input each variable is applied. (The symbol ≡ means "equivalent to.")

$$\begin{bmatrix} A & & & \\ B & & & \\ & & & \end{bmatrix} A + B \equiv \begin{bmatrix} B & & & \\ A & & & \\ \end{bmatrix} B + A$$

FIGURE 4-3 Application of commutative law of addition.

The commutative law of multiplication for two variables is

$$AB = BA$$

Equation 4–2

This law states that the order in which the variables are ANDed makes no difference. Figure 4–4 illustrates this law as applied to the AND gate. Remember, in Boolean algebra as applied to logic circuits, multiplication and the AND function are the same.

$$\begin{array}{c|c} A & & \\ \hline B & & \\ \end{array} \longrightarrow \begin{array}{c} AB & \equiv \begin{array}{c} B & \\ \end{array} \longrightarrow \begin{array}{c} BA \end{array}$$

FIGURE 4-4 Application of commutative law of multiplication.

#### **Associative Laws**

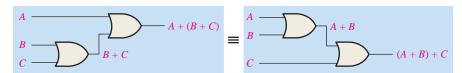

The associative law of addition is written as follows for three variables:

$$A + (B + C) = (A + B) + C$$

Equation 4–3

This law states that when ORing more than two variables, the result is the same regardless of the grouping of the variables. Figure 4–5 illustrates this law as applied to 2-input OR gates.

**FIGURE 4–5** Application of associative law of addition. Open file F04-05 to verify. *A Multisim tutorial is available on the website.*

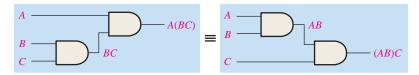

The associative law of multiplication is written as follows for three variables:

$$A(BC) = (AB)C$$

Equation 4–4

This law states that it makes no difference in what order the variables are grouped when ANDing more than two variables. Figure 4–6 illustrates this law as applied to 2-input AND gates.

FIGURE 4-6 Application of associative law of multiplication. Open file F04-06 to verify.

#### **Distributive Law**

The distributive law is written for three variables as follows:

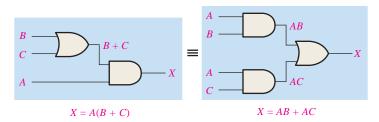

$$A(B + C) = AB + AC$$

Equation 4–5

This law states that ORing two or more variables and then ANDing the result with a single variable is equivalent to ANDing the single variable with each of the two or more variables and then ORing the products. The distributive law also expresses the process of *factoring* in which the common variable A is factored out of the product terms, for example, AB + AC = A(B + C). Figure 4–7 illustrates the distributive law in terms of gate implementation.

FIGURE 4-7 Application of distributive law. Open file F04-07 to verify.

## Rules of Boolean Algebra

Table 4–1 lists 12 basic rules that are useful in manipulating and simplifying **Boolean expressions**. Rules 1 through 9 will be viewed in terms of their application to logic gates. Rules 10 through 12 will be derived in terms of the simpler rules and the laws previously discussed.

A, B, or C can represent a single variable or a combination of variables.

**Rule 1:** A + 0 = A A variable ORed with 0 is always equal to the variable. If the input variable A is 1, the output variable X is 1, which is equal to A. If A is 0, the output is 0, which is also equal to A. This rule is illustrated in Figure 4–8, where the lower input is fixed at 0.

X = A + 0 = A

**Rule 2:** A + 1 = 1 A variable ORed with 1 is always equal to 1. A 1 on an input to an OR gate produces a 1 on the output, regardless of the value of the variable on the other input. This rule is illustrated in Figure 4–9, where the lower input is fixed at 1.

$$X = 1$$

$$X = 1$$

$$X = A + 1 = 1$$

#### FIGURE 4-9

**Rule 3:**  $\mathbf{A} \cdot \mathbf{0} = \mathbf{0}$  A variable ANDed with 0 is always equal to 0. Any time one input to an AND gate is 0, the output is 0, regardless of the value of the variable on the other input. This rule is illustrated in Figure 4–10, where the lower input is fixed at 0.

$$A = 1$$

$$0$$

$$X = 0$$

$$0$$

$$X = A \cdot 0 = 0$$

#### FIGURE 4-10

**Rule 4:**  $A \cdot 1 = A$  A variable ANDed with 1 is always equal to the variable. If A is 0, the output of the AND gate is 0. If A is 1, the output of the AND gate is 1 because both inputs are now 1s. This rule is shown in Figure 4–11, where the lower input is fixed at 1.

$$A = 0$$

$$1$$

$$X = A \cdot 1 = A$$

$$X = A \cdot 1 = A$$

#### FIGURE 4-11

**Rule 5:** A + A = A A variable ORed with itself is always equal to the variable. If A is 0, then 0 + 0 = 0; and if A is 1, then 1 + 1 = 1. This is shown in Figure 4–12, where both inputs are the same variable.

$$A = 0$$

$$A = 0$$

$$X = 0$$

$$X = A + A = A$$

#### **FIGURE 4-12**

**Rule 6:**  $A + \overline{A} = 1$  A variable ORed with its complement is always equal to 1. If A is 0, then  $0 + \overline{0} = 0 + 1 = 1$ . If A is 1, then  $1 + \overline{1} = 1 + 0 = 1$ . See Figure 4–13, where one input is the complement of the other.

$$A = 0$$

$$\overline{A} = 1$$

$$X = 1$$

$$X = A + \overline{A} = 1$$

$$X = A + \overline{A} = 1$$

**Rule 7:**  $\mathbf{A} \cdot \mathbf{A} = \mathbf{A}$  A variable ANDed with itself is always equal to the variable. If A = 0, then  $0 \cdot 0 = 0$ ; and if A = 1, then  $1 \cdot 1 = 1$ . Figure 4–14 illustrates this rule.

$$A = 0$$

$$A = 0$$

$$A = 1$$

$$A = 1$$

$$A = 1$$

$X = A \cdot A = A$

#### FIGURE 4-14

**Rule 8:**  $\vec{A} \cdot \vec{A} = 0$  A variable ANDed with its complement is always equal to 0. Either *A* or  $\vec{A}$  will always be 0; and when a 0 is applied to the input of an AND gate, the output will be 0 also. Figure 4–15 illustrates this rule.

$$A = 1$$

$$\overline{A} = 0$$

$$X = 0$$

$$\overline{A} = 1$$

$$X = 0$$

$$X = A \bullet \overline{A} = 0$$

#### FIGURE 4-15

**Rule 9:**  $\overline{\overline{A}} = A$  The double complement of a variable is always equal to the variable. If you start with the variable A and complement (invert) it once, you get  $\overline{A}$ . If you then take  $\overline{A}$  and complement (invert) it, you get A, which is the original variable. This rule is shown in Figure 4–16 using inverters.

$$A = 0$$

$$\overline{A} = 1$$

$$\overline{A} = 0$$

$$A = 1$$

$$\overline{A} = 0$$

$$\overline{A} = 0$$

$$\overline{A} = 0$$

#### **FIGURE 4-16**

**Rule 10:** A + AB = A This rule can be proved by applying the distributive law, rule 2, and rule 4 as follows:

$$A + AB = A \cdot 1 + AB = A(1 + B)$$

Factoring (distributive law)

=  $A \cdot 1$  Rule 2:  $(1 + B) = 1$

=  $A$  Rule 4:  $A \cdot 1 = A$

The proof is shown in Table 4–2, which shows the truth table and the resulting logic circuit simplification.

| TABLE 4-   | -2        |           |             |                          |

|------------|-----------|-----------|-------------|--------------------------|

| Rule 10: A | + AB = A. | Open file | T04-02 to v | erify.                   |

| A          | В         | AB        | A + AB      | _                        |

| 0          | 0         | 0         | 0           | $A \rightarrow \bigcirc$ |

| 0          | 1         | 0         | 0           |                          |

| 1          | 0         | 0         | 1           | $B \longrightarrow B$    |

| 1          | 1         | 1         | 1           | <b>,</b>                 |

| <u> </u>   | equ       | ual ———   |             | A straight connection    |

**Rule 11:**  $A + \overline{AB} = A + B$  This rule can be proved as follows:

$$A + \overline{A}B = (A + AB) + \overline{A}B \qquad \text{Rule } 10: A = A + AB$$

$$= (AA + AB) + \overline{A}B \qquad \text{Rule } 7: A = AA$$

$$= AA + AB + A\overline{A} + \overline{A}B \qquad \text{Rule } 8: \text{ adding } A\overline{A} = 0$$

$$= (A + \overline{A})(A + B) \qquad \text{Factoring}$$

$$= 1 \cdot (A + B) \qquad \text{Rule } 6: A + \overline{A} = 1$$

$$= A + B \qquad \text{Rule } 4: \text{ drop the } 1$$

The proof is shown in Table 4–3, which shows the truth table and the resulting logic circuit simplification.

## **MultiSim**

#### **TABLE 4-3**

Rule 11:  $A + \overline{A}B = A + B$ . Open file T04-03 to verify.

| A | В | $\overline{A}B$ | $A + \overline{A}B$ | A + B | _                   |

|---|---|-----------------|---------------------|-------|---------------------|

| 0 | 0 | 0               | 0                   | 0     | $A \rightarrow A$   |

| 0 | 1 | 1               | 1                   | 1     |                     |

| 1 | 0 | 0               | 1                   | 1     | В                   |

| 1 | 1 | 0               | 1                   | 1     | A —                 |

|   |   |                 | eq                  | ual 💇 | $B \longrightarrow$ |

**Rule 12:** (A + B)(A + C) = A + BC This rule can be proved as follows:

$$(A + B)(A + C) = AA + AC + AB + BC$$

Distributive law

$= A + AC + AB + BC$  Rule 7:  $AA = A$

$= A(1 + C) + AB + BC$  Factoring (distributive law)

$= A \cdot 1 + AB + BC$  Rule 2:  $1 + C = 1$

$= A(1 + B) + BC$  Factoring (distributive law)

$= A \cdot 1 + BC$  Rule 2:  $1 + B = 1$

$= A + BC$  Rule 4:  $A \cdot 1 = A$

**MultiSim**

The proof is shown in Table 4–4, which shows the truth table and the resulting logic circuit simplification.

## TABLE 4-4

Rule 12: (A + B)(A + C) = A + BC. Open file T04-04 to verify.

| ,                | , , | , |       |       | •          |            |        |                   |

|------------------|-----|---|-------|-------|------------|------------|--------|-------------------|

| $\boldsymbol{A}$ | В   | C | A + B | A + C | (A+B)(A+C) | BC         | A + BC | _                 |

| 0                | 0   | 0 | 0     | 0     | 0          | 0          | 0      |                   |

| 0                | 0   | 1 | 0     | 1     | 0          | 0          | 0      | $A \rightarrow A$ |

| 0                | 1   | 0 | 1     | 0     | 0          | 0          | 0      |                   |

| 0                | 1   | 1 | 1     | 1     | 1          | 1          | 1      | c                 |

| 1                | 0   | 0 | 1     | 1     | 1          | 0          | 1      |                   |

| 1                | 0   | 1 | 1     | 1     | 1          | 0          | 1      | ,                 |

| 1                | 1   | 0 | 1     | 1     | 1          | 0          | 1      | A B               |

| 1                | 1   | 1 | 1     | 1     | 1          | 1          | 1      | c                 |

|                  |     |   |       |       | <u>†</u>   | — equal —— |        |                   |

|                  |     |   |       |       |            | •          |        |                   |

#### **SECTION 4-2 CHECKUP**

- **1.** Apply the associative law of addition to the expression A + (B + C + D).

- **2.** Apply the distributive law to the expression A(B + C + D).

# **4–3** DeMorgan's Theorems

DeMorgan, a mathematician who knew Boole, proposed two theorems that are an important part of Boolean algebra. In practical terms, DeMorgan's theorems provide mathematical verification of the equivalency of the NAND and negative-OR gates and the equivalency of the NOR and negative-AND gates, which were discussed in Chapter 3.

After completing this section, you should be able to

- State DeMorgan's theorems

- Relate DeMorgan's theorems to the equivalency of the NAND and negative-OR gates and to the equivalency of the NOR and negative-AND gates

- Apply DeMorgan's theorems to the simplification of Boolean expressions

DeMorgan's first theorem is stated as follows:

The complement of a product of variables is equal to the sum of the complements of the variables.

To apply DeMorgan's theorem, break the bar over the product of variables and change the sign from AND to OR.

Stated another way,

The complement of two or more ANDed variables is equivalent to the OR of the complements of the individual variables.

The formula for expressing this theorem for two variables is

$$\overline{XY} = \overline{X} + \overline{Y}$$

Equation 4–6

DeMorgan's second theorem is stated as follows:

The complement of a sum of variables is equal to the product of the complements of the variables.

Stated another way,

The complement of two or more ORed variables is equivalent to the AND of the complements of the individual variables.

The formula for expressing this theorem for two variables is

$$\overline{X + Y} = \overline{X}\overline{Y}$$

Equation 4–7

Figure 4–17 shows the gate equivalencies and truth tables for Equations 4–6 and 4–7.

As stated, DeMorgan's theorems also apply to expressions in which there are more than two variables. The following examples illustrate the application of DeMorgan's theorems to 3-variable and 4-variable expressions.

**Inputs**

Output

**FIGURE 4–17** Gate equivalencies and the corresponding truth tables that illustrate DeMorgan's theorems. Notice the equality of the two output columns in each table. This shows that the equivalent gates perform the same logic function.

#### **EXAMPLE 4-3**

Apply DeMorgan's theorems to the expressions  $\overline{XYZ}$  and  $\overline{X+Y+Z}$ .

Solution

$$\overline{XYZ} = \overline{X} + \overline{Y} + \overline{Z}$$

$$\overline{X + Y + Z} = \overline{X} \overline{Y} \overline{Z}$$

#### **Related Problem**

Apply DeMorgan's theorem to the expression  $\overline{X} + \overline{Y} + \overline{Z}$ .

#### **EXAMPLE 4-4**

Apply DeMorgan's theorems to the expressions  $\overline{WXYZ}$  and  $\overline{W+X+Y+Z}$ .

**Solution**

$$\overline{WXYZ} = \overline{W} + \overline{X} + \overline{Y} + \overline{Z}$$

$$\overline{W + X + Y + Z} = \overline{W}\overline{X}\overline{Y}\overline{Z}$$

#### **Related Problem**

Apply DeMorgan's theorem to the expression  $\overline{\overline{W}\overline{X}\overline{Y}\overline{Z}}$ .

Each variable in DeMorgan's theorems as stated in Equations 4–6 and 4–7 can also represent a combination of other variables. For example, X can be equal to the term AB + C, and Y can be equal to the term A + BC. So if you can apply DeMorgan's theorem for two variables as stated by  $\overline{XY} = \overline{X} + \overline{Y}$  to the expression  $\overline{(AB + C)(A + BC)}$ , you get the following result:

$$\overline{(AB + C)(A + BC)} = (\overline{AB + C}) + (\overline{A + BC})$$

Notice that in the preceding result you have two terms,  $\overline{AB + C}$  and  $\overline{A + BC}$ , to each of which you can again apply DeMorgan's theorem  $\overline{X + Y} = \overline{X}\overline{Y}$  individually, as follows:

$$(\overline{AB + C}) + (\overline{A + BC}) = (\overline{AB})\overline{C} + \overline{A}(\overline{BC})$$

Notice that you still have two terms in the expression to which DeMorgan's theorem can again be applied. These terms are  $\overline{AB}$  and  $\overline{BC}$ . A final application of DeMorgan's theorem gives the following result:

$$(\overline{AB})\overline{C} + \overline{A}(\overline{BC}) = (\overline{A} + \overline{B})\overline{C} + \overline{A}(\overline{B} + \overline{C})$$

Although this result can be simplified further by the use of Boolean rules and laws, DeMorgan's theorems cannot be used any more.

## Applying DeMorgan's Theorems

The following procedure illustrates the application of DeMorgan's theorems and Boolean algebra to the specific expression

$$\overline{\overline{A + B\overline{C}} + D(\overline{E + \overline{F}})}$$

- **Step 1:** Identify the terms to which you can apply DeMorgan's theorems, and think of each term as a single variable. Let  $\overline{A + B\overline{C}} = X$  and  $D(\overline{E + \overline{F}}) = Y$ .

- **Step 2:** Since  $\overline{X+Y} = \overline{X}\overline{Y}$ ,

$$\overline{(\overline{A+B\overline{C}})+(\overline{D(E+\overline{F})})}=(\overline{A+B\overline{C}})(\overline{D(E+\overline{F})})$$

**Step 3:** Use rule  $9(\overline{A} = A)$  to cancel the double bars over the left term (this is not part of DeMorgan's theorem).

$$(\overline{\overline{A} + B\overline{C}})(\overline{D(\overline{E} + \overline{F})}) = (A + B\overline{C})(\overline{D(\overline{E} + \overline{F})})$$

**Step 4:** Apply DeMorgan's theorem to the second term.

$$(A + B\overline{C})(\overline{D(E + \overline{F})}) = (A + B\overline{C})(\overline{D} + (\overline{E + \overline{F}}))$$

**Step 5:** Use rule  $9(\overline{\overline{A}} = A)$  to cancel the double bars over the  $E + \overline{F}$  part of the term.

$$(A + B\overline{C})(\overline{D} + \overline{\overline{E + F}}) = (A + B\overline{C})(\overline{D} + E + \overline{F})$$

The following three examples will further illustrate how to use DeMorgan's theorems.

## **EXAMPLE 4-5**

Apply DeMorgan's theorems to each of the following expressions:

- (a)  $\overline{(A+B+C)D}$

- (b)  $\overline{ABC + DEF}$

- (c)  $A\overline{B} + \overline{C}D + EF$

#### **Solution**

(a) Let A+B+C=X and D=Y. The expression  $\overline{(A+B+C)D}$  is of the form  $\overline{XY}=\overline{X}+\overline{Y}$  and can be rewritten as

$$\overline{(A+B+C)D} = \overline{A+B+C} + \overline{D}$$

Next, apply DeMorgan's theorem to the term  $\overline{A + B + C}$ .

$$\overline{A + B + C} + \overline{D} = \overline{A}\overline{B}\overline{C} + \overline{D}$$

(b) Let ABC = X and DEF = Y. The expression  $\overline{ABC + DEF}$  is of the form  $\overline{X + Y} = \overline{X}\overline{Y}$  and can be rewritten as

$$\overline{ABC + DEF} = (\overline{ABC})(\overline{DEF})$$

Next, apply DeMorgan's theorem to each of the terms  $\overline{ABC}$  and  $\overline{DEF}$ .

$$(\overline{ABC})(\overline{DEF}) = (\overline{A} + \overline{B} + \overline{C})(\overline{D} + \overline{E} + \overline{F})$$

(c) Let  $A\overline{B} = X$ ,  $\overline{CD} = Y$ , and EF = Z. The expression  $\overline{AB} + \overline{CD} + EF$  is of the form  $\overline{X} + \overline{Y} + \overline{Z} = \overline{X}\overline{Y}\overline{Z}$  and can be rewritten as

$$\overline{A\overline{B}} + \overline{\overline{C}D} + EF = (\overline{A\overline{B}})(\overline{\overline{C}D})(\overline{EF})$$

Next, apply DeMorgan's theorem to each of the terms  $\overline{AB}$ ,  $\overline{\overline{CD}}$ , and  $\overline{EF}$ .

$$(\overline{AB})(\overline{\overline{CD}})(\overline{EF}) = (\overline{A} + B)(C + \overline{D})(\overline{E} + \overline{F})$$

#### **Related Problem**

Apply DeMorgan's theorems to the expression  $\overline{\overline{ABC} + D + E}$ .

#### **EXAMPLE 4-6**

Apply DeMorgan's theorems to each expression:

(a)

$$\overline{(\overline{A+B})} + \overline{\overline{C}}$$

**(b)**

$$\overline{(\overline{A} + B) + CD}$$

(c)

$$\overline{(A+B)\overline{C}\overline{D}+E+\overline{F}}$$

#### Solution

(a)

$$\overline{(\overline{A+B})} + \overline{\overline{C}} = (\overline{\overline{A+B}})\overline{\overline{C}} = (A+B)C$$

**(b)**

$$\overline{(\overline{A} + B) + CD} = (\overline{\overline{A} + B})\overline{CD} = (\overline{\overline{A}}\overline{B})(\overline{C} + \overline{D}) = A\overline{B}(\overline{C} + \overline{D})$$

(c)

$$\overline{(A+B)\overline{C}\overline{D}+E+\overline{F}} = \overline{((A+B)\overline{C}\overline{D})}(\overline{E+\overline{F}}) = (\overline{A}\overline{B}+C+D)\overline{E}F$$

#### **Related Problem**

Apply DeMorgan's theorems to the expression  $\overline{A}B(C + \overline{D}) + E$ .

#### **EXAMPLE 4-7**

The Boolean expression for an exclusive-OR gate is  $A\overline{B} + \overline{A}B$ . With this as a starting point, use DeMorgan's theorems and any other rules or laws that are applicable to develop an expression for the exclusive-NOR gate.

## **Solution**

Start by complementing the exclusive-OR expression and then applying DeMorgan's theorems as follows:

$$\overline{A\overline{B} + \overline{A}B} = (\overline{A}\overline{B})(\overline{\overline{A}B}) = (\overline{A} + \overline{\overline{B}})(\overline{\overline{A}} + \overline{B}) = (\overline{A} + B)(A + \overline{B})$$

Next, apply the distributive law and rule 8 ( $A \cdot \overline{A} = 0$ ).

$$(\overline{A} + B)(A + \overline{B}) = \overline{A}A + \overline{A}\overline{B} + AB + B\overline{B} = \overline{A}\overline{B} + AB$$

The final expression for the XNOR is  $\overline{AB} + AB$ . Note that this expression equals 1 any time both variables are 0s or both variables are 1s.

## **Related Problem**

Starting with the expression for a 4-input NAND gate, use DeMorgan's theorems to develop an expression for a 4-input negative-OR gate.

#### **SECTION 4-3 CHECKUP**

1. Apply DeMorgan's theorems to the following expressions:

(a)

$$\overline{ABC} + (\overline{\overline{D} + E})$$

(b)

$$\overline{(A+B)C}$$

(c)

$$\overline{A+B+C}+\overline{\overline{D}E}$$

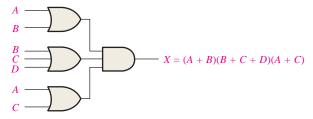

# **4–4** Boolean Analysis of Logic Circuits

Boolean algebra provides a concise way to express the operation of a logic circuit formed by a combination of logic gates so that the output can be determined for various combinations of input values.

After completing this section, you should be able to

- Determine the Boolean expression for a combination of gates

- Evaluate the logic operation of a circuit from the Boolean expression

- Construct a truth table

## Boolean Expression for a Logic Circuit

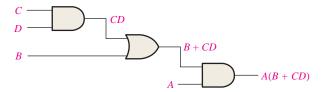

To derive the Boolean expression for a given combinational logic circuit, begin at the left-most inputs and work toward the final output, writing the expression for each gate. For the example circuit in Figure 4–18, the Boolean expression is determined in the following three steps:

A combinational logic circuit can be described by a Boolean equation.

- 1. The expression for the left-most AND gate with inputs C and D is CD.

- **2.** The output of the left-most AND gate is one of the inputs to the OR gate and B is the other input. Therefore, the expression for the OR gate is B + CD.

- **3.** The output of the OR gate is one of the inputs to the right-most AND gate and A is the other input. Therefore, the expression for this AND gate is A(B + CD), which is the final output expression for the entire circuit.

**FIGURE 4–18** A combinational logic circuit showing the development of the Boolean expression for the output.

# Constructing a Truth Table for a Logic Circuit

Once the Boolean expression for a given logic circuit has been determined, a truth table that shows the output for all possible values of the input variables can be developed. The procedure requires that you evaluate the Boolean expression for all possible combinations of values for the input variables. In the case of the circuit in Figure 4–18, there are four input variables (A, B, C, and D) and therefore sixteen  $(2^4 = 16)$  combinations of values are possible.

A combinational logic circuit can be described by a truth table.

## **Evaluating the Expression**

To evaluate the expression A(B + CD), first find the values of the variables that make the expression equal to 1, using the rules for Boolean addition and multiplication. In this case, the expression equals 1 only if A = 1 and B + CD = 1 because

$$A(B + CD) = 1 \cdot 1 = 1$$

Now determine when the B + CD term equals 1. The term B + CD = 1 if either B = 1 or CD = 1 or if both B and CD equal 1 because

$$B + CD = 1 + 0 = 1$$

$B + CD = 0 + 1 = 1$

$B + CD = 1 + 1 = 1$

The term CD = 1 only if C = 1 and D = 1.

To summarize, the expression A(B + CD) = 1 when A = 1 and B = 1 regardless of the values of C and D or when A = 1 and C = 1 and D = 1 regardless of the value of B. The expression A(B + CD) = 0 for all other value combinations of the variables.

## **Putting the Results in Truth Table Format**

The first step is to list the sixteen input variable combinations of 1s and 0s in a binary sequence as shown in Table 4–5. Next, place a 1 in the output column for each combination of input variables that was determined in the evaluation. Finally, place a 0 in the output column for all other combinations of input variables. These results are shown in the truth table in Table 4–5.

| TABLE 4-5                            |              |

|--------------------------------------|--------------|

| Truth table for the logic circuit in | Figure 4–18. |

|                                      |              |

|   | Inp | Output           |   |           |

|---|-----|------------------|---|-----------|

| A | В   | $\boldsymbol{C}$ | D | A(B + CD) |

| 0 | 0   | 0                | 0 | 0         |

| 0 | 0   | 0                | 1 | 0         |

| 0 | 0   | 1                | 0 | 0         |

| 0 | 0   | 1                | 1 | 0         |

| 0 | 1   | 0                | 0 | 0         |

| 0 | 1   | 0                | 1 | 0         |

| 0 | 1   | 1                | 0 | 0         |

| 0 | 1   | 1                | 1 | 0         |

| 1 | 0   | 0                | 0 | 0         |

| 1 | 0   | 0                | 1 | 0         |

| 1 | 0   | 1                | 0 | 0         |

| 1 | 0   | 1                | 1 | 1         |

| 1 | 1   | 0                | 0 | 1         |

| 1 | 1   | 0                | 1 | 1         |

| 1 | 1   | 1                | 0 | 1         |

| 1 | 1   | 1                | 1 | 1         |

#### **EXAMPLE 4-8**

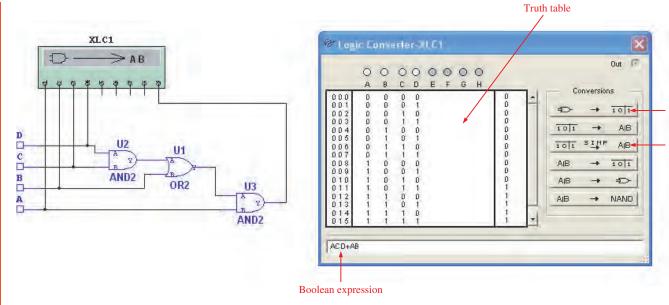

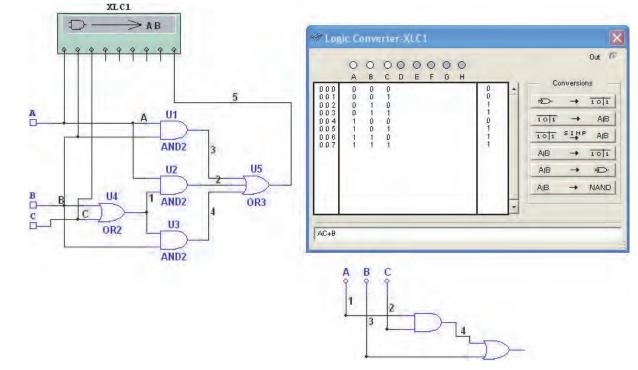

Use Multisim to generate the truth table for the logic circuit in Figure 4–18.

#### **Solution**

Construct the circuit in Multisim and connect the Multisim Logic Converter to the inputs and output, as shown in Figure 4–19. Click on the circuit in Multisim and connect the Multisim Logic Converter to the inputs and output, as shown in Figure 4–19.

You can also generate the simplified Boolean expression from the truth table by clicking on Toll Style Alb.

#### **FIGURE 4-19**

#### **Related Problem**

Open Multisim. Create the setup and do the conversions shown in this example.

#### **SECTION 4-4 CHECKUP**

- 1. Replace the AND gates with OR gates and the OR gate with an AND gate in Figure 4–18. Determine the Boolean expression for the output.

- **2.** Construct a truth table for the circuit in Question 1.

# 4-5 Logic Simplification Using Boolean Algebra

A logic expression can be reduced to its simplest form or changed to a more convenient form to implement the expression most efficiently using Boolean algebra. The approach taken in this section is to use the basic laws, rules, and theorems of Boolean algebra to manipulate and simplify an expression. This method depends on a thorough knowledge of Boolean algebra and considerable practice in its application, not to mention a little ingenuity and cleverness.

After completing this section, you should be able to

Apply the laws, rules, and theorems of Boolean algebra to simplify general expressions

A simplified Boolean expression uses the fewest gates possible to implement a given expression. Examples 4–9 through 4–12 illustrate Boolean simplification.

## **EXAMPLE 4-9**

Using Boolean algebra techniques, simplify this expression:

$$AB + A(B + C) + B(B + C)$$

#### **Solution**

The following is not necessarily the only approach.

**Step 1:** Apply the distributive law to the second and third terms in the expression, as follows:

$$AB + AB + AC + BB + BC$$

**Step 2:** Apply rule 7 (BB = B) to the fourth term.

$$AB + AB + AC + B + BC$$

**Step 3:** Apply rule 5(AB + AB = AB) to the first two terms.

$$AB + AC + B + BC$$

**Step 4:** Apply rule 10 (B + BC = B) to the last two terms.

$$AB + AC + B$$

**Step 5:** Apply rule 10 (AB + B = B) to the first and third terms.

$$B + AC$$

At this point the expression is simplified as much as possible. Once you gain experience in applying Boolean algebra, you can often combine many individual steps.

#### **Related Problem**

Simplify the Boolean expression  $A\overline{B} + A(\overline{B+C}) + B(\overline{B+C})$ .

Simplification means fewer gates for the same function.

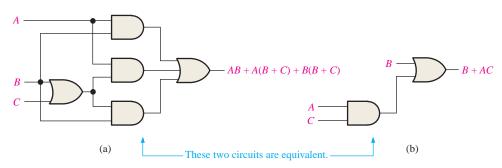

Figure 4–20 shows that the simplification process in Example 4–9 has significantly reduced the number of logic gates required to implement the expression. Part (a) shows that five gates are required to implement the expression in its original form; however, only two gates are needed for the simplified expression, shown in part (b). It is important to realize that these two gate circuits are equivalent. That is, for any combination of levels on the A, B, and C inputs, you get the same output from either circuit.

MultiSim

FIGURE 4–20 Gate circuits for Example 4–9. Open file F04-20 to verify equivalency.

#### **EXAMPLE 4-10**

Simplify the following Boolean expression:

$$[A\overline{B}(C + BD) + \overline{A}\overline{B}]C$$

Note that brackets and parentheses mean the same thing: the term inside is multiplied (ANDed) with the term outside.

#### **Solution**

**Step 1:** Apply the distributive law to the terms within the brackets.

$$(A\overline{B}C + A\overline{B}BD + \overline{A}\overline{B})C$$

**Step 2:** Apply rule  $8 (\overline{B}B = 0)$  to the second term within the parentheses.

$$(A\overline{B}C + A \cdot 0 \cdot D + \overline{A}\overline{B})C$$

**Step 3:** Apply rule 3  $(A \cdot 0 \cdot D = 0)$  to the second term within the parentheses.

$$(A\overline{B}C + 0 + \overline{A}\overline{B})C$$

**Step 4:** Apply rule 1 (drop the 0) within the parentheses.

$$(A\overline{B}C + \overline{A}\overline{B})C$$

**Step 5:** Apply the distributive law.

$$A\overline{B}CC + \overline{A}\overline{B}C$$

**Step 6:** Apply rule 7 (CC = C) to the first term.

$$A\overline{B}C + \overline{A}\overline{B}C$$

**Step 7:** Factor out  $\overline{B}C$ .

$$\overline{B}C(A + \overline{A})$$

**Step 8:** Apply rule 6 ( $A + \overline{A} = 1$ ).

$$\overline{B}C \cdot 1$$

**Step 9:** Apply rule 4 (drop the 1).

$\overline{B}C$

#### **Related Problem**

Simplify the Boolean expression  $[AB(C + \overline{BD}) + \overline{AB}]CD$ .

#### EXAMPLE 4-11

Simplify the following Boolean expression:

$$\overline{A}BC + A\overline{B}\overline{C} + \overline{A}\overline{B}\overline{C} + A\overline{B}C + ABC$$

#### **Solution**

**Step 1:** Factor *BC* out of the first and last terms.

$$BC(\overline{A} + A) + A\overline{B}\overline{C} + \overline{A}\overline{B}\overline{C} + A\overline{B}C$$

**Step 2:** Apply rule  $6(\overline{A} + A = 1)$  to the term in parentheses, and factor  $A\overline{B}$  from the second and last terms.

$$BC \cdot 1 + A\overline{B}(\overline{C} + C) + \overline{A}\overline{B}\overline{C}$$

**Step 3:** Apply rule 4 (drop the 1) to the first term and rule 6 ( $\overline{C} + C = 1$ ) to the term in parentheses.

$$BC + A\overline{B} \cdot 1 + \overline{A}\overline{B}\overline{C}$$

**Step 4:** Apply rule 4 (drop the 1) to the second term.

$$BC + A\overline{B} + \overline{A}\overline{B}\overline{C}$$

**Step 5:** Factor  $\overline{B}$  from the second and third terms.

$$BC + \overline{B}(A + \overline{A}\overline{C})$$

**Step 6:** Apply rule 11  $(A + \overline{A} \overline{C} = A + \overline{C})$  to the term in parentheses.

$$BC + \overline{B}(A + \overline{C})$$

**Step 7:** Use the distributive and commutative laws to get the following expression:

$$BC + A\overline{B} + \overline{B}\overline{C}$$

#### **Related Problem**

Simplify the Boolean expression  $AB\overline{C} + \overline{A}BC + \overline{A}BC + \overline{A}B\overline{C}$ .

#### EXAMPLE 4-12

Simplify the following Boolean expression:

$$\overline{AB + AC} + \overline{A}\overline{B}C$$

#### **Solution**

**Step 1:** Apply DeMorgan's theorem to the first term.

$$(\overline{AB})(\overline{AC}) + \overline{A}\overline{B}C$$

**Step 2:** Apply DeMorgan's theorem to each term in parentheses.

$$(\overline{A} + \overline{B})(\overline{A} + \overline{C}) + \overline{A}\overline{B}C$$

**Step 3:** Apply the distributive law to the two terms in parentheses.

$$\overline{A}\overline{A} + \overline{A}\overline{C} + \overline{A}\overline{B} + \overline{B}\overline{C} + \overline{A}\overline{B}C$$

**Step 4:** Apply rule  $7(\overline{A}\overline{A} = \overline{A})$  to the first term, and apply rule  $10 = \overline{A}\overline{B} + \overline{A}\overline{B}C = \overline{A}\overline{B}(1 + C) = \overline{A}\overline{B}$  to the third and last terms.

$$\overline{A} + \overline{A}\overline{C} + \overline{A}\overline{B} + \overline{B}\overline{C}$$

**Step 5:** Apply rule  $10[\overline{A} + \overline{A}\overline{C} = \overline{A}(1 + \overline{C}) = \overline{A}]$  to the first and second terms.

$$\overline{A} + \overline{A}\overline{B} + \overline{B}\overline{C}$$

**Step 6:** Apply rule  $10[\overline{A} + \overline{A}\overline{B} = \overline{A}(1 + \overline{B}) = \overline{A}]$  to the first and second terms.

$$\overline{A} + \overline{B}\overline{C}$$

#### **Related Problem**

Simplify the Boolean expression  $\overline{AB} + \overline{AC} + \overline{A}\overline{B}\overline{C}$ .

#### EXAMPLE 4-13

Use Multisim to perform the logic simplification shown in Figure 4–20.

#### Solution

- **Step 1:** Connect the Multisim Logic Converter to the circuit as shown in Figure 4–21.

- Step 2: Generate the truth table by clicking on  $\Rightarrow \rightarrow 101$ .

- Step 3: Generate the simplified Boolean expression by clicking on TOTAL SIMP AIB.

- Step 4: Generate the simplified logic circuit by clicking on AB -> => |

#### FIGURE 4-21

#### **Related Problem**

Open Multisim. Create the setup and perform the logic simplification illustrated in this example.

#### **SECTION 4-5 CHECKUP**

- 1. Simplify the following Boolean expressions:

- (a)  $A + AB + A\overline{B}C$

- **(b)**  $(\overline{A} + B)C + ABC$

- (c)  $A\overline{B}C(BD + CDE) + A\overline{C}$

- **2.** Implement each expression in Question 1 as originally stated with the appropriate logic gates. Then implement the simplified expression, and compare the number of gates.

# **4–6** Standard Forms of Boolean Expressions

All Boolean expressions, regardless of their form, can be converted into either of two standard forms: the sum-of-products form or the product-of-sums form. Standardization makes the evaluation, simplification, and implementation of Boolean expressions much more systematic and easier.

After completing this section, you should be able to

- Identify a sum-of-products expression

- Determine the domain of a Boolean expression

- Convert any sum-of-products expression to a standard form

- Evaluate a standard sum-of-products expression in terms of binary values

- Identify a product-of-sums expression

- Convert any product-of-sums expression to a standard form

- Evaluate a standard product-of-sums expression in terms of binary values

- Convert from one standard form to the other

## The Sum-of-Products (SOP) Form

An SOP expression can be implemented with one OR gate and two or more AND gates.

A product term was defined in Section 4–1 as a term consisting of the product (Boolean multiplication) of literals (variables or their complements). When two or more product terms are summed by Boolean addition, the resulting expression is a **sum-of-products** (**SOP**). Some examples are

$$AB + ABC$$

$$ABC + CDE + \overline{B}C\overline{D}$$

$$\overline{A}B + \overline{A}B\overline{C} + AC$$

Also, an SOP expression can contain a single-variable term, as in  $A + \overline{ABC} + BC\overline{D}$ . Refer to the simplification examples in the last section, and you will see that each of the final expressions was either a single product term or in SOP form. In an SOP expression, a single overbar cannot extend over more than one variable; however, more than one variable in a term can have an overbar. For example, an SOP expression can have the term  $\overline{ABC}$  but not  $\overline{ABC}$ .

## **Domain of a Boolean Expression**

The **domain** of a general Boolean expression is the set of variables contained in the expression in either complemented or uncomplemented form. For example, the domain of the expression  $\overline{AB} + A\overline{BC}$  is the set of variables A, B, C and the domain of the expression  $AB\overline{C} + C\overline{DE} + \overline{BCD}$  is the set of variables A, B, C, D, E.

#### **AND/OR Implementation of an SOP Expression**

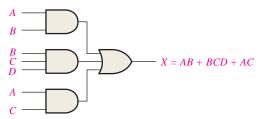

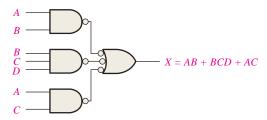

Implementing an SOP expression simply requires ORing the outputs of two or more AND gates. A product term is produced by an AND operation, and the sum (addition) of two or more product terms is produced by an OR operation. Therefore, an SOP expression can be implemented by AND-OR logic in which the outputs of a number (equal to the number of product terms in the expression) of AND gates connect to the inputs of an OR gate, as shown in Figure 4–22 for the expression AB + BCD + AC. The output X of the OR gate equals the SOP expression.

**FIGURE 4–22** Implementation of the SOP expression AB + BCD + AC.

## NAND/NAND Implementation of an SOP Expression

NAND gates can be used to implement an SOP expression. By using only NAND gates, an AND/OR function can be accomplished, as illustrated in Figure 4–23. The first level of NAND gates feed into a NAND gate that acts as a negative-OR gate. The NAND and negative-OR inversions cancel and the result is effectively an AND/OR circuit.

FIGURE 4-23 This NAND/NAND implementation is equivalent to the AND/OR in Figure 4-22.

## Conversion of a General Expression to SOP Form

Any logic expression can be changed into SOP form by applying Boolean algebra techniques. For example, the expression A(B + CD) can be converted to SOP form by applying the distributive law:

$$A(B + CD) = AB + ACD$$

#### **EXAMPLE 4-14**

Convert each of the following Boolean expressions to SOP form:

(a)

$$AB + B(CD + EF)$$

**(b)**

$$(A + B)(B + C + D)$$

**(c)**  $(\overline{A + B}) + C$

(c)

$$\overline{(\overline{A+B})} + \overline{C}$$

#### Solution

(a)

$$AB + B(CD + EF) = AB + BCD + BEF$$

**(b)**

$$(A + B)(B + C + D) = AB + AC + AD + BB + BC + BD$$

(c)

$$\overline{(\overline{A+B})+C} = (\overline{\overline{A+B}})\overline{C} = (A+B)\overline{C} = A\overline{C} + B\overline{C}$$

#### **Related Problem**

Convert  $\overline{A}B\overline{C} + (A + \overline{B})(B + \overline{C} + A\overline{B})$  to SOP form.

#### The Standard SOP Form

So far, you have seen SOP expressions in which some of the product terms do not contain all of the variables in the domain of the expression. For example, the expression  $\overline{ABC} + A\overline{BD} + \overline{ABCD}$  has a domain made up of the variables A, B, C, and D. However, notice that the complete set of variables in the domain is not represented in the first two terms of the expression; that is, D or  $\overline{D}$  is missing from the first term and C or  $\overline{C}$  is missing from the second term.

A standard SOP expression is one in which all the variables in the domain appear in each product term in the expression. For example,  $A\overline{B}CD + AB\overline{C}D + AB\overline{C}D$  is a standard SOP expression. Standard SOP expressions are important in constructing truth tables, covered in Section 4-7, and in the Karnaugh map simplification method, which is covered in Section 4–8. Any nonstandard SOP expression (referred to simply as SOP) can be converted to the standard form using Boolean algebra.

## Converting Product Terms to Standard SOP

Each product term in an SOP expression that does not contain all the variables in the domain can be expanded to standard form to include all variables in the domain and their complements. As stated in the following steps, a nonstandard SOP expression is converted into standard form using Boolean algebra rule 6 ( $A + \overline{A} = 1$ ) from Table 4–1: A variable added to its complement equals 1.

Step 1: Multiply each nonstandard product term by a term made up of the sum of a missing variable and its complement. This results in two product terms. As you know, you can multiply anything by 1 without changing its value.

**Step 2:** Repeat Step 1 until all resulting product terms contain all variables in the domain in either complemented or uncomplemented form. In converting a product term to standard form, the number of product terms is doubled for each missing variable, as Example 4–15 shows.

#### **EXAMPLE 4-15**

Convert the following Boolean expression into standard SOP form:

$$A\overline{B}C + \overline{A}\overline{B} + AB\overline{C}D$$

#### **Solution**

The domain of this SOP expression is A, B, C, D. Take one term at a time. The first term,  $A\overline{B}C$ , is missing variable D or  $\overline{D}$ , so multiply the first term by  $D+\overline{D}$  as follows:

$$A\overline{B}C = A\overline{B}C(D + \overline{D}) = A\overline{B}CD + A\overline{B}C\overline{D}$$

In this case, two standard product terms are the result.

The second term,  $\overline{A}\overline{B}$ , is missing variables C or  $\overline{C}$  and D or  $\overline{D}$ , so first multiply the second term by  $C + \overline{C}$  as follows:

$$\overline{A}\overline{B} = \overline{A}\overline{B}(C + \overline{C}) = \overline{A}\overline{B}C + \overline{A}\overline{B}\overline{C}$$

The two resulting terms are missing variable D or  $\overline{D}$ , so multiply both terms by  $D + \overline{D}$  as follows:

$$\overline{A}\overline{B} = \overline{A}\overline{B}C + \overline{A}\overline{B}\overline{C} = \overline{A}\overline{B}C(D + \overline{D}) + \overline{A}\overline{B}\overline{C}(D + \overline{D})$$

$$= \overline{A}\overline{B}CD + \overline{A}\overline{B}C\overline{D} + \overline{A}\overline{B}\overline{C}D + \overline{A}\overline{B}\overline{C}\overline{D}$$

In this case, four standard product terms are the result.

The third term,  $AB\overline{C}D$ , is already in standard form. The complete standard SOP form of the original expression is as follows:

$$A\overline{B}C + \overline{A}\overline{B} + AB\overline{C}D = A\overline{B}CD + A\overline{B}C\overline{D} + \overline{A}\overline{B}CD + \overline{A}\overline{B}C\overline{D} + \overline{A}\overline{B}\overline{C}D + \overline{A}\overline{B}\overline{C}D + AB\overline{C}D$$

#### **Related Problem**

Convert the expression  $W\overline{X}Y + \overline{X}Y\overline{Z} + WX\overline{Y}$  to standard SOP form.

#### **Binary Representation of a Standard Product Term**

A standard product term is equal to 1 for only one combination of variable values. For example, the product term  $A\overline{B}C\overline{D}$  is equal to 1 when A=1, B=0, C=1, D=0, as shown below, and is 0 for all other combinations of values for the variables.

$$A\overline{B}C\overline{D} = 1 \cdot \overline{0} \cdot 1 \cdot \overline{0} = 1 \cdot 1 \cdot 1 \cdot 1 = 1$$

In this case, the product term has a binary value of 1010 (decimal ten).

Remember, a product term is implemented with an AND gate whose output is 1 only if each of its inputs is 1. Inverters are used to produce the complements of the variables as required.

An SOP expression is equal to 1 only if one or more of the product terms in the expression is equal to 1.

## **EXAMPLE 4–16**

Determine the binary values for which the following standard SOP expression is equal to 1:

$$ABCD + A\overline{B}\overline{C}D + \overline{A}\overline{B}\overline{C}\overline{D}$$

## Solution

The term ABCD is equal to 1 when A = 1, B = 1, C = 1, and D = 1.

$$ABCD = 1 \cdot 1 \cdot 1 \cdot 1 = 1$$

The term  $A\overline{B}\overline{C}D$  is equal to 1 when A = 1, B = 0, C = 0, and D = 1.

$$A\overline{B}\overline{C}D = 1 \cdot \overline{0} \cdot \overline{0} \cdot 1 = 1 \cdot 1 \cdot 1 \cdot 1 = 1$$

The term  $\overline{A}\overline{B}\overline{C}\overline{D}$  is equal to 1 when A = 0, B = 0, C = 0, and D = 0.

$$\overline{A}\overline{B}\overline{C}\overline{D} = \overline{0} \cdot \overline{0} \cdot \overline{0} \cdot \overline{0} = 1 \cdot 1 \cdot 1 \cdot 1 = 1$$

The SOP expression equals 1 when any or all of the three product terms is 1.

#### **Related Problem**

Determine the binary values for which the following SOP expression is equal to 1:

$$\overline{X}YZ + X\overline{Y}Z + XY\overline{Z} + \overline{X}Y\overline{Z} + XYZ$$

Is this a standard SOP expression?

## The Product-of-Sums (POS) Form

A sum term was defined in Section 4–1 as a term consisting of the sum (Boolean addition) of literals (variables or their complements). When two or more sum terms are multiplied, the resulting expression is a **product-of-sums** (**POS**). Some examples are

$$(\overline{A} + B)(A + \overline{B} + C)$$

$$(\overline{A} + \overline{B} + \overline{C})(C + \overline{D} + E)(\overline{B} + C + D)$$

$$(A + B)(A + \overline{B} + C)(\overline{A} + C)$$

A POS expression can contain a single-variable term, as in  $\overline{A}(A + \overline{B} + C)(\overline{B} + \overline{C} + D)$ . In a POS expression, a single overbar cannot extend over more than one variable; however, more than one variable in a term can have an overbar. For example, a POS expression can have the term  $\overline{A} + \overline{B} + \overline{C}$  but not  $\overline{A} + \overline{B} + \overline{C}$ .

#### Implementation of a POS Expression

Implementing a POS expression simply requires ANDing the outputs of two or more OR gates. A sum term is produced by an OR operation, and the product of two or more sum terms is produced by an AND operation. Therefore, a POS expression can be implemented by logic in which the outputs of a number (equal to the number of sum terms in the expression) of OR gates connect to the inputs of an AND gate, as Figure 4–24 shows for the expression (A + B)(B + C + D)(A + C). The output *X* of the AND gate equals the POS expression.

**FIGURE 4–24** Implementation of the POS expression (A + B)(B + C + D)(A + C).

#### The Standard POS Form

So far, you have seen POS expressions in which some of the sum terms do not contain all of the variables in the domain of the expression. For example, the expression

$$(A + \overline{B} + C)(A + B + \overline{D})(A + \overline{B} + \overline{C} + D)$$

has a domain made up of the variables A, B, C, and D. Notice that the complete set of variables in the domain is not represented in the first two terms of the expression; that is, D or  $\overline{D}$  is missing from the first term and C or  $\overline{C}$  is missing from the second term.

A *standard POS expression* is one in which *all* the variables in the domain appear in each sum term in the expression. For example,

$$(\overline{A} + \overline{B} + \overline{C} + \overline{D})(A + \overline{B} + C + D)(A + B + \overline{C} + D)$$

is a standard POS expression. Any nonstandard POS expression (referred to simply as POS) can be converted to the standard form using Boolean algebra.

## **Converting a Sum Term to Standard POS**

Each sum term in a POS expression that does not contain all the variables in the domain can be expanded to standard form to include all variables in the domain and their complements. As stated in the following steps, a nonstandard POS expression is converted into standard form using Boolean algebra rule 8 ( $A \cdot \overline{A} = 0$ ) from Table 4–1: A variable multiplied by its complement equals 0.

- **Step 1:** Add to each nonstandard product term a term made up of the product of the missing variable and its complement. This results in two sum terms. As you know, you can add 0 to anything without changing its value.

- **Step 2:** Apply rule 12 from Table 4–1: A + BC = (A + B)(A + C)

- **Step 3:** Repeat Step 1 until all resulting sum terms contain all variables in the domain in either complemented or uncomplemented form.

#### **EXAMPLE 4-17**

Convert the following Boolean expression into standard POS form:

$$(A + \overline{B} + C)(\overline{B} + C + \overline{D})(A + \overline{B} + \overline{C} + D)$$

#### **Solution**

The domain of this POS expression is A, B, C, D. Take one term at a time. The first term,  $A + \overline{B} + C$ , is missing variable D or  $\overline{D}$ , so add  $D\overline{D}$  and apply rule 12 as follows:

$$A + \overline{B} + C = A + \overline{B} + C + D\overline{D} = (A + \overline{B} + C + D)(A + \overline{B} + C + \overline{D})$$

The second term,  $\overline{B} + C + \overline{D}$ , is missing variable A or  $\overline{A}$ , so add  $A\overline{A}$  and apply rule 12 as follows:

$$\overline{B} + C + \overline{D} = \overline{B} + C + \overline{D} + A\overline{A} = (A + \overline{B} + C + \overline{D})(\overline{A} + \overline{B} + C + \overline{D})$$

The third term,  $A + \overline{B} + \overline{C} + D$ , is already in standard form. The standard POS form of the original expression is as follows:

$$(A + \overline{B} + C)(\overline{B} + C + \overline{D})(A + \overline{B} + \overline{C} + D) = (A + \overline{B} + C + D)(A + \overline{B} + C + \overline{D})(A + \overline{B} + C + \overline{D})(\overline{A} + \overline{B} + C + \overline{D})(A + \overline{B} + \overline{C} + D)$$

#### **Related Problem**

Convert the expression  $(A + \overline{B})(B + C)$  to standard POS form.

#### **Binary Representation of a Standard Sum Term**

A standard sum term is equal to 0 for only one combination of variable values. For example, the sum term  $A + \overline{B} + C + \overline{D}$  is 0 when A = 0, B = 1, C = 0, and D = 1, as shown below, and is 1 for all other combinations of values for the variables.

$$A + \overline{B} + C + \overline{D} = 0 + \overline{1} + 0 + \overline{1} = 0 + 0 + 0 + 0 = 0$$

In this case, the sum term has a binary value of 0101 (decimal 5). Remember, a sum term is implemented with an OR gate whose output is 0 only if each of its inputs is 0. Inverters are used to produce the complements of the variables as required.

A POS expression is equal to 0 only if one or more of the sum terms in the expression is equal to 0.

#### **EXAMPLE 4–18**

Determine the binary values of the variables for which the following standard POS expression is equal to 0:

$$(A + B + C + D)(A + \overline{B} + \overline{C} + D)(\overline{A} + \overline{B} + \overline{C} + \overline{D})$$

#### Solution

The term A + B + C + D is equal to 0 when A = 0, B = 0, C = 0, and D = 0.

$$A + B + C + D = 0 + 0 + 0 + 0 = 0$$

The term  $A + \overline{B} + \overline{C} + D$  is equal to 0 when A = 0, B = 1, C = 1, and D = 0.

$$A + \overline{B} + \overline{C} + D = 0 + \overline{1} + \overline{1} + 0 = 0 + 0 + 0 + 0 = 0$$

The term  $\overline{A} + \overline{B} + \overline{C} + \overline{D}$  is equal to 0 when A = 1, B = 1, C = 1, and D = 1.

$$\overline{A} + \overline{B} + \overline{C} + \overline{D} = \overline{1} + \overline{1} + \overline{1} + \overline{1} = 0 + 0 + 0 + 0 = 0$$

The POS expression equals 0 when any of the three sum terms equals 0.

#### **Related Problem**

Determine the binary values for which the following POS expression is equal to 0:

$$(X + \overline{Y} + Z)(\overline{X} + Y + Z)(X + Y + \overline{Z})(\overline{X} + \overline{Y} + \overline{Z})(X + \overline{Y} + \overline{Z})$$

Is this a standard POS expression?

## Converting Standard SOP to Standard POS

The binary values of the product terms in a given standard SOP expression are not present in the equivalent standard POS expression. Also, the binary values that are not represented in the SOP expression are present in the equivalent POS expression. Therefore, to convert from standard SOP to standard POS, the following steps are taken:

- **Step 1:** Evaluate each product term in the SOP expression. That is, determine the binary numbers that represent the product terms.

- **Step 2:** Determine all of the binary numbers not included in the evaluation in Step 1.

- **Step 3:** Write the equivalent sum term for each binary number from Step 2 and express in POS form.

Using a similar procedure, you can go from POS to SOP.

#### **EXAMPLE 4-19**

Convert the following SOP expression to an equivalent POS expression:

$$\overline{A}\overline{B}\overline{C} + \overline{A}B\overline{C} + \overline{A}BC + A\overline{B}C + ABC$$

#### Solution

The evaluation is as follows:

$$000 + 010 + 011 + 101 + 111$$

Since there are three variables in the domain of this expression, there are a total of eight  $(2^3)$  possible combinations. The SOP expression contains five of these combinations, so the POS must contain the other three which are 001, 100, and 110. Remember, these are the binary values that make the sum term 0. The equivalent POS expression is

$$(A + B + \overline{C})(\overline{A} + B + C)(\overline{A} + \overline{B} + C)$$

#### **Related Problem**

Verify that the SOP and POS expressions in this example are equivalent by substituting binary values into each.

#### **SECTION 4–6 CHECKUP**

- Identify each of the following expressions as SOP, standard SOP, POS, or standard POS:

- (a)  $AB + \overline{A}BD + \overline{A}C\overline{D}$

- **(b)**  $(A + \overline{B} + C)(A + B + \overline{C})$

- (c)  $\overline{A}BC + AB\overline{C}$

- (d)  $(A + \overline{C})(A + B)$

- 2. Convert each SOP expression in Question 1 to standard form.

- 3. Convert each POS expression in Question 1 to standard form.

## **4–7** Boolean Expressions and Truth Tables

All standard Boolean expressions can be easily converted into truth table format using binary values for each term in the expression. The truth table is a common way of presenting, in a concise format, the logical operation of a circuit. Also, standard SOP or POS expressions can be determined from a truth table. You will find truth tables in data sheets and other literature related to the operation of digital circuits.

After completing this section, you should be able to

- Convert a standard SOP expression into truth table format

- Convert a standard POS expression into truth table format

- Derive a standard expression from a truth table

- Properly interpret truth table data

## Converting SOP Expressions to Truth Table Format

Recall from Section 4–6 that an SOP expression is equal to 1 only if at least one of the product terms is equal to 1. A truth table is simply a list of the possible combinations of input variable values and the corresponding output values (1 or 0). For an expression with a domain of two variables, there are four different combinations of those variables ( $2^2 = 4$ ). For an expression with a domain of three variables, there are eight different combinations of those variables ( $2^3 = 8$ ). For an expression with a domain of four variables, there are sixteen different combinations of those variables ( $2^4 = 16$ ), and so on.

The first step in constructing a truth table is to list all possible combinations of binary values of the variables in the expression. Next, convert the SOP expression to standard form if it is not already. Finally, place a 1 in the output column (X) for each binary value that makes the standard SOP expression a 1 and place a 0 for all the remaining binary values. This procedure is illustrated in Example 4–20.

#### **EXAMPLE 4-20**

Develop a truth table for the standard SOP expression  $\overline{A}\overline{B}C + A\overline{B}\overline{C} + ABC$ .

#### Solution

There are three variables in the domain, so there are eight possible combinations of binary values of the variables as listed in the left three columns of Table 4–6. The binary values that make the product terms in the expressions equal to 1 are

| TABLE | TABLE 4-6 |   |        |                             |  |  |  |

|-------|-----------|---|--------|-----------------------------|--|--|--|

|       | Inputs    |   | Output |                             |  |  |  |

| A     | В         | C | X      | Product Term                |  |  |  |

| 0     | 0         | 0 | 0      |                             |  |  |  |

| 0     | 0         | 1 | 1      | $\overline{A}\overline{B}C$ |  |  |  |

| 0     | 1         | 0 | 0      |                             |  |  |  |

| 0     | 1         | 1 | 0      |                             |  |  |  |

| 1     | 0         | 0 | 1      | $A\overline{B}\overline{C}$ |  |  |  |

| 1     | 0         | 1 | 0      |                             |  |  |  |

| 1     | 1         | 0 | 0      |                             |  |  |  |

| 1     | 1         | 1 | 1      | ABC                         |  |  |  |

$\overline{ABC}$ : 001;  $\overline{ABC}$ : 100; and  $\overline{ABC}$ : 111. For each of these binary values, place a 1 in the output column as shown in the table. For each of the remaining binary combinations, place a 0 in the output column.

#### **Related Problem**

Create a truth table for the standard SOP expression  $\overline{A}B\overline{C} + A\overline{B}C$ .

## Converting POS Expressions to Truth Table Format

Recall that a POS expression is equal to 0 only if at least one of the sum terms is equal to 0. To construct a truth table from a POS expression, list all the possible combinations of binary values of the variables just as was done for the SOP expression. Next, convert the POS expression to standard form if it is not already. Finally, place a 0 in the output column (X) for each binary value that makes the expression a 0 and place a 1 for all the remaining binary values. This procedure is illustrated in Example 4–21.

#### **EXAMPLE 4-21**

Determine the truth table for the following standard POS expression:

$$(A + B + C)(A + \overline{B} + C)(A + \overline{B} + \overline{C})(\overline{A} + B + \overline{C})(\overline{A} + \overline{B} + C)$$

#### **Solution**

There are three variables in the domain and the eight possible binary values are listed in the left three columns of Table 4–7. The binary values that make the sum terms in the expression equal to 0 are A + B + C: 000;  $A + \overline{B} + C$ : 010;  $A + \overline{B} + \overline{C}$ : 011;  $\overline{A} + B + \overline{C}$ : 101; and  $\overline{A} + \overline{B} + C$ : 110. For each of these binary values, place a 0 in the output column as shown in the table. For each of the remaining binary combinations, place a 1 in the output column.

| TABLE            | TABLE 4-7 |                  |        |                                     |  |  |  |

|------------------|-----------|------------------|--------|-------------------------------------|--|--|--|

|                  | Inputs    |                  | Output |                                     |  |  |  |

| $\boldsymbol{A}$ | В         | $\boldsymbol{C}$ | X      | Sum Term                            |  |  |  |

| 0                | 0         | 0                | 0      | (A + B + C)                         |  |  |  |

| 0                | 0         | 1                | 1      |                                     |  |  |  |

| 0                | 1         | 0                | 0      | $(A + \overline{B} + C)$            |  |  |  |

| 0                | 1         | 1                | 0      | $(A + \overline{B} + \overline{C})$ |  |  |  |

| 1                | 0         | 0                | 1      |                                     |  |  |  |

| 1                | 0         | 1                | 0      | $(\overline{A} + B + \overline{C})$ |  |  |  |

| 1                | 1         | 0                | 0      | $(\overline{A} + \overline{B} + C)$ |  |  |  |

| 1                | 1         | 1                | 1      |                                     |  |  |  |

Notice that the truth table in this example is the same as the one in Example 4–20. This means that the SOP expression in the previous example and the POS expression in this example are equivalent.

#### **Related Problem**

Develop a truth table for the following standard POS expression:

$$(A + \overline{B} + C)(A + B + \overline{C})(\overline{A} + \overline{B} + \overline{C})$$

## Determining Standard Expressions from a Truth Table

To determine the standard SOP expression represented by a truth table, list the binary values of the input variables for which the output is 1. Convert each binary value to the corresponding product term by replacing each 1 with the corresponding variable and each 0 with the corresponding variable complement. For example, the binary value 1010 is converted to a product term as follows:

$$1010 \longrightarrow A\overline{B}C\overline{D}$$

If you substitute, you can see that the product term is 1:

$$A\overline{B}C\overline{D} = 1 \cdot \overline{0} \cdot 1 \cdot \overline{0} = 1 \cdot 1 \cdot 1 \cdot 1 = 1$$

To determine the standard POS expression represented by a truth table, list the binary values for which the output is 0. Convert each binary value to the corresponding sum term by replacing each 1 with the corresponding variable complement and each 0 with the corresponding variable. For example, the binary value 1001 is converted to a sum term as follows:

$$1001 \longrightarrow \overline{A} + B + C + \overline{D}$$

If you substitute, you can see that the sum term is 0:

$$\overline{A} + B + C + \overline{D} = \overline{1} + 0 + 0 + \overline{1} = 0 + 0 + 0 + 0 = 0$$

#### **EXAMPLE 4-22**

From the truth table in Table 4–8, determine the standard SOP expression and the equivalent standard POS expression.

| TABLE 4-8        |        |                  |        |  |  |

|------------------|--------|------------------|--------|--|--|

|                  | Inputs |                  | Output |  |  |

| $\boldsymbol{A}$ | В      | $\boldsymbol{C}$ | X      |  |  |

| 0                | 0      | 0                | 0      |  |  |

| 0                | 0      | 1                | 0      |  |  |

| 0                | 1      | 0                | 0      |  |  |

| 0                | 1      | 1                | 1      |  |  |

| 1                | 0      | 0                | 1      |  |  |

| 1                | 0      | 1                | 0      |  |  |

| 1                | 1      | 0                | 1      |  |  |

| 1                | 1      | 1                | 1      |  |  |

#### Solution

There are four 1s in the output column and the corresponding binary values are 011, 100, 110, and 111. Convert these binary values to product terms as follows:

$$011 \longrightarrow \overline{A}BC$$

$$100 \longrightarrow A\overline{B}\overline{C}$$

$$110 \longrightarrow AB\overline{C}$$

$$111 \longrightarrow ABC$$

The resulting standard SOP expression for the output *X* is

$$X = \overline{A}BC + A\overline{B}\overline{C} + AB\overline{C} + ABC$$

For the POS expression, the output is 0 for binary values 000, 001, 010, and 101. Convert these binary values to sum terms as follows:

$$000 \longrightarrow A + B + C$$

$$001 \longrightarrow A + B + \overline{C}$$

$$010 \longrightarrow A + \overline{B} + C$$

$$101 \longrightarrow \overline{A} + B + \overline{C}$$

The resulting standard POS expression for the output X is

$$X = (A + B + C)(A + B + \overline{C})(A + \overline{B} + C)(\overline{A} + B + \overline{C})$$

#### **Related Problem**

By substitution of binary values, show that the SOP and the POS expressions derived in this example are equivalent; that is, for any binary value each SOP and POS term should either both be 1 or both be 0, depending on the binary value.

#### **SECTION 4-7 CHECKUP**

- 1. If a certain Boolean expression has a domain of five variables, how many binary values will be in its truth table?

- **2.** In a certain truth table, the output is a 1 for the binary value 0110. Convert this binary value to the corresponding product term using variables *W*, *X*, *Y*, and *Z*.

- **3.** In a certain truth table, the output is a 0 for the binary value 1100. Convert this binary value to the corresponding sum term using variables *W*, *X*, *Y*, and *Z*.

# **4–8** The Karnaugh Map

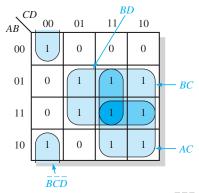

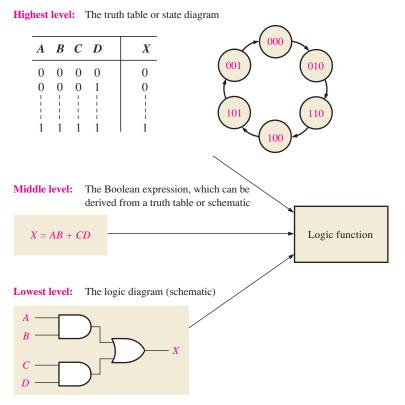

A Karnaugh map provides a systematic method for simplifying Boolean expressions and, if properly used, will produce the simplest SOP or POS expression possible, known as the minimum expression. As you have seen, the effectiveness of algebraic simplification depends on your familiarity with all the laws, rules, and theorems of Boolean algebra and on your ability to apply them. The Karnaugh map, on the other hand, provides a "cookbook" method for simplification. Other simplification techniques include the Quine-McCluskey method and the Espresso algorithm.

After completing this section, you should be able to

- Construct a Karnaugh map for three or four variables

- Determine the binary value of each cell in a Karnaugh map

- Determine the standard product term represented by each cell in a Karnaugh map

- Explain cell adjacency and identify adjacent cells

The purpose of a Karnaugh map is to simplify a Boolean expression.

A **Karnaugh map** is similar to a truth table because it presents all of the possible values of input variables and the resulting output for each value. Instead of being organized into columns and rows like a truth table, the Karnaugh map is an array of **cells** in which each cell represents a binary value of the input variables. The cells are arranged in a way so that simplification of a given expression is simply a matter of properly grouping the cells. Karnaugh maps can be used for expressions with two, three, four, and five variables, but we will discuss only 3-variable and 4-variable situations to illustrate the principles. *A discussion of 5-variable Karnaugh maps is available on the website*.

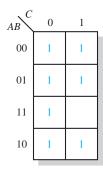

The number of cells in a Karnaugh map, as well as the number of rows in a truth table, is equal to the total number of possible input variable combinations. For three variables, the number of cells is  $2^3 = 8$ . For four variables, the number of cells is  $2^4 = 16$ .

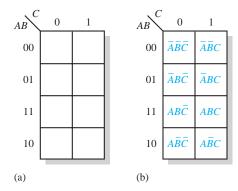

## The 3-Variable Karnaugh Map

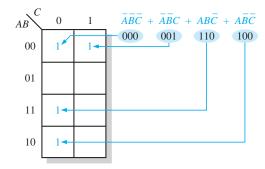

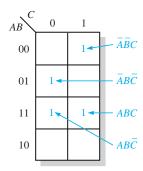

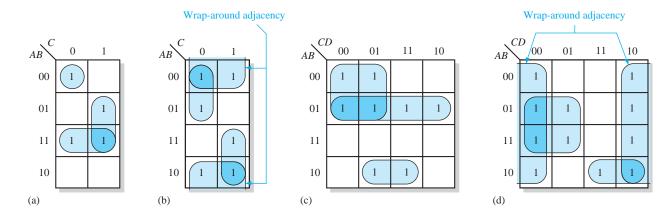

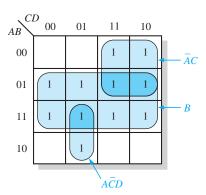

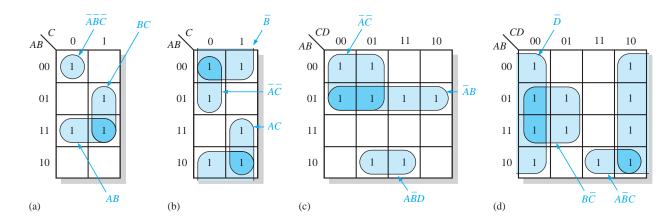

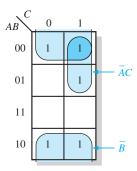

The 3-variable Karnaugh map is an array of eight cells, as shown in Figure 4–25(a). In this case, A, B, and C are used for the variables although other letters could be used. Binary values of A and B are along the left side (notice the sequence) and the values of C are across the top. The value of a given cell is the binary values of A and B at the left in the same row combined with the value of C at the top in the same column. For example, the cell in the upper left corner has a binary value of 000 and the cell in the lower right corner has a binary value of 101. Figure 4–25(b) shows the standard product terms that are represented by each cell in the Karnaugh map.

FIGURE 4-25 A 3-variable Karnaugh map showing Boolean product terms for each cell.

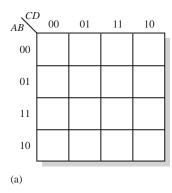

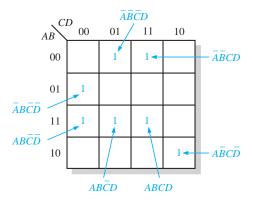

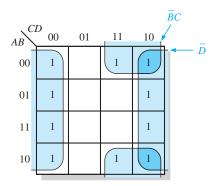

## The 4-Variable Karnaugh Map

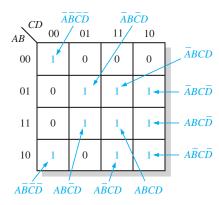

The 4-variable Karnaugh map is an array of sixteen cells, as shown in Figure 4–26(a). Binary values of A and B are along the left side and the values of C and D are across the top. The value of a given cell is the binary values of A and B at the left in the same row combined with the binary values of C and D at the top in the same column. For example, the cell in the upper right corner has a binary value of 0010 and the cell in the lower right corner has a binary value of 1010. Figure 4–26(b) shows the standard product terms that are represented by each cell in the 4-variable Karnaugh map.

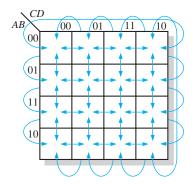

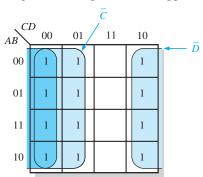

## Cell Adjacency

The cells in a Karnaugh map are arranged so that there is only a single-variable change between adjacent cells. **Adjacency** is defined by a single-variable change. In the 3-variable map the 010 cell is adjacent to the 000 cell, the 011 cell, and the 110 cell. The 010 cell is not adjacent to the 001 cell, the 111 cell, the 100 cell, or the 101 cell.

Physically, each cell is adjacent to the cells that are immediately next to it on any of its four sides. A cell is not adjacent to the cells that diagonally touch any of its corners. Also, the cells in the top row are adjacent to the corresponding cells in the bottom row and

Cells that differ by only one variable are adjacent.

Cells with values that differ by more than one variable are not adjacent.