# Lab Manual Basic Electronics BS(CS)

# IQRA NATIONAL UNIVERSITY PESHAWAR

# CONTENTS

| S. No. | Dated | List of Experiments                                                                                                                                                          | Remarks |

|--------|-------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|

| 1.     |       | To study about the Electrical &Electronic Symbols and Laboratory Equipments like, Multimeter, Oscilloscope, Function Generator.                                              |         |

| 2.     |       | To make a circuit on a wire-o-board & find different currents & voltages                                                                                                     |         |

| 3.     |       | To study the characteristic curve of Silicon & Germanium diodes.                                                                                                             |         |

| 4.     |       | To analyze the half-wave rectifier                                                                                                                                           |         |

| 5.     |       | To analyze the Full-wave rectifier                                                                                                                                           |         |

| 6.     |       | To analyze the Bridge rectifier                                                                                                                                              |         |

| 7.     |       | To study the operations of filters for smooth DC supply.                                                                                                                     |         |

| 8.     |       | To study the operation of Diode Limiters.                                                                                                                                    |         |

| 9.     |       | To study the operation of biased Diode limiters biased                                                                                                                       |         |

| 10.    |       | To study the operation of Diode Clampers.                                                                                                                                    |         |

| 11.    |       | To study the operation of Voltage Doubler                                                                                                                                    |         |

| 12.    |       | To study the characteristic curve of Zener Diode & find the Zener Voltage Vz.                                                                                                |         |

| 13.    |       | To identify the type of transistor (NPN & PNP) & find its mode of<br>operation on different values of Vcc by calculating its base, collector<br>& emitter voltage & currents |         |

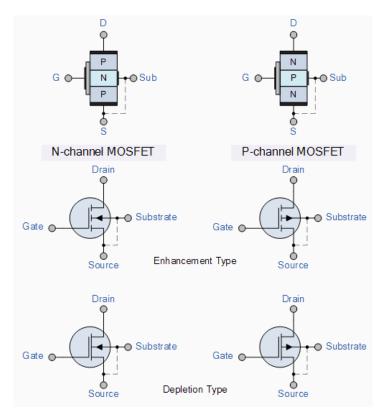

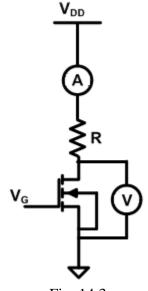

| 14.    |       | To determine source, drain and gate terminals and study the different modes of opertain of an enhancement type n-channel MOSFET.                                             |         |

# Lab Session 01

#### **OBJECTIVE**

To study about the electrical symbols and laboratory equipments like, Multimeter, Oscilloscope, Function Generator, Power Supplies.(<u>http://www.ladyada.net/learn/multimeter</u>)

#### **MULTIMETERS**

The most important debugging tool in any Electronic Lab is a multimeter. A multimeter can measure continuity, resistance, voltage and sometimes even current, capacitance, temperature, etc.

You should go through all of these sections in order, as they build on each other.

- Continuity measurements How to tell if two points are electrically connected

- 2. Resistance measurements How to measure resistance - resistors, potentiometers and sensors

- 3. Voltage measurements How to measure voltage - battery testing, wall adaptor testing, and mixed AC/DC measurements.

#### What is continuity?

Continuity means, are two things electrically connected. So if two electronic parts are connected with a wire, they are continuous. If they are connected with cotton string, they are not: while they are connected, the cotton string is not conductive.

You can always use a resistance-tester (ohmmeter) to figure out if something is connected because the resistance of wires is very small, less than 100 ohms, usually. However, continuity testers usually have a piezo buzzer which beeps. This makes them very useful when you want to poke at a circuit and need to focus on where the probes are instead of staring at the meter display.

#### **Remember!**

#### You can only test continuity when the device you're testing is not powered.

**Always** test to make sure your meter is working before starting the test by brushing the two tips together, and verifying you hear the beep. Maybe the battery is low or its not in the right mode.

Continuity is non-directional, you can switch probes and it will be the same.

If you are testing two points in a circuit and there is a (big) capacitor between those points **you may hear a quick beep and then quiet**. That's because the voltage the meter is applying to the

circuit is charging up the capacitor and during that time the meter 'thinks' its continuous (essentially)

**Small resistors (under 100 ohms or so) and also all inductors will seem like short circuits** to a multimeter because they are very much like wires.

**Likewise, continuity doesn't mean ''short''** it just means very very low resistance. For example, if you have a circuit that draws an Amp from a 5V supply, it will appear to be a 5 resistor. If you measure that with your meter it will think its a short circuit, but really its just a high-drain circuit.

### Lab Procedure

First step is to get your multimeter into the correct mode. Look for the icon that looks sort of like a 'sound wave'.

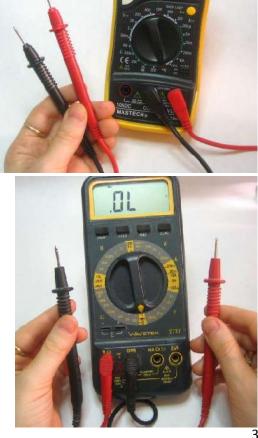

Here are examples. Turn the multimeter knob so that it points to this symbol

#### **Example 1**

This meter is very simple. When the probes are not touching, the display shows "1".

When you touch the tips together, the display changes to a three digit mode (it's displaying resistance, which we will cover later) It also emits a beep.

# ->+•)))•

#### Example 2

This meter is dual-mode but still very easy to use. Turn the dial to the symbol. When the probes are not touching the display shows "OL" which stands for Open Loop. (Open loop is another way of saying there is no continuity)

When you touch the probes, the sound wave icon shows up in the display (upper right) and it also shows a number. The number is not the resistance, actually...it is the voltage (look for the V in the right hand side for Volts). This is because this mode is also a **Diode Test** (which will be discussed later)

#### What is resistance?

Resistance is just what it sounds like, it is the characteristic that makes a component fight current flow. The bigger the resistance value (in **ohms** )

the more it fights. Most resistors you'll see range between 1 ohm and 1 mega ohm (1.0 M) they often have 5% tolerance but you can buy 1% or even 0.1% accuracy resistors.

In general, resistance testing is best for measuring resistors, but you may find yourself measuring the resistance of other things, such as sensors and speakers.

#### **Resistor coding**

Resistors are color coded, at first it seems like a bad way to print the values but with a little time it becomes faster because you dont have to read any numbers and the stripes are visible no matter how it is rotated.

This image shows a 1.0  $k\Omega$  5% resistor (brown black red gold)

#### **Remember!**

**You can only test resistance when the device you're testing is not powered**. Resistance testing works by poking a little voltage into the circuit and seeing how much current flow, it is perfectly safe for any component but if it is powered there is already voltage in the circuit, and you will get incorrect readings

**You can only test a resistor before it has been soldered/inserted into a circuit**. If you measure it in the circuit you will also be measuring everything connected to it. In some instances this is OK but I would say that in the vast majority it is not. If you try, you will get incorrect readings and that's worse than no reading at all.

Resistance is non-directional, you can switch probes and the reading will be the same.

If you have a ranging meter (as most inexpensive ones are), you'll need to keep track of what range you are in. Otherwise, you will get strange readings, like **OL** or similar, or you may think you're in K $\Omega$  when really you're in M $\Omega$ . This is a big problem for beginners so be careful!

# Lab Procedure

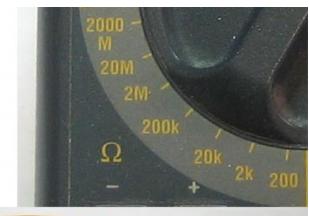

Look for an ohm ( ) symbol, if its a ranging meter there will be a bunch of subdivided modes. If its auto-ranging there will be only one.

This meter has the symbol and then 7 submodes, ranging from 200 to 2000M .

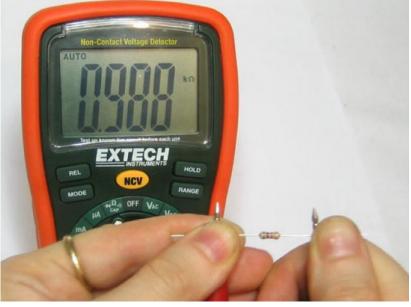

# **Example1.** Testing a resistor

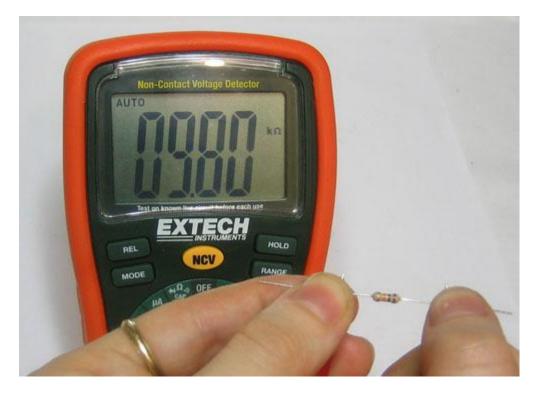

With an auto-ranging meter, just put the two probes across the resistor and read the number. For example, this 1K 5% resistor is actually

0.988 K ohm.

And this 10K is really 9.80K . Note that the numbers look similar but the decimal point has moved.

This ranged meter requires that you dial in the range. We'll guess that this resistor is under 2K then measure it. We get 0.992 which means its 0.992 K (or, a 1K resistor)

Now testing a different resistor, we will again guess its under 2K. However, this time we get a strange response, a **1**.which means out of range. Some meters will display an **OL** which you may remember from the continuity section as meaning "open loop" here it means "the measurement is higher than the range"

We try again, changing the range to 20K .

It is a 9.82 K resistor (10K)

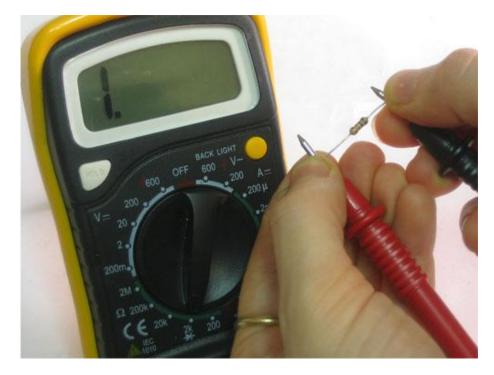

# **Example 2. Testing a potentiometer**

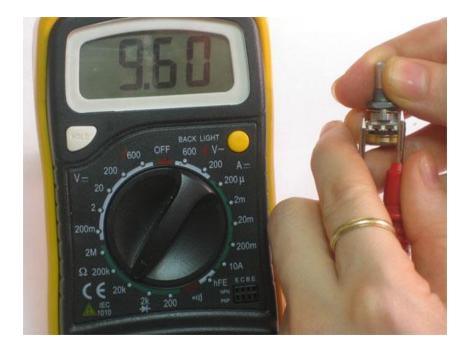

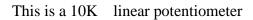

You can test the max-value of a potentiometer by measuring across the two 'ends' as shown here with a rotational 10K pot. To find the 'range' look at the dial.

You can also use a multimeter to tell whether the potentiometer is a linear or logarithmic (audio) pot. When the pot is centered, if the resistance between the wiper and one end is half of the total value, its linear.

The minimum resistance of the pot, 0 (a short) as expected

Potentiometer centered, about 5K

Maximum value is 9.5K (it should be around 10K )

# **Example 3. Testing a sensor**

Potentiometers are resistors that change value when they are moved. A Light Dependent Resistor (LDR) is a resistor that changes value with the amount of light it receives. This one has a range of about 20K max.

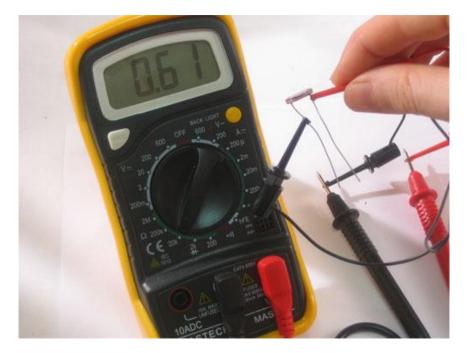

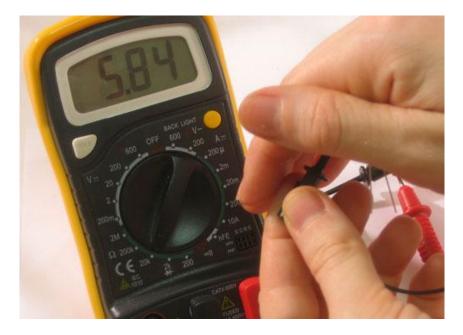

First, set the range, in this case 20K seems pretty good. In bright light, it measures about 610

Slightly shaded it's 5.84K (remember this is still a well-lit photo)

# What is voltage?

Voltage is used to provide power (via a battery or wall plug) and its also used as a way of transmitting data. For example, music is recorded from a microphone as an analog voltage

signal, if that voltage waveform is applied to a speaker the voltage performs the work of making air move and produces sound.

# AC/DC

**Direct current voltage is what comes out of batteries**. The battery is at 9V, and it pretty much keeps that voltage constant, until it dies. The chemical reactions inside the battery create DC voltage. Most of the Electronic circuits work on DC voltage.

Alternating current voltage is what comes out of the wall socket. The generator at the US power plant creates a voltage that oscillates, going from -120V to 0 to +120V to 0 again, 60 times a second. At the European power plant its -240V to +240V at 50 times a second. (Note that those voltages are 'RMS' - Root Mean Square - which means that the peak voltage is actually about 1.4x higher, but since multimeters show RMS voltages, its easier to just use those) AC voltage is great for power plants because its easy to transform AC voltages (using a transformer) up to 50KV for long distance travel and then down to 240V or 120V to safely power your home. Batteries only supply DC voltage and wall plugs only supply AC voltage. However, it is totally possible to have **both**AC and DC voltage at a certain point: If an AC voltage is oscillating between -60V and +60V it has 120V AC and 0V DC because the **average** voltage of -60V and +60V is 0V.

If an AC voltage is oscilating between 0V and 120V then it has 120V AC and 60V DC because the average voltage of 0V and 120V is 60V.

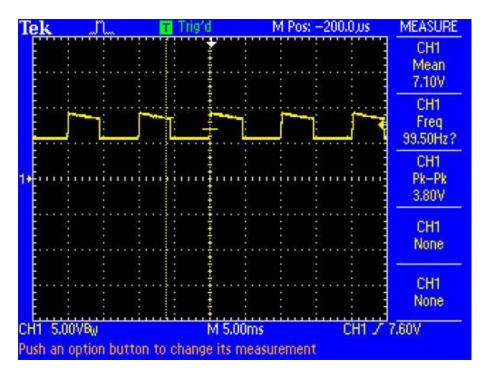

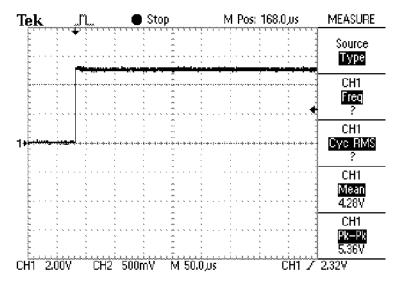

In the above oscilloscope image, the dashed horizontal line in the center is ground (0V) and each dashed division is 5V. The scope is displaying a signal that has both AC and DC components.

There is an alternating voltage (a square wave) that is about 4V high at about 100Hz and a DC (mean average) voltage that is around 7V. Use the dashed divisions to verify for yourself that this is so.

# **Remember!**

**You can only test voltage when the circuit is powered** If there is no voltage coming in (power supply) then there will be no voltage in the circuit to test! It must be plugged in (even if it doesn't seem to be working)

**Voltage is always measured between two points** There is no way to measure voltage with only one probe, it is like trying to check continuity with only one probe. You must have two probes in the circuit. If you are told to **test at a point** or **read the voltage at this or that location** what it really means is that you should put the negative (reference, ground, black) probe at **ground** (which you must determine by a schematic or somewhere else in the instructions) and the positive (red) probe at the point you would like to measure.

**Voltage is directional** If you measure a battery with the red/positive probe on the black/negative contact and the black probe on the positive contact you will read a negative voltage. If you are reading a negative voltage in your circuit and you're nearly positive that this cannot be, then make sure you are putting the black probe on the reference voltage (usually ground)

**DC voltage and AC voltage are very different** Make sure you are testing the right kind of voltage. This may require pressing a mode button or changing the dial.

**Multimeters have different input impedances that affect readings of high impedance circuits** For example, measuring a sensor that has 1M ohm impedance with a 1 M ohm impedance meter will give you only half the correct reading

# Lab Procedure

There are often two separate modes for AC and DC voltage. Both will have a V but one will have two lines, one dashed and one solid (DC) and one with have a wave next to it (AC).

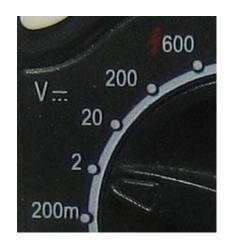

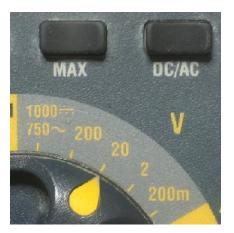

This meter has the double line for DC voltage, and 5 ranges, from 200mV to 600V.

This ranged meter has 5 ranges, the top range is 750 VAC or 1000 VDC, to switch between DC and AC you need to press the DC/AC button on the upper right.

When the probes are not connected to anything, they should display 0V. They might flicker a bit if they pick up ambient voltage (your home is a big radiator of 60Hz voltage which can couple into your meter probes).

# **Example 1: Testing batteries**

Testing batteries is a super useful skill and is one of the best ways to practice with your multimeter. The first battery we'll test is a new 1.5V alkaline. This one is a AAA but a AA, C or D cell will be the same voltage. Set the range to **2V DC**.

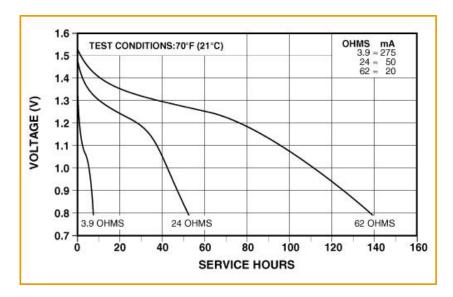

We read 1.588V, which you may think is a mistake, after all its a 1.5V battery so shouldn't it be 1.5V? Not quite, the 1.5V written on the side is just a **nominal voltage**, or the "average" you may expect from the battery. In reality, an alkaline battery starts out higher, and then slowly drifts down to 1.3V and then finally to 1.0V and even lower.

Using this graph you can easy tell how fresh your battery is and how long you can expect it to last.

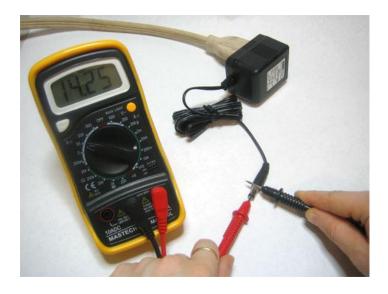

# Example 2: Testing wall wart (adapter) plugs

Testing wall adapters is also very handy, especially when you build your own circuits.

The first kind we will test is a **transformer-based** adapter.

Note that the label says **Transformer**, it is also blocky and heavy which indicates a transformer as well. It requires 120VAC input, US power only. The nominal output is 9VDC at 300mA. The polarity symbol shows that the middle is positive, the outside is negative, thus we place the

ground (black) probe on the outside and the positive (red) probe on the inside.

14V? That's not anything like the 9V on the package, is this a broken wall wart? Turns out, its totally normal. Transformer-based wall adaptors are (almost always) **unregulated**, which means that the output is not guaranteed to be a particular value, only that it will be **at least** what is printed on the box. For example, with this adapter it means that when drawing 300mA, the voltage is guaranteed to be higher than 9V.

Since the output is unregulated, the voltage supplied will drop as more current is pulled from it, which means that open-circuit (connected to nothing) the measured output can be as high as 14V.

# **Example 3: Testing Wall output**

This is the 'easiest' test, just shove the two probes into a wall socket.

About 220V, as expected

#### Post Lab

- 1. Plot a graph between your mobile battery voltage & Hours.

- 2. Calculate the voltage regulation of your cell phone charger.

- 3. From website check the data sheets of IC's present on any motherboard &find how much voltages are required by your PC processor, motherboard, hard disk, Ram memory & LAN card.

- 4. AC voltages are alternating voltages, but when measuring AC voltages why don't the reading keeps on varying with the variation in AC voltage?

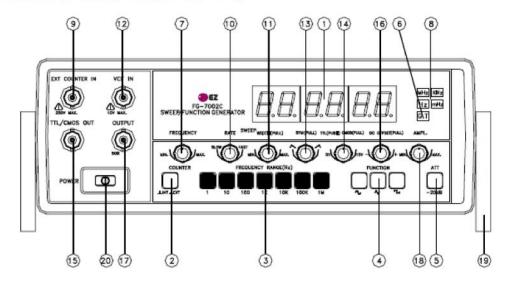

#### 3. OPERATION

3-1. Controls, indicators and connectors

FIG 1. FRONT PANEL OPERATOR'S CONTROLS

| ① LED DISPLAY.                                                | Displays Internal Or External                                             |  |  |  |  |

|---------------------------------------------------------------|---------------------------------------------------------------------------|--|--|--|--|

|                                                               | Frequency.                                                                |  |  |  |  |

| ② INTERNAL/EXTERNAL SWITCH.                                   | PUSH IN : External Frequency                                              |  |  |  |  |

|                                                               | Counter.                                                                  |  |  |  |  |

|                                                               | PUSH OUT: Internal Frequency                                              |  |  |  |  |

|                                                               | Counter.                                                                  |  |  |  |  |

| ③ RANGE SWITCHES.                                             | Frequency Range Selector.                                                 |  |  |  |  |

| <b>©</b> FUNCTION SWITCHES.                                   | Select Sine wave, Triangle Wave Or                                        |  |  |  |  |

| @                                                             | Square Wave Output.                                                       |  |  |  |  |

| S ATTENUATOR.                                                 | Selects Output Level By -20 dB.                                           |  |  |  |  |

| ⑥ GATE TIME INDICATOR.                                        | Gate Time Is Selected Automatically E                                     |  |  |  |  |

|                                                               | Input Signal.                                                             |  |  |  |  |

| ⑦ FREQUENCY DIAL.                                             | Controls Output Frequency In Selecter                                     |  |  |  |  |

|                                                               | Range.                                                                    |  |  |  |  |

| ⑧ MHz, KHz , Hz, mHz INDICATOR. ⑨ EXTERNAL COUNTER INPUT BNC. | Indicates Unit Of Frequency.<br>Used As An External Frequency<br>Counter. |  |  |  |  |

| 1 SWEEP WIDTH CONTROL.              | Pullout And Adjusts Magnitude Of                     |

|-------------------------------------|------------------------------------------------------|

|                                     | Sweep.                                               |

| 1 VCF INPUT BNC.                    | Voltage Controlled Frequency Input                   |

|                                     | Permits External Sweep.                              |

|                                     | Frequency Control Sweep Rate Control                 |

|                                     | Should Be Off When Applying External                 |

|                                     | Voltage At This BNC.                                 |

| ③ SYMMETRY CONTROL.                 | Adjust Symmetry Of Output                            |

|                                     | Waveform 1:1 to 10:1 With Push/Pull                  |

|                                     | Switch On.                                           |

| <sup>(I)</sup> TTL/CMOS CONTROL.    | Selects TTL Or CMOS Mode                             |

|                                     | Pull-out : CMOS Level Control, Push-                 |

|                                     | In: TTL Level.                                       |

| <sup>(5)</sup> TTL/CMOS OUTPUT BNC. | TTL/CMOS Level Output.                               |

| <sup>16</sup> DC OFFSET CONTROLS.   | Adds Positive Or Negative DC                         |

|                                     | Component To Output Signal.                          |

| 1 MAIN OUTPUT BNC.                  | Impedance 50 Ohm.                                    |

| ③ AMPLITUDE CONTROL.                | Adjusts Output Level From 0 TO 20 dB.                |

| 19 TILT STAND.                      | Pull Out To Adjust Tilt.                             |

| POWER SWITCH.                       | Push type switch. turning on the power when pressed. |

# Oscilloscopes

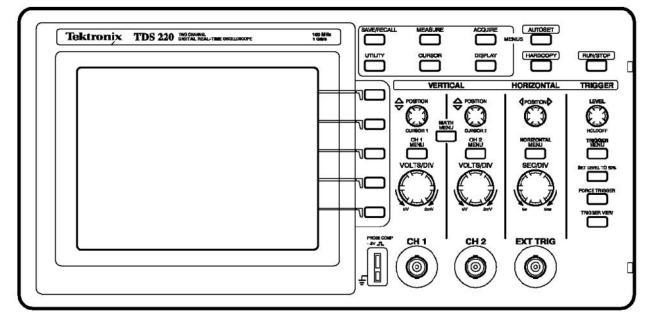

The next drawing shows the front of a TDS 220 oscilloscope.

# Lab procedure 1 - Getting Started

This lesson teaches you how to turn on the oscilloscope and display a simple signal. To perform the Getting Started lesson, follow these steps:

1. Plug in the oscilloscope and apply power by pressing the POWER button on the top of the case.

Notice that when you apply power, the oscilloscope immediately performs a self-test. 2. Wait until the display shows that all self tests passed and press the SAVE/RECALL front-panel button (top left).

The SAVE/REC menu displays on the right of the screen. The top right bezel button toggles between two menus: Setups and Waveforms.

3. Be sure that Setups is highlighted (in inverse video) and press the button beside "Recall Factory."

The oscilloscope recalls the default factory settings to initialize the instrument to a known state, which eliminates any nasty surprises. If at any time you do not understand what the oscilloscope is displaying, you can repeat this step.

The box at the end of this lesson also gives some suggestions for getting out of odd screen modes without resetting everything.

The display that dominates the left side of the scope is a digital LCD screen. This means that displayed signals have visible pixel "jaggies." If you have used an analog scope, you will notice that the signals, especially sine waves, do not look as smooth and continuous on this screen. The digital display does, however, have some significant advantages, as you will discover. Some of the information around the edges of the display will be explained as we go along; the rest can be looked up in the Tektronix manuals. The large area down the right side of the screen is the menu. A large number of menus are available and are called up by pressing various buttons on the control panel. The buttons immediately to the right of the screen correspond to the menu items; their functions change depending on the menu displayed.

Take a close look at the probes that are provided with the scope. These are important to the performance of the oscilloscope and should be handled with care. The sprung hook tip is removable, revealing a point that can be used in tight locations. The short wire that terminates in an alligator clip is the ground connection. If both probes are connected to the scope, disconnect one of them by turning the connector to the left and pulling it straight toward you.

Take a look at the connector and note that it is not quite like a regular BNC connector, on which the shell will rotate continuously. This connector only turns through a small arc and must be in the left, or unlocked, position, before being pushed onto the oscilloscope

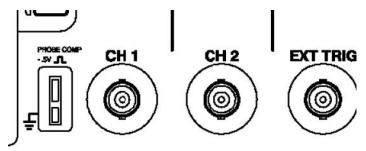

input. Do this now and turn the connector to the right to lock it. Now we will get a signal onto the display. Note that the first two BNC type connectors at the bottom edge of the front of

the scope are labelled CH 1 (for channel 1) and CH 2.

Usually you will connect the probes here, but you can also

use a coaxial cable with a BNC connector to connect the

scope to a function generator or other signal source. Immediately to the left of the inputs is a pair of small metal tabs labelled PROBE COMP for probe compensation. This is an internal source of a square wave at about 5 volts magnitude and 1KHz, used to adjust the internal compensation of the probe.

4. Connect the probe on channel 1 of the scope to the top tab, and the ground clip of the probe to the bottom tab.

5. Press the AUTOSET button near the top right corner on the front-panel.

The oscilloscope sets the vertical, horizontal, and trigger controls automatically which usually results in a usable display. These settings are adequate in this and many other situations. Be aware that the oscilloscope also sets a number of background functions that might be not be desirable in some circumstances.

Depending on how the oscilloscope was being used when it was last turned off, you may see one or more channels displayed. The trace labels on the left edge of the screen correspond to the channel numbers on the front of the oscilloscope.

6. If only one channel appears, press the CH 2 MENU front-panel button to display channel 2, and then press AUTOSET again.

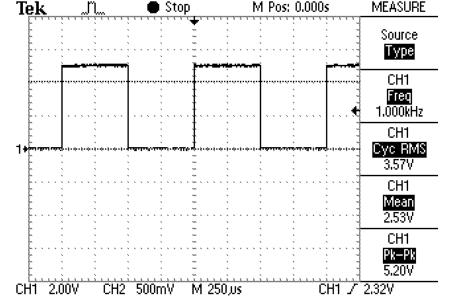

Now both channels display even though there is nothing but noise on channel two. The upper trace should show a steady square wave as depicted below. The wave is stationary on the screen because AUTOSET has set the oscilloscope's trigger to channel 1 and the trigger circuit causes successive similar waveforms to be superimposed on the screen. For a complete discussion of trigger see the Tektronix manual.

If the top and bottom of the square waves are not straight, your probe needs to be compensated, but you do not need to do it right now.

|                          | Tę | <u>k</u>              | "n               |      | T                               | Trig'd                                |           | M           | l Pos: | 0.000            | 5           | MEASURE   |

|--------------------------|----|-----------------------|------------------|------|---------------------------------|---------------------------------------|-----------|-------------|--------|------------------|-------------|-----------|

|                          |    | · · · · ·             |                  |      |                                 | •                                     | •••••     |             |        |                  |             | Source    |

| To demonstrate           |    |                       |                  |      |                                 | <b>.</b>                              |           |             |        | • • • • • •      |             | Туре      |

| the downside of          |    | ~<br>~                |                  |      | 1                               | ĺ                                     | L L       |             |        | 1                | d           |           |

| using Autoset,           | 1+ |                       |                  |      |                                 | ار<br>مستقدمات                        |           |             |        |                  |             | CH1       |

| follow these             |    | ~<br>~                | · ·              |      |                                 |                                       |           |             |        |                  | · · ·       | Pk—Pk     |

| steps:                   |    |                       |                  |      |                                 |                                       |           |             |        |                  |             | 5.40V     |

| a) Disconnect            |    | ~                     | · · ·            |      |                                 | · · · · · · · · · · · · · · · · · · · |           |             |        |                  | · •         | CH1       |

| the channel 1            |    |                       | *•••••••••       |      | ,<br>,<br>,<br>,<br>,<br>,<br>, |                                       |           | ••••••••••• |        |                  | ••••••••    | Freq      |

| probe from               |    | ~                     | • •              |      |                                 | · · · · · ·                           |           |             |        | •                |             | 1.000kHz? |

| PROBE COMP,              |    | <br><br>              | · · · · ·        |      |                                 | · · · · · · · · · · · · · · · · · · · |           |             |        |                  |             |           |

| and connect<br>channel 2 |    | n<br>n                |                  |      |                                 |                                       |           |             |        |                  |             | CH2       |

| instead.                 | 2+ | ~<br>~                |                  |      |                                 |                                       |           |             |        |                  |             | None      |

| Press                    |    | · ·                   | · ·              |      |                                 |                                       |           |             |        |                  |             |           |

| AUTOSET.                 |    | ~<br>~<br>~ ~ ~ ~ ~ ~ | 、<br>、 、 、 、 、 、 | <br> | · · · · ·                       | · · · · · · · · · · · · · · · · · · · | · · · · · | <br>        |        | •<br>• • • • • • | · · · · · · | CH2       |

| The wave is no           |    | ~                     | · ·              |      |                                 |                                       |           |             |        |                  | ,           | None      |

| longer                   |    |                       | `<br>            |      |                                 |                                       |           |             |        | `<br>            | `           |           |

| stationary               | СН | 1 5.0                 | 70V              | CH2  | 500n                            | nV N                                  | 4 500     | JUS         |        | С                | H1 /        | 2.34V     |

because there is no signal on channel 1 to trigger the oscilloscope, which is now free-running. b) Press the TRIGGER MENU button (near the right edge of the scope). The third menu item is the trigger source, which is currently set to CH1.

c) Press the button beside this menu item once to switch the source to CH2. The display should become stable.

d) Now press AUTOSET again. Once again the scope is free running because Autoset sets the trigger source to the lowest displayed channel. This is just one of many settings that Autoset changes – see the Tektronix manual for the complete list, and use Autoset wisely.

e) Before proceeding, switch the probe compensation waveform back to channel 1. Now let us get rid of the useless channel 2 display and expand the channel 1 presentation.

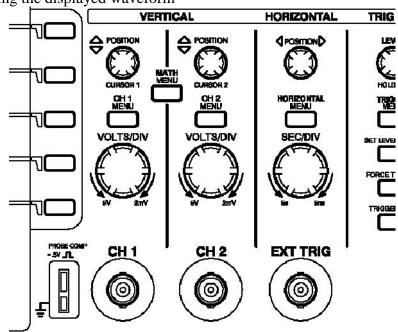

7. Press the CH 2 MENU front-panel button to remove the channel 2 waveform from the display. If that channel's menu is not already displayed, the first push of the button displays the menu (the top right corner of the screen will say CH1 or CH2). A second push turns off the channel. Do this and you should see that the channel 2 trace disappears. Now look at the channel 1 control area. In addition to the CH 1 MENU front-panel button, there are two knobs. The top one controls the vertical position.

8. Turn the POSITION knob to bring the displayed waveform

down to the middle of the screen. Note that as soon as you start turning the knob, a line of text appears in the bottom left corner of the screen. This is telling you how far the zero level of this channel is from the vertical center of the screen. There are several reasons why you might want the display exactly centered, and this helps you to do that.

Once you have the trace centered you can expand it for a better view. The bottom knob of the channel, or vertical, controls is the volts per division range control. Turning the

VOLTS/DIV knob to the right increases the sensitivity (decreases the volts per division, and expands the display vertically). One division is the distance between the grid lines on the screen, a bit less than one centimeter apart. Just to the right, on the other side of the channel 2 controls, is a similar knob labelled SEC/DIV that controls the time base resolution. Turning it to the right reduces the time per division and expands the display horizontally.

**Quick fixes for display problems**. These relate to features that we will stud y later but may be just getting in your way right now.

My display is very dark or has very low contrast.

Press the DISPLAY button. The bottom two buttons at the right edge of the screen are

now labelled "Contrast Increase" and "Contrast Decrease." These actually lower and raise, respectively, the brightness of the white part of the screen. As soon as you press one of them the "contrast" level appears at the bottom right corner. Set it to 50%. There are a pair of extra vertical or horizontal lines cluttering up my display.

Press the CURSOR button. The top button at the right of the screen is now labelled

"Type" and will have either "Voltage" or "Time" below it. Press it until it says "Off". There is an "A" and/or a "B" (with or without an associated trace) at the left edge of the screen.

Press the SAVE/RECALL button. Use the third screen button to select "Ref A" or "Ref B" if necessary, then press bottom button to turn it off.

#### Lab Procedure 2 – Measurements

In general, you will use an oscilloscope to measure characteristics of a signal, such as magnitude or period of oscillation. You can look at the signal in relation to the screen grid or graticule to estimate the values of these characteristics, which was about one could do with early oscilloscopes. Modern oscilloscopes have much more powerful measurement capabilities. In this lesson, you will learn about the following topics:

- How to use the Measure menu to define the source and type of measurement to take

- How to set the Probe menu item to match the probe in use

- The difference between measuring a signal and a displayed waveform

Lesson 2 begins where lesson 1 ended. If the oscilloscope has been turned off or the settings changed since lesson 1, you need to quickly redo lesson 1 to get back the centered square waveform that fills most of the screen with two or three full cycles displayed.

To perform the Measurements lesson, follow these steps:

1) Press the MEASURE front-panel button.

The word "MEASURE" appears above the menu area, Type is the active menu, CH1 is the source for four measurements and no measurements are selected (NONE).

The Measure menu is a Page Selection type of menu. The top menu displays two menu names: Source and Type. The active menu is highlighted in inverse video - white letters in a black box. When Source is highlighted, you can press each of the other four bezel buttons to switch between CH1 and CH2 as the measurement source. When Type is highlighted, you can press each of the other four buttons to select the type of measurement to take from the selected source.

2) Press the second button until Freq appears. A question mark appears momentarily until the oscilloscope measures the frequency of the signal connected to CH1.

3) Press the third button until Period appears. The oscilloscope displays the period of the signal (1/f).

4) Press the fourth button until Mean appears. The oscilloscope displays the mean voltage.

5) Press the fifth button until Pk-Pk appears. The oscilloscope displays the peak-to-peak voltage.

6) Press the third button until Cyc RMS appears. The oscilloscope displays the true RMS value of one cycle of the waveform.

The Freq, Period, Mean, Pk-Pk, and Cyc RMS measurements are always available. If you have a TDS2MM module in your oscilloscope, then there are some other measurements available that we will not cover here, such as rise time.

The next drawing shows how the oscilloscope display should now look. There may be

signal.

If the peak-to-peak voltage is not close to 5 volts, in particular if it is around 0.5 or 50 volts, the probe setting of the oscilloscope is incorrect. The oscilloscope displays voltage values based on the probes. The probes improve the performance of the oscilloscope by increasing the effective input impedance from 1 Megohm to 10 Megohms, thus reducing the loading effect that the oscilloscope has on the circuit. In doing so, the probe reduces the input signal by a factor of ten. For example, if a three volt signal is present at the probe tip, 0.3 volts appears at the oscilloscope input channel connector.

The oscilloscope compensates for this attenuation when it takes voltage measurements. Since the oscilloscope cannot detect which type of probe is connected to any input channel, you have to tell the oscilloscope through a channel menu selection.

The most common probe attenuates the signal 10 times and is called a 10X probe. The oscilloscope includes 10X probes although you can also use 100X and 1000X probes. 7) Press the appropriate channel menu front-panel button, such as CH 1 MENU.

The Probe menu item appears beside the fourth bezel button – successive presses of the button rotate through 1X, 10X, 100X and 1000X. As you press this button, watch the bottom left corner of the display – the number that is changing is the volts per division. If the readings seem wildly high or low when taking voltage measurements, check that the Probe menu setting matches the probe connected between the oscilloscope and the circuit. If you are using a straight coax cable connection, set the Probe menu to 1X. 8) Press the MEASURE front-panel button.

We will now discover one of the most important things to remember when using the oscilloscope to take measurements from signals displayed as waveforms. To do this, we need to understand how the oscilloscope displays signals.

Notice that there is a small arrow at the top of the display and another at the right side, both pointing inwards. The one at the top shows the time of the trigger event, and the one at the right shows the trigger voltage. Because this is a storage oscilloscope, it can display the waveform before the trigger event, and the default horizontal position for the trigger is the centre of the screen. If the arrow at the top of the display, the trigger time, is not at the centre, use the Horizontal POSITION knob to move it to the centre. Read the mean voltage. The value should be approximately half the peak voltage; it may actually be a bit less because the peak voltage includes any overshoot – something to remember for the future when interpreting peak-to-peak values. Now we are going to

deliberately cause an erroneous reading.

9) Turn the Horizontal SEC/DIV knob

(time base control) until the time per division reads M 50.0  $\mu$ s. The oscilloscope no longer displays values for frequency or RMS voltage because there is not a full cycle to measure on the screen, but the mean voltage has not significantly changed. 10) Turn the Horizontal POSITION knob to move the waveform to the left, while reading the mean voltage.

The mean value steadily increases,

reaching close to the peak voltage when the trigger point is at the left side of the screen. The mean value of the signal has not actually changed – what has changed is the mean value of the part of the waveform that is displayed, which is the point of this exercise. The measurement functions of this oscilloscope (and digital scopes in general) operate on the displayed waveform, not on the input signal, and must be interpreted with care.

#### Using the Display Menu

To understand various functions of the Display menu, follow these steps:

1) Press the DISPLAY front-panel button.

The top menu item is Type, which switches between dots and vectors, and with this particular set of waveforms yo u will not see a noticeable difference. When displaying square waves or other waveforms that have rapid vertical excursions, the vectors setting draws in the vertical lines to make the waveform easier to recognize.

2) Press the Format bezel button and select XY.

You should see an ellipse on the screen – we are now displaying channel 1 as the X axis versus channel 2 on the Y axis.

3) To make the ellipse more solid, go back to the Persist bezel button and set it to 2 Sec. Note that the ellipse fills in because the oscilloscope is now keeping two seconds of history on the screen. The bottom two buttons are labelled Contrast Increase and Contrast Decrease but they actually lower and raise, respectively, the screen brightness. If the screen is too dark you actually need to press the Contrast Decrease button to raise the contrast.

#### POST LAB

- 1. Using function generator & oscilloscope, generate & observe following waveforms. Also note down all parameters in following chart:

- a) A pulse train with 50% duty cycle.

- b) A waveform similar to the supply which comes in our wall socket.

- c) A triangular wave with 50% duty cycle.

|                | Peak to Peak | RMS Value | Frequency | Average Value |

|----------------|--------------|-----------|-----------|---------------|

|                | Value        |           |           |               |

| a) Pulse Train |              |           |           |               |

| b) Wall Supply |              |           |           |               |

| c) Triangular  |              |           |           |               |

#### TASK:

1. Find & list the application where different types of waveforms are used.

# Lab Session 02

#### **OBJECTIVE**

To make a circuit on a bread-board & find different currents & voltages

#### PRE – LAB

#### Procedure

#### Simulation

Simulate the circuit using multisim and check whether the output is amplified version of input or not?

#### Wiring the circuit

How to construct a circuit on veroboard by reading the schematic. If you're an experienced constructor, then you will just look at the schematic and start assembly. Experience tells you where to place components and use veroboard space to its best advantage. If you are a beginner, certain prerequisites are assumed. You need to be able to read the circuit diagram and relate to each component on the diagram, as it is wired onto the veroboard. You also need to be able to solder, and beware of the position and orientation of the board and components when working on it from the reverse side.

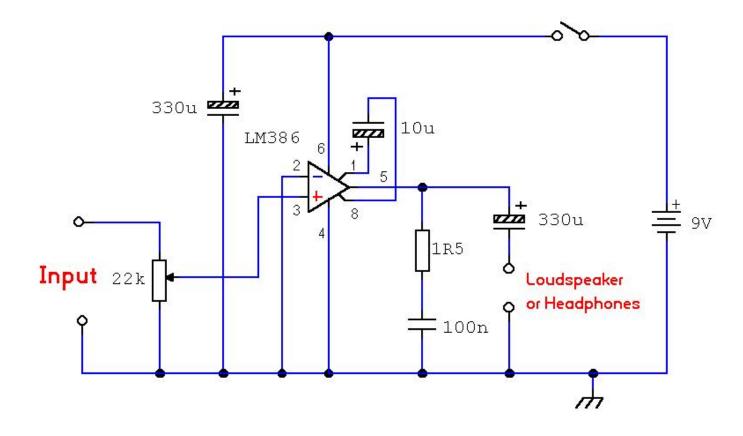

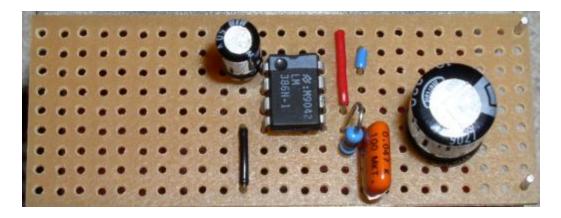

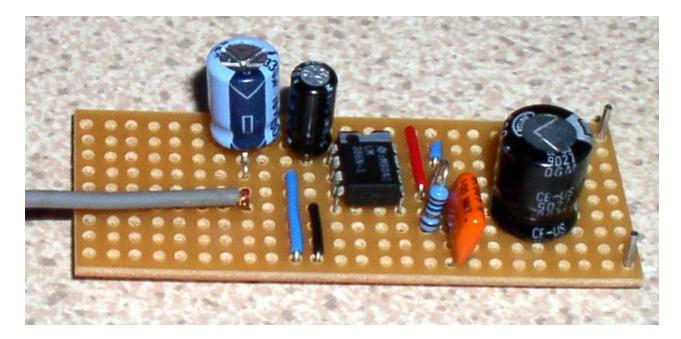

Notes: The circuit is based on the National Semiconductor LM386 amplifier. In the diagram above, the LM386 forms a complete non-inverting amplifier with voltage gain of x200.

A datasheet in PDF format can be downloaded from the National Semiconductor website. The IC is available in an 8 pin DIL package and several versions are available; the LM386N-1 which has 325mW output into an 8 ohm load, the Lm386N-3 which has 700mW output and the LM386N-4 which offers 1000mW output. all versions work in this circuit.

The gain of the Lm386 can be controlled by the capacitor across pins 1 and 8. With the 10u cap shown above, voltage gain is 200, omitting this capacitor and the gain of the amplifier is 20.

The IC works from 4 to 12Volts DC, 12Volt being the maximum recommended value. The internal input impedance of the amplifier is 50K, this is shunted with a 22k log potentiometer so input impedance in this circuit will be lower at about 15k. The input is DC coupled so care must be taken not to amplify any DC from the preceeding circuit, otherwise the loudspeaker may be damaged. A coupling capacitor may included in series with the 22k control to prevent this from happening.. The schematic is shown below:

Below is the suggested parts list:

- 1 22k potentiometer (log)

- 1 1R5 ohm resistor 5% tolerance

- 1 10u 25WV electrolytic capacitor

- 2 330u 25WV electrolytic capacitors

- 1 100n ceramic capacitor 100V ( these small capacitors are usually rated 100 or 2220 or 400V)

- 1 LM386 linear integrated circuit

- 1 8 Pin DIL socket (optional)

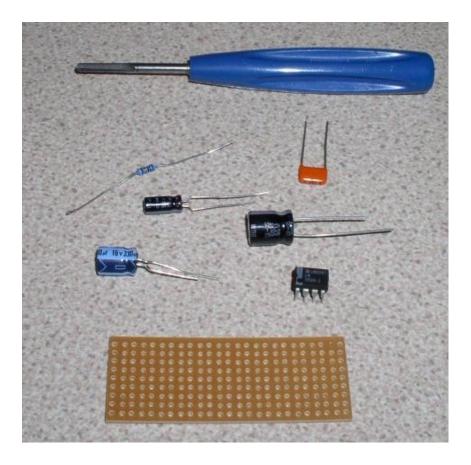

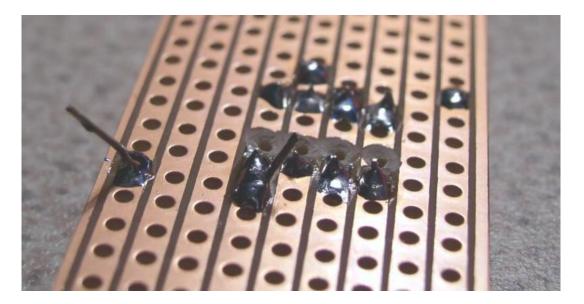

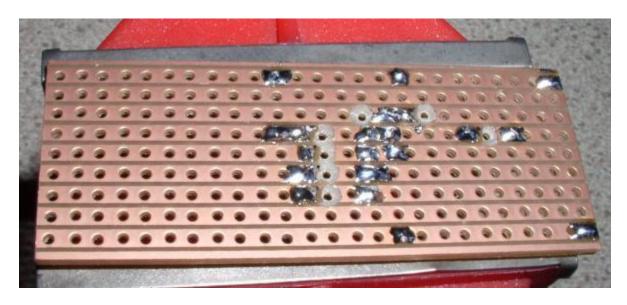

Step 1:

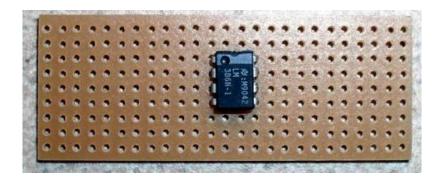

First the components are collected and laid out. The blue item is a veroboard track cutter (Optional).

#### Step 2

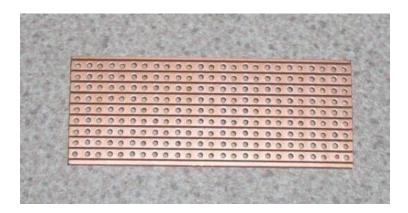

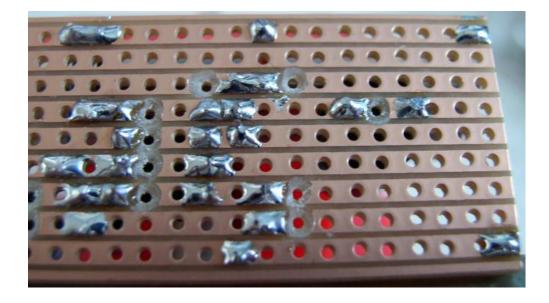

A suitable piece of veroboard is used. This must be large enough to hold all the components of the circuit. They are available in standard sizes, the piece below is 9 holes wide by 25 holes long and approximate dimesions 1 by 2.5 inches. Each of the horizontal 9 strips is known as a "track". A track is the same as a single wire running from opposite ends of the board.

If a track is broken, with a veroboard cutter, then you have two non-connected wires on the same horizontal strip. Note that NO continuity exists across adjacent tracks. If this should happen, i.e. when cutting a track and a piece of copper "swarf" should accidentally bridge two tracks, then

the design would be compromised and probably not work at all. Therefore take care when breaking tracks and examine the board after making each break.

#### Step 3

Check that the veroboard is large enough. Loosely push all components through the holes (in any order). Leave at least a space of 2 holes between components. This will allow room for wiring

and track breaks.

#### Step 4

Work begins! You do need to know how to read a schematic. The lines represent wires, the symbols are the components.

To help identify components, these are listed here. Look at the schematic. The triangle represents the LM386. As 7 connections are used it makes sense to place the IC somewhere central, (see above picture), as tracks above and below the IC will act as the wires for the power supply.

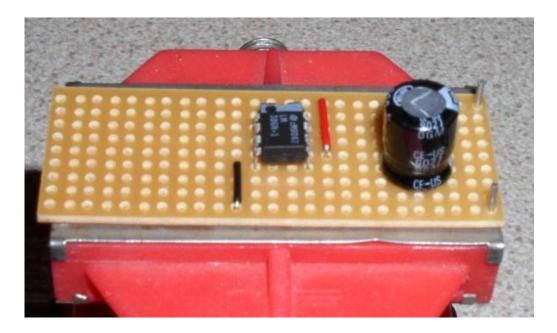

#### Step 5

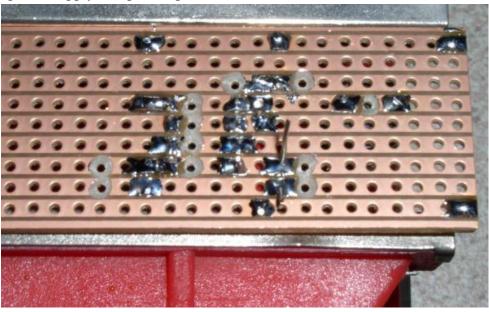

Turn the board over, all component pins should poke through the shiny copper side of the board. All soldering and track cutting is also done on this side. You need a little soldering experience to begin with. If you are not used to soldering, then it is advisable to use a plastic IC socket. There are other advantages to using a socket, mainly if the IC should fail, it can be simply unplugged from the socket and replaced, no need to desolder and resolder. Remember that as the board is now upside down that the top and bottom tracks are reversed. If you turn it upside down and through 180 degrees then left and right are also interchanged. This must be born in mind throughout construction. If in doubt, turn the board back and forth and keep an eye on a reference point, say pin 1 of the IC, marked with a dimple or round spot.

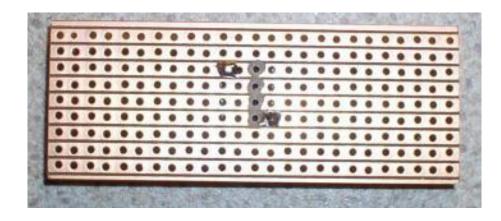

Here we have soldered diagonally opposite legs. This makes sure the IC is held firmly. Next the veroboard track cutter is used to break 4 holes in the centre of the IC (or IC socket). Without this pins 1 and 8, 2 and 7, 3 and 6, 4 and 5 would be short-circuited. After breaking the tracks, solder the remaining pins on the IC or IC socket.

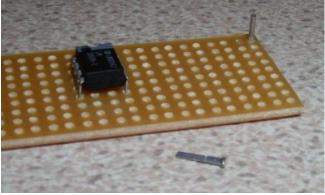

#### Step 6

Turn the board over and use two veropins for the power connectors. A veropin is a short piece of metal that makes contact with the copper side of the veroboard. It is rigid and allows a wire to be connected on the component side of the board. Veropins also make convenient test points as well.

A veropin is shown above (centre bottom). Push two veropins through the copper side at the right hand side on track extremities. It is a good idea to separate power supply rails by at least one vero track.

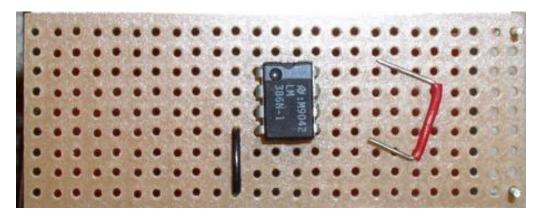

Step 7

Now the IC and power rails are ascertained, it is time to start wiring. Pin 4 is the ground connection, so a piece of wire is used to connect from the adjacent track next to pin 4 of the LM386 to the ground track (bottom track) with veropin. I use black for ground connections, and red wires for power.

#### Step 8

The wire (also called a "jumper") because it bridges are spans several tracks is soldered on the copper side. After soldering the end wires are cut close to the board. The red jumper connects pin 6 of the IC to the top power rail and can be seen in the photo below already soldered.

#### Step 9

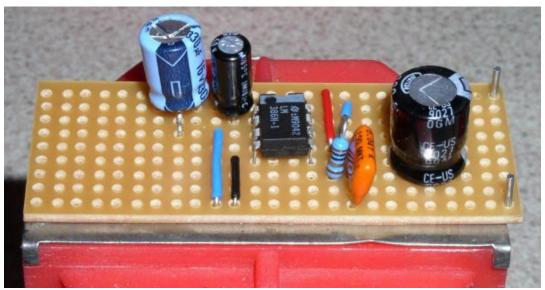

Components can be added in any order, I prefer to use the larger parts first, so I am aware of the physical space left on the board. It is however good practice to solder veropins, jumpers first, then passive components, resistors, capacitors, inductors, followed by active components such as diodes and transistors next. Finally IC's are added last, the reason for this order is that repeated soldering and excessive overheating of the board can destroy the sensitive components. If however, you are a competent at soldering, any order of assembly can take place.

The board is turned over and the 330u output capacitor put in place. From the schematic the "+" plate needs to connect to pin 5 of the IC. I place the component a few holes away on the same track as pin 5 of the IC in the same direction.

#### Step 10

As can be seen below, the 330u capacitor is now soldered a few holes away from pin 5 of the IC. Also note that the centre track of the capacitor is broken. If you forget to do this then the component is short circuited by the vero track itself. Components may be placed in line with the tracks, at right angles, or diagonally, there are no rules. However, if components are in line with a track, then the track must be broken, otherwise the component is short circuited. The output from the amplifier (see schematic) is the negative side of this capacitor. A veropin can also be used to make the external connection to a loudspeaker easier.

As the output capacitor has been soldered, the zobel network comprising of the 1R5 resistor and 100n capacitor are wired up. Referring to the schematic, one end of the resistor is also connected to pin 5, one end of the capacitor goes to ground, and the free ends of these two components are wired together.

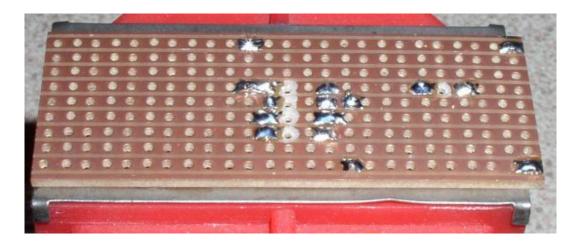

#### Step 12

This is the underside of the 1R5 resistor and 100n capacitor. The resistor is wired adjacent to pin5 of the IC and to the track immediately below the IC. The 100n capacitor is wired adjacent to the resistor and to ground.

As no more connections are at the union of the resistor and capacitor, the tracks are cut either side. The track either side of the break is now free to be used, if required. The tiny piece of solder also on the same track as pin 5 of the IC is a solder splash. As long as the solder blob does not bridge adjacent tracks, it is nothing to worry about.

#### Step 13

Referring to the schematic, the output side of the amplifier is almost complete, apart from a 10u electrolytic capacitor connected to pins 1 and 8 of the IC. Note the polarity, the positive terminal

connect at pin 1, so the capacitor is pushed through a veroboard hole adjacent to pin 1 of the LM386, at right angles to the copper tracks on the reverse side.

As pin 8 is connected to the negative plate of the capacitor, a blue jumper wire is pushed through a hole near the IC on pin 8, the other end of the jumper wire is connected to the same track as the negative pin of the 10u capacitor. This is shown in the above picture.

#### Step 14

The underside of the veroboard is shown below. Note that the right hand side of the picture shows the power supply veropins (top and bottom tracks).

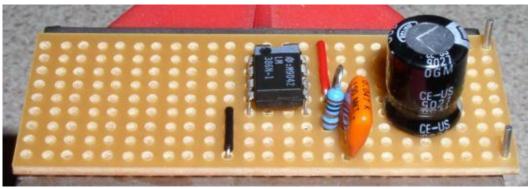

Step 15

The final 330u electrolytic capacitor can be added. This is the leftmost capacitor in the schematic.

This capacitor is inserted so that the positive plate is on the positive power track and the negative plate reached to the same track as pin 2 of the LM386 which is also at ground potential. The final component is the volume control. As this is external all that remains is to solder a length of screened cable between the LM386 at pin 3 and ground.

#### Step 16

Job complete. A final closeup inspection of the board is recommended. Pay particular attention to all areas where the tracks have been cut and also where there are any solder splashes. All soldered joints should appear shiny as in the picture below.

Step 17

The final completed amplifier circuit with a short length of screened cable (grey) leading off to the volume control.

## Lab Procedure

#### **OBJECTIVE**

To apply DC biasing & ac signal & observe the output.

#### 2.3 EQUIPMENT REQUIRED

- 1- Your circuit board

- 2- Function Generator

- 3- Oscilloscope

- 4- DC Supply

- 5- Multimeter

#### 2.4 PROCEDURE

- 1- Check the continuity of all tracks using multimeter.

- 2- Apply the DC supply to the circuit.

- 3- Check the voltages across each component & write them in the following table.

| Across:             | Voltage (V) |

|---------------------|-------------|

| 1) 330uF capacitors |             |

| 2) Pin 6 & 4 of IC  |             |

| 3) 10uF capacitor   |             |

| 4) | R5                     |  |

|----|------------------------|--|

| 5) | Pin 3 & 4              |  |

| 6) | 220k ohm potentiometer |  |

- 4- Now apply a 100Hz, 1mVpk-pk sine wave from function generator to the circuit input (at potentiometer).

- 5- Check the output ac voltage across Pin 5 & 4 using oscilloscope.

- 6- Using following formulas & reading, fill the following table.

| Vin (across Potentiometer) |  |

|----------------------------|--|

| Vout (across pin 5 & 4)    |  |

| Gain (Gain = Vout/Vin)     |  |

# Post Lab

### Task:

- **1-** Calculate value of maximum input for which output is a sine wave.

- 2- Calculate the range of frequency for which output is a sine wave.

- **3-** Attach the simulated version of the circuit.

# Lab Session 3

# **OBJECTIVE**

To study the characteristic curves of Silicon & Germanium diodes

### 3.1 INTRODUCTION

### **BIASING A DIODE**

As you have learned, no electrons move through the pn junction at equilibrium. Generally the term bias refers to the use of a dc voltage to establish certain operating conditions for an electronic device. In relation to a diode, there are two bias conditions: forward and reverse. Either of these bias conditions is established by connecting a sufficient de voltage of the proper polarity across the pn junction.

### **Forward Bias**

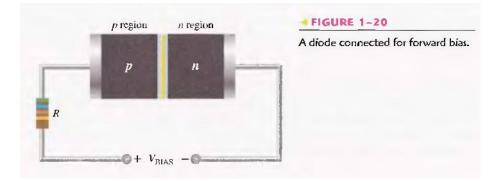

To bias a diode, you apply a de voltage across it. Forward bias is the condition that allows current through the pn junction. Figure 1-20 shows a dc voltage source connected by conductive material (contacts and wire) across a diode in the direction to produce forward bias. This external bias voltage is designated as  $V_{\text{bias}}$ . The resistor, R, limits the current to a value that will not damage the diode.

Notice that the negative side of  $V_{\text{bias}}$  is connected to the n region of the diode and positive side is connected to the p region. This is one requirement for forward bias. A second requirement is that the bias voltage.  $V_{\text{bias}}$ , must be greater than the barrier potential.

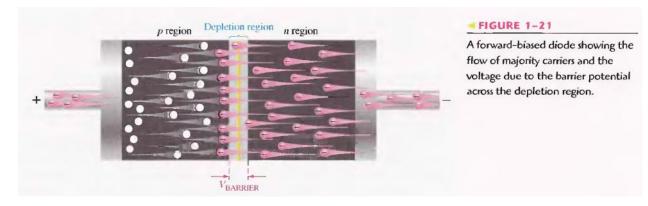

A fundamental picture of what happens when a diode is Forward-biased is shown in Figure 1-21. Because like charges repel, the negative side of the bias-voltage source "pushes" the free electrons which are the majority carriers in the n region toward the pn junction. This flow of free electrons is called electron current. The negative side of the source also provides a continuous flow of electrons through the external connection (conductor) and into the n region as shown.

The bias-voltage source imparts sufficient energy to the free electrons for them to overcome the barrier potential of the depletion region and move on through into the p region. Once in the p region, these conduction electrons have lost enough energy to immediately combine with holes in the valence band.

Now, the electrons are in the valence band in the p region, simply because they have lost too much energy overcoming the barrier potential to remain in the conduction band. Since unlike charges attract, the positive side of the bias-voltage source attracts the valence electrons toward the left end of the p region. The holes in the p region provide the medium or "pathway" for these valence electrons to move through the p region. The electrons move from one hole to the next toward the left. The holes, which are the majority carriers in the p region, effectively (not actually) move to the right toward the junction, as you can see in Figure 1-21. This effective flow of holes is called the hole current. You can also view the hole current as being created by the flow of valence electrons through the p region, with the holes providing the only means for these electrons to flow.

A forward-biased diode showing the flow of majority carriers and the voltage due to the barrier potential across the depletion region.

As the electrons flow out of the p region through the external connection (conductor) and to the positive side of the bias-voltage source, they leave holes behind in the p region; at the same time, these electrons become conduction electrons in the metal conductor. Recall that the conduction band in a conductor overlaps the valence band so that it takes much less energy for an electron to be a free electron in a conductor than in a semiconductor. So there is a continuous availability of holes effectively moving toward the pn junction to combine with the continuous stream of electrons as they come across the junction into the p region.

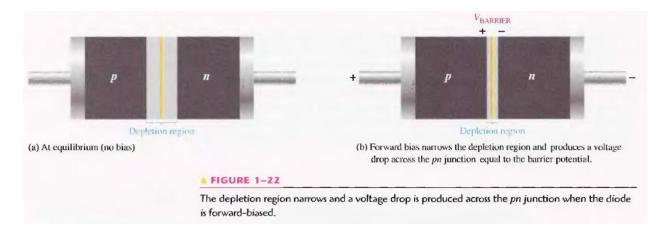

**The Effect of Forward Bias on the Depletion Region** As more electrons flow into the depletion region the number of positive ions is reduced. As more holes effectively flow into the depletion region on the other side of the p/1 junction, the number of negative ions is reduced. This reduction in positive and negative ions during forward bias causes the depletion region to narrow, as indicated in Figure 1-22.

The Effect of the Barrier Potential during Forward Bias Recall that the electric field between the positive and negative ions in the depletion region on either side of the junction creates an "energy hill" that prevents free electrons from diffusing across the junction at equilibrium(see Figure 1-19(b). This is known as the barrier potential. When forward bias is applied, the free electrons are provided with enough energy from the bias-voltage source to overcome the barrier potential and effectively "climb the energy hill" and cross the depletion region. The energy that the electrons require in order to pass through the depletion region is equal to the barrier potential. In other words the electrons give up an amount of energy equivalent to the barrier potential when they cross the depletion region. This energy loss results in a voltage drop across the pn junction equal to the barrier potential (0.7 V), as indicated in Figure 1-22(b). An additional small voltage drop occurs across the p and /1 regions due to the internal resistance of the material. For doped semi conductive material, this resistance, called the dynamic resistance, is very small and can usually be neglected.

#### **Reverse Bias**

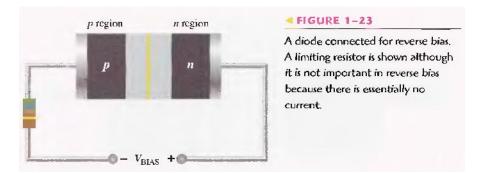

Reverse bias is the condition that essentially prevents current through the diode. Figure 1-23 shows a dc voltage source connected across a diode in the direction to produce reverse bias. This external bias voltage is designated as Vbias just as it was for forward bias. Notice that the positive side of Vbias is connected to the n region of the diode and the negative side is connected to the p region. Also note that the depletion region is shown much wider than in forward bias or equilibrium.

An illustration of what happens when a diode is reverse-biased is shown in Figure 1-24. Because unlike charges attract, the positive side of the bias-voltage source "pulls" the free electrons, which are the majority carriers in the 17 region, away from the pn junction. As the electrons flow toward the positive

side of the voltage source, additional positive ions are created. This results in a widening of the depletion region and a depletion of majority carriers.

In the p region, electrons from the negative side of the voltage source enter as valence electrons and move from hole to hole toward the depletion region where they create additional negative ions. This results in a widening of the depletion region and a depletion of majority carriers. The flow of valence electrons can be viewed as holes being "pulled" toward the positive side. The initial flow of charge carriers is transitional and lasts for only a very short time after the reverse-bias voltage is applied. As the depletion region widens, the availability of majority carriers decreases. As more of the n and p regions become depleted of majority carriers, the electric field between the positive and negative ions increases in strength until the potential across the depletion region equals the bias voltage, Vbias. At this point the transition current essentially ceases except for a very small reverse current that can usually be neglected.

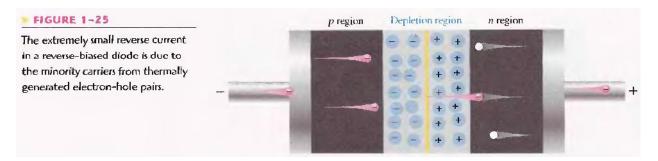

**Reverse Current** The extremely small current that exists in reverse bias after the transition current dies out is caused by the minority carriers in the 11 and p regions that are produced by thermally generated electron-hole pairs. The small number of free minority electrons in the p region are "pushed" toward the pn junction by the negative bias voltage. When these electrons reach the wide depletion region, they "fall down the energy hill" and combine with the minority holes in the n region as valence electrons and flow toward the positive bias voltage, creating a small hole current. The conduction band in the p region is at a higher energy level than the conduction band in the n region. Therefore, the minority electrons easily pass through the depletion region because they require no additional energy. Reverse current is illustrated in Figure 1-25.

**Reverse Breakdown** Norn1ally, the reverse current is so small that it can be neglected. However, if the external reverse-bias voltage is increased to a value called the breakdown voltage, the reverse current will drastically increase.

This is what happens. The high reverse-bias voltage imparts energy to the free minority electrons so that as they speed through the p region, they collide with atoms with enough energy to knock valence

electrons out of orbit and into the conduction band. The newly created conduction electrons are also high in energy and repeat the process. If one electron knocks only two others out of their valence orbit during its travel through the p region. The numbers quickly multiply. As these high-energy electrons go through the depletion region, they have enough energy to go through the 11 region as conduction electrons, rather than combining with holes. The multiplication of conduction electrons just discussed is known as avalanche and results in a very high reverse cunent that can damage the diode because of excessive heat dissipation.

# **VOLTAGE-CURRENT CHARACTERISTIC OF A DIODE**

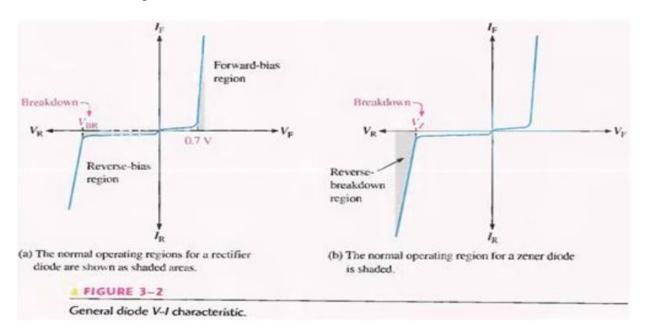

As you have learned, forward bias produces current through a diode and reverse bias essentially prevents current. except for a negligible reverse current. Reverse bias prevents current as long as the reverse-bias voltage does not equal or exceed the breakdown voltage of the junction.

### V-I Characteristic for Forward Bias

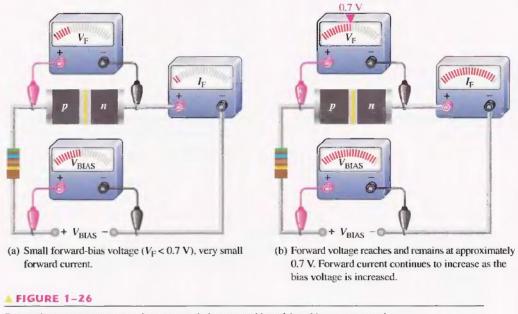

When a forward-bias voltage is applied across a diode, there is current. This current is called the forward current and is designated  $I_F$  Figure 1-26 illustrates what happen as the forward-bias voltage is increased positively from 0 V The resistor is used to limit the forward current to a value that will not overheat the diode and cause damage.

Forward-bias measurements show general changes in  $V_{\rm F}$  and  $I_{\rm F}$  as  $V_{\rm BIAS}$  is increased.

With 0 V across the diode, there is no forward current. As you gradually increase the forward-bias voltage, the forward current and the voltage across the diode gradually increase, as shown in Figure 1-26(a). A portion of the forward-bias voltage is dropped across the limiting resistor. When the forward-bias voltage is increased to a value where the voltage across the diode reaches approximately 0.7 V (barrier potential), the forward current begins to increase rapidly, as illustrated in Figure 1-26(b). As you continue to increase the forward-bias voltage, the current continues to increase very rapidly, but the voltage across the diode increases only gradually above 0.7 V. This small increase in the diode voltage

above the barrier potential is due to the voltage drop across the internal dynamic resistance of the semi conductive material.

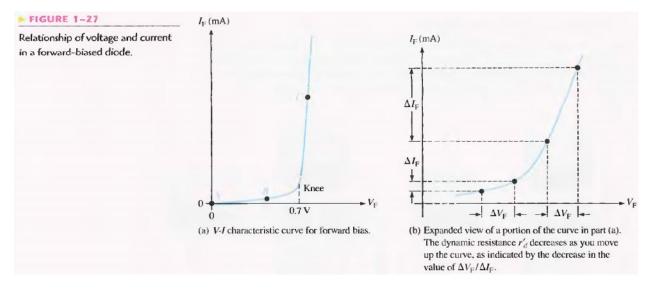

**Graphing the V-I Curve** If you plot the results of the type of measurements shown in Figure 1-26 on a graph, you get the V-I characteristic curve for a forward-biased diode, as shown in Figure 1-27(a). The diode forward voltage ( $V_F$ ) increases to the right along the horizontal axis, and the forward current ( $I_F$ ) increases upward along the vertical axis. As you can see in Figure 1-27(a), the forward current increases very little until the forward voltage across the pn junction reaches approximately 0.7 V at the knee of the curve. After this point, the forward voltage remains at approximately 0.7 V, but  $I_F$  increases rapidly. As previously mentioned, there is a slight increase in  $V_F$  above 0.7 V as the current increases due mainly to the voltage drop across the dynamic resistance. Normal operation for a forward-biased diode is above the knee of the curve. The  $I_F$  scale is typically in mA, as indicated.

Three points A, B, and C are shown on the curve in Figure 1-27(a). Point A corresponds to a zero-bias condition. Point B corresponds to Figure 1-26(a) where the forward voltage is less than the barrier potential of 0.7 V. Point C corresponds to Figure 1-26(a) where the

forward voltage approximately equals the barrier potential. As the external bias voltage and forward current continue to increase above the knee, the forward voltage will increase slightly above 0.7 V. In reality, the forward voltage can be as much as approximately 0.90 V, depending on the forward current.

**Dynamic Resistance** Figure 1-27(b) is an expanded view of the V-I characteristic curve in part (a) and illustrates dynamic resistance. Unlike a linear resistance, the resistance of the forward-biased diode is not constant over the entire curve. Because the resistance changes as you move along the V-I curve, it is called dynamic or ac resistance. Internal resistances of electronic devices are usually designated by lowercase italic l' with a prime, instead of the standard R. The dynamic resistance of a diode is designated r'<sub>d</sub>.

Below the knee of the curve the resistance is greatest because the current increases very little for a given change in voltage ( $\dot{r}_{d} = V_{F}/I_{F}$ ). The resistance begins to decrease in the region of the knee of the curve

and becomes smallest above the knee where there is a large change in current for a given change in voltage.

#### V-I Characteristic for Reverse Bias

When a reverse-bias voltage is applied across a diode, there is only an extremely small reverse current  $(I_R)$  through the pn junction. With 0 V across the diode, there is no reverse current. As you gradually increase the reverse-bias voltage, there is a very small reverse current and the voltage across the diode increases. When the applied bias voltage is increased to a value where the reverse voltage across the diode  $(V_R)$  reaches the breakdown value  $(V_{BR})$ , the reverse current begins to increase rapidly.

As you continue to increase the bias voltage, the current continues to increase very rapidly, but the voltage across the diode increases very little above  $V_{BR}$ . Breakdown, with exceptions, is not a normal mode of operation for most pn junction devices.

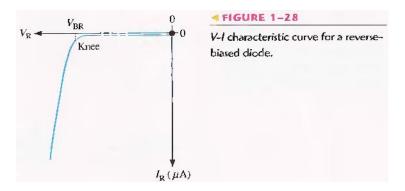

**Graphing the V-I Curve** If you plot the results of reverse-bias measurements on a graph, you get the V-I characteristic curve for a reverse-biased diode. A typical curve is shown in Figure 1-28. The diode reverse voltage  $(V_R)$  increases to the left along the horizontal axis and the reverse current  $(I_R)$  increases downward along the vertical axis.

There is very little reverse current (usually  $\mu$ A or nA) until the reverse voltage across the diode reaches approximately the breakdown value (V<sub>BR</sub>) at the knee of the curve. After this point, the reverse voltage remains at approximately V<sub>BR</sub>, but I R increases very rapidly, resulting in overheating and possible damage. The breakdown voltage for a typical silicon diode can vary, but a minimum value of 50 V is not unusual.

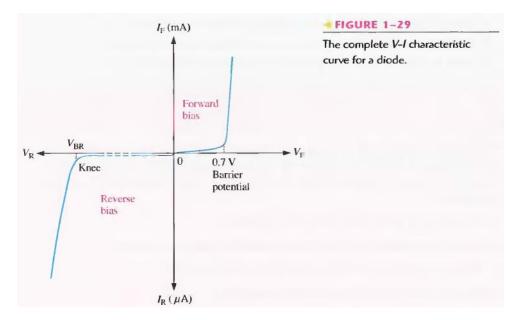

#### The Complete V-I Characteristic Curve

Combine the curve, for both forward bias and reverse bias, and you have the complete V-I characteristic curve for a diode, as shown in Figure 1-29. Notice that the IF scale is in mA compared to the  $I_R$  scale in  $\mu A$ .

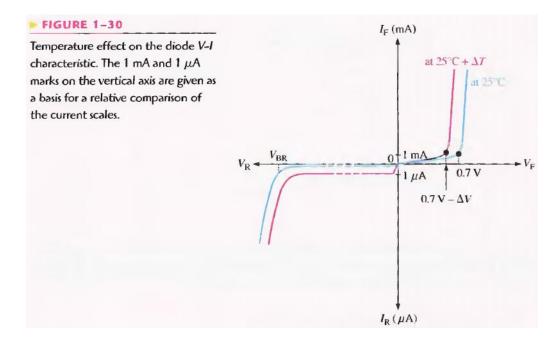

**Temperature Effects** For a forward-biased diode, as temperature is increased, the forward current increases for a given value of forward voltage. Also, for a given value of forward current, the forward voltage decreases. This is shown with the V-I characteristic curves in Figure 1-30. The blue curve is at room temperature ( $25^{\circ}$ C) and the red curve is at an elevated temperature ( $25^{\circ}$ C) + T). Notice that the barrier potential decreases as temperature increases.

For a reverse-biased diode, as temperature is increased, the reverse current increases. The difference in the two curves is exaggerated on the graph in Figure 1-30 for illustration. Keep in mind that the reverse current below breakdown remains extremely small and can usually be neglected.

# Pre Lab

## **OBJECTIVE**

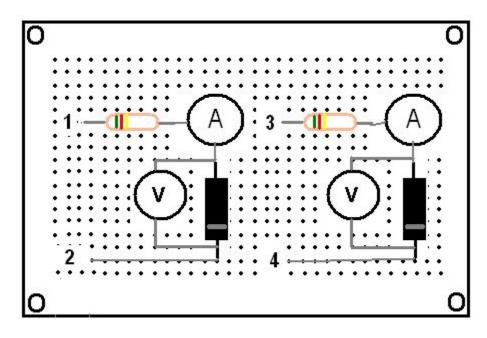

Construct the following circuit on bread board & Test for continuity.

### **REQUIRED COMPONENTS**

- 1) Bread-board

- 2) Silicon diode

- 3) Germanium diode

- 4) 2 Resistors (10K each)

### PROCEDURE

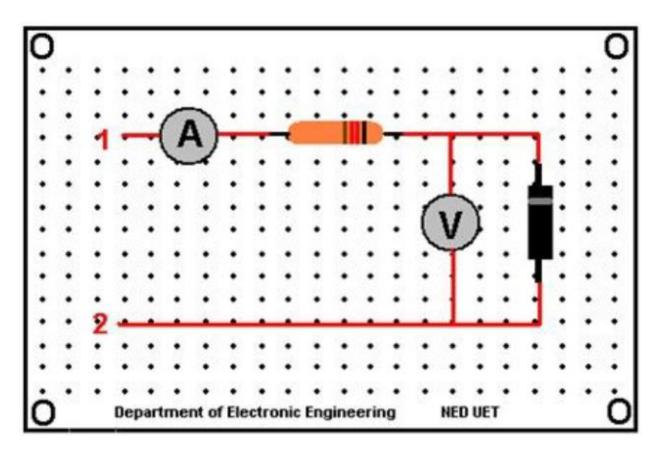

Make the circuit as shown.

#### OBJECTIVE

To plot the V-I curve of Silicon & Germanium diodes.

#### PROCEDURE

- 1- Apply positive supply across terminal 1 & 2. (Terminal 1 being positive)

- 2- Connect a voltmeter across 1<sup>st</sup> diode & start varying the variable supply voltages.

- 3- For each division of voltages, note the corresponding current & voltage across the diode.

- 4- Take at least nine readings & then reverse the supply voltages across terminal 1 & 2. (This time terminal 2 being positive)

- 5- Repeat the same procedure for negative voltages

- 6- Repeat the same procedure for germanium diode also.

- 7- After getting all the readings, plot the V-I curve for both diodes.

#### **OBSERVATIONS**

#### FORWARD BAIS MODE

#### SILICON DIODE

# GERMANIUM DIODE

| Voltage | Current |

|---------|---------|

|         |         |

|         |         |

|         |         |

|         |         |

|         |         |

|         |         |

|         |         |

|         |         |

|         |         |

#### **REVERSE BAIS MODE**

#### SILICON DIODE

| Voltage | Current |  |

|---------|---------|--|

|         |         |  |

|         |         |  |

|         |         |  |

|         |         |  |

|         |         |  |

|         |         |  |

|         |         |  |

|         |         |  |

#### GERMANIUM DIODE

| Voltage | Current |

|---------|---------|

|         |         |

|         |         |

|         |         |

|         |         |

|         |         |

|         |         |

|         |         |

|         |         |

#### GRAPH:

Attach both graphs here.

#### POST LAB

1- Make both circuits on multisim &attach the print out of simulated circuits.

# Lab Session 04

### **OBJECTIVE**

To study the half-wave rectifier

### 4.1 INTRODUCTION

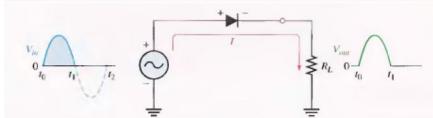

Because of their ability to conduct current in one direction and block current in other direction, diodes are used in circuits called rectifiers that convert ac voltage into dc voltage. Rectifiers are found in all dc power supplies that operate from an ac voltage source. A power supply is an essential part of each electronic system from the simplest to the most complex. In this section, you will study the most basic type of rectifier, the half-wave rectifier.

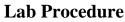

#### 4.1.1 The Basic DC Power Supply

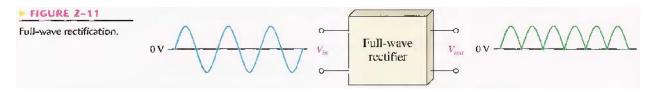

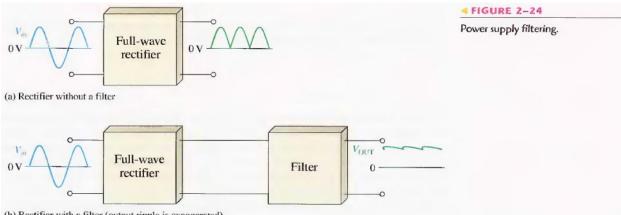

The DC power supply converts the standard 220 V, 50 Hz ac available at wall outlets into a constant dc voltage. It is one of the most common electronic circuits that you will find. The dc voltage produced by a power supply is used to power all types of electronic circuits, such as television receivers, stereo systems, VCRs, CD players and most laboratory equipment. Basic block diagrams for a rectifier and complete power supply are shown in Figure 2-1. The rectifier can be either a half-wave rectifier or a full-wave rectifier (covered in proceeding labs). The rectifier converts the ac input voltage to a pulsating dc voltage, which is half-wave rectified as shown in Figure 2-1(a). A block diagram for a complete power supply is shown in part (b). The filter eliminates the fluctuations in the rectified voltage and produces a relatively smooth dc voltage. The power supply filter is covered in proceeding labs. The regulator is a circuit that maintains a constant de voltage for variations in the input line voltage or in the load. Regulators vary from a single device to more complex integrated circuits. The load is a circuit or device for which producing the voltage the power supply is dc and load current.

(b) Complete power supply with rectifier, filter, and regulator

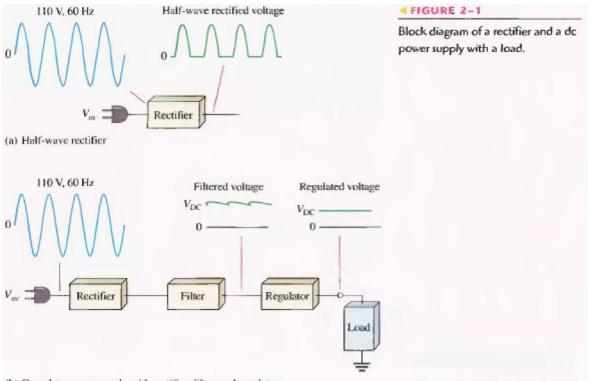

FIGURE 2-2

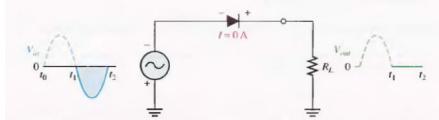

Half-wave rectifier operation. The diode is considered to be ideal.

(a) During the positive alternation of the 60 Hz input voltage, the output voltage looks like the positive half of the input voltage. The current path is through ground back to the source.

(b) During the negative alternation of the input voltage, the current is 0, so the output voltage is also 0.

(c) 60 Hz half-wave output voltage for three input cycles

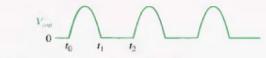

#### 4.1.2 Average Value of the Half-Wave Output Voltage

The average value of the half-wave rectified output voltage is the value you would measure on a dc voltmeter. Mathematically, it is determined by finding the area under the curve over a full cycle, as illustrated in Figure 2-3, and then dividing by 2, the number of radians in a full cycle. The result of this is expressed in Equation 2-1, where  $V_P$  is the peak value of the voltage. This equation shows that  $V_{AVG}$  is approximately 31.8% of  $V_P$  for a half-wave rectified voltage.

```

Equation 2-1 V_{AVG} = \frac{Vp}{\pi}

```

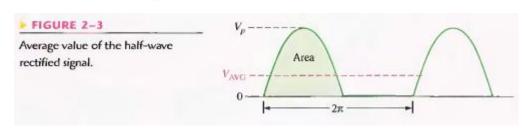

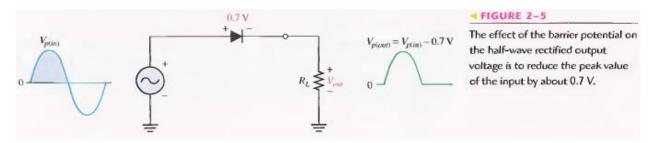

#### 4.1.3 Effect of the Barrier Potential on the Half-Wave Rectifier Output

In the previous discussion, the diode was considered ideal. When the practical diode model is used with the barrier potential of 0.7 V taken into account, this is what happens. During the positive half-cycle, the input voltage must overcome the barrier potential before the diode becomes forward-biased. This results in a half-wave output with a peak value that is 0.7 V less than the peak value of the input, as shown in Figure 2-5. The expression for the peak output voltage is:

Equation 2-2  $V_{P(out)} = V_{P(in)} - 0.7$

It is usually acceptable to use the ideal diode model, which neglects the effect of the barrier potential, when the peak value of the applied voltage is much greater than the barrier potential (at least 10 V, as a rule of thumb).

#### 4.1.4 Peak Inverse Voltage (PIV)

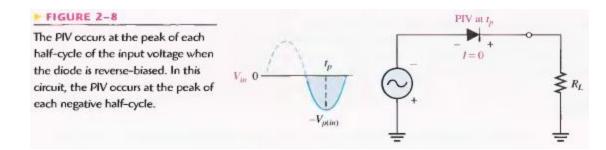

The peak inverse voltage (PIV) equals the peak value of the input voltage, and the diode must be capable of withstanding this amount of repetitive reverse voltage. For the diode in Figure 2-8, the maximum value of reverse voltage, designated as PIV occurs at the peak of each negative alternation of the input voltage when the diode is reverse-biased.

Equation 2-3  $PIV = V_{P(in)}$

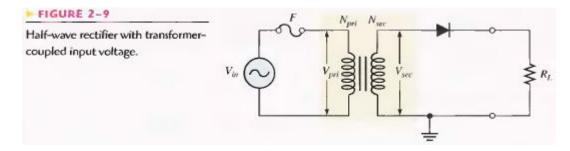

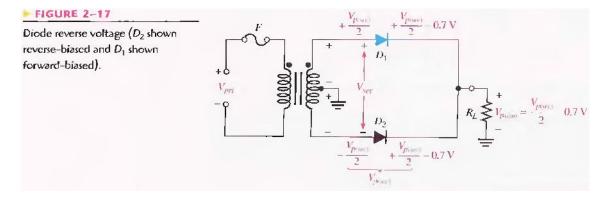

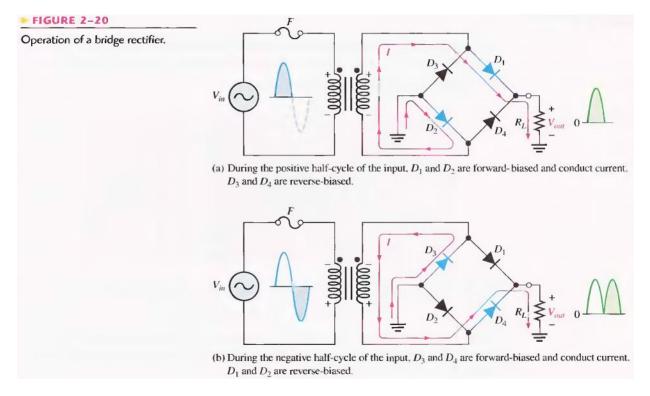

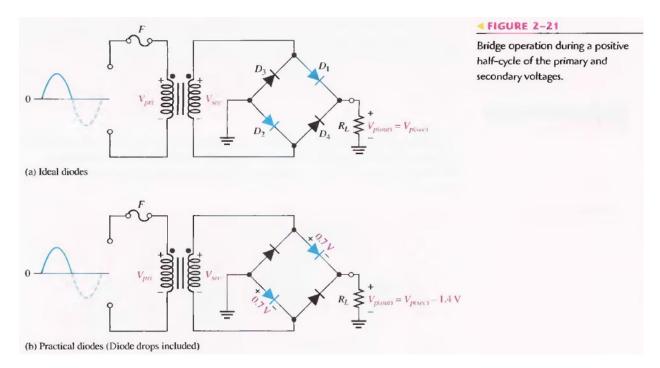

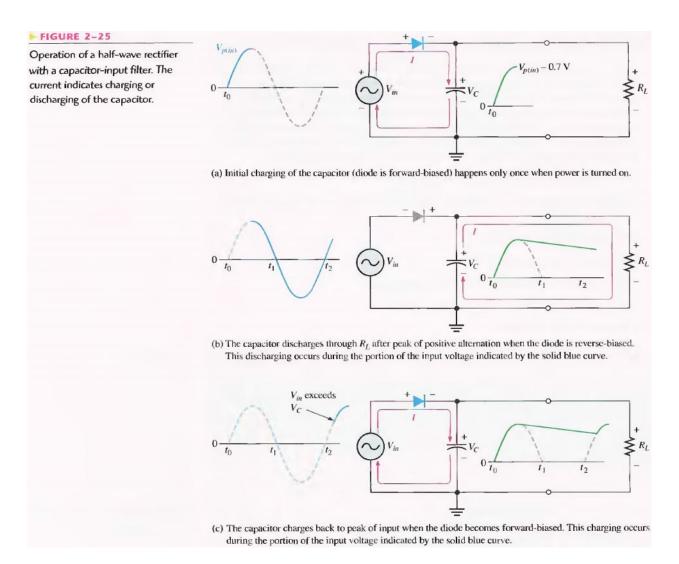

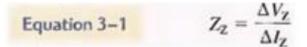

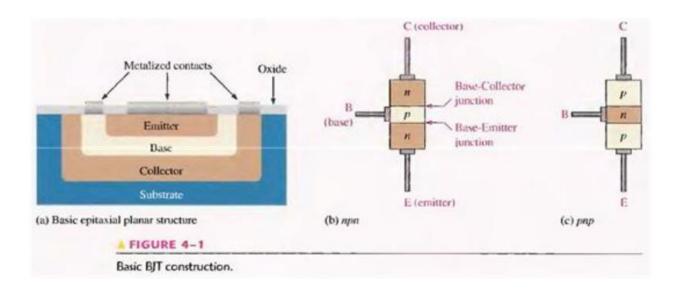

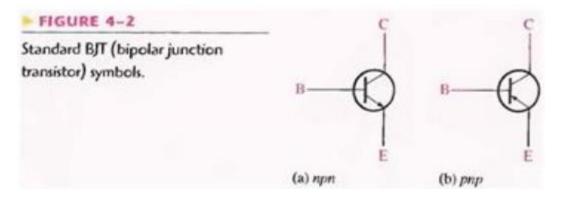

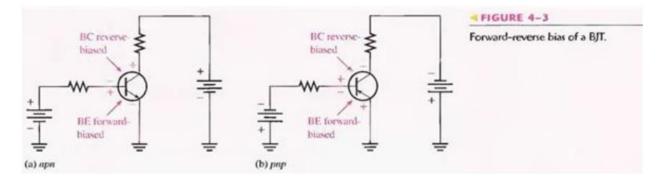

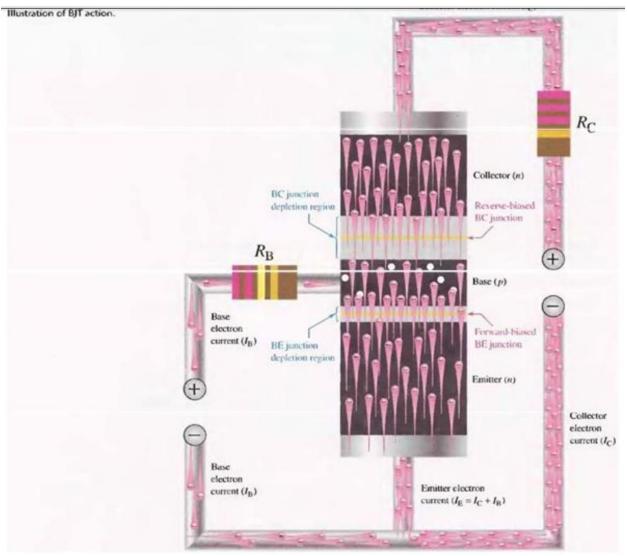

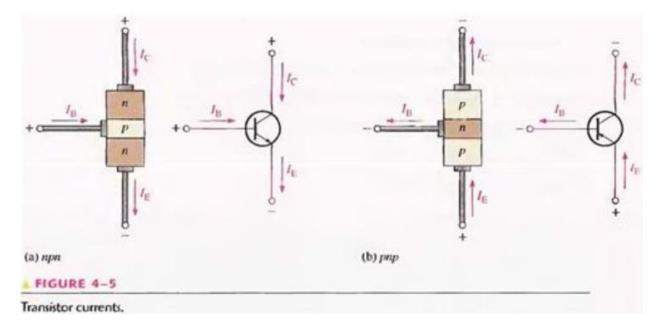

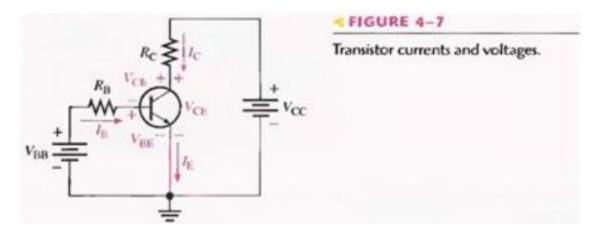

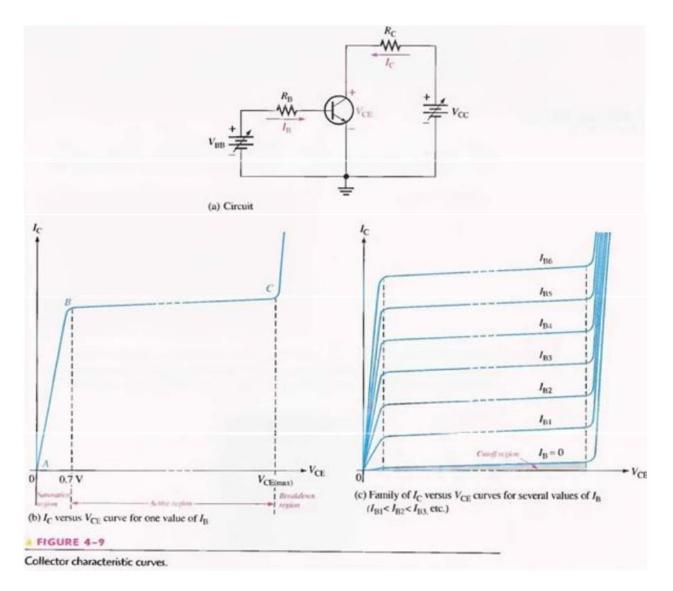

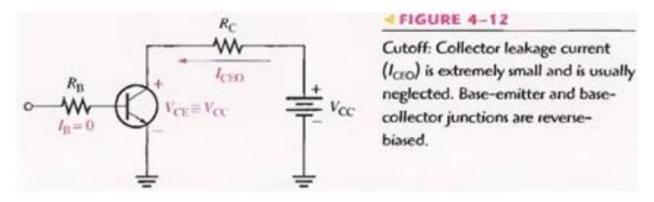

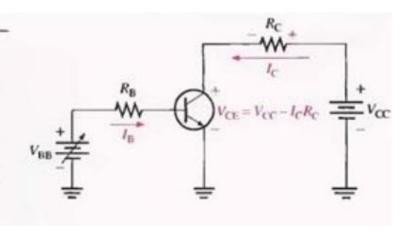

#### 4.1.5 Half-Wave Rectifier with Transformer-Coupled Input Voltage