Program: BC (CS) Subject: Digital Logic Design (Theory) **Assignment Number: 04** Course Code: CSC-201 EDP Code: 102010016 Semester: Fall 2020

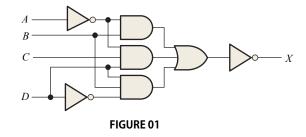

Write the output expression for circuit in Figure 01.

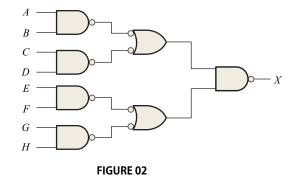

- Q.2 Write the output expression for circuit as it appears in Figure 02 and then change it to an equivalent AND-OR configuration.

- Q.3 Develop the truth table for circuit in Figure 02.

- Show that an exclusive-NOR circuit produces a POS output. Q.4

- Use AND gates, OR gates, or combinations of both to implement the following logic Q.5 expressions as stated:

X = ABC(D + E + F) + AC(C + D + E)

Use AND gates, OR gates, and inverters as needed to implement the following logic Q.6 expres-sions as stated:

$$X / B(CDE + EFG)(AB + C)$$

Q.1

Q.7 Use NAND gates, NOR gates, or combinations of both to implement the following logic expressions as stated:

$$X = \overline{AB} + CD + (\overline{A+B}) (ACD + \overline{BE})$$

**Q.8** Implement a logic circuit for the truth table in Table 01.

| TABLE 01 |   |   |   |        |

|----------|---|---|---|--------|

| Inputs   |   |   |   | Output |

| A        | В | С | D | X      |

| 0        | 0 | 0 | 0 | 0      |

| 0        | 0 | 0 | 1 | 0      |

| 0        | 0 | 1 | 0 | 1      |

| 0        | 0 | 1 | 1 | 1      |

| 0        | 1 | 0 | 0 | 1      |

| 0        | 1 | 0 | 1 | 0      |

| 0        | 1 | 1 | 0 | 0      |

| 0        | 1 | 1 | 1 | 0      |

| 1        | 0 | 0 | 0 | 1      |

| 1        | 0 | 0 | 1 | 1      |

| 1        | 0 | 1 | 0 | 1      |

| 1        | 0 | 1 | 1 | 1      |

| 1        | 1 | 0 | 0 | 0      |

| 1        | 1 | 0 | 1 | 0      |

| 1        | 1 | 1 | 0 | 0      |

| 1        | 1 | 1 | 1 | 1      |

Q.9

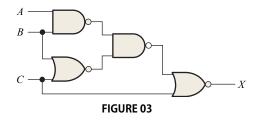

Simplify the circuit in Figure 03 as much as possible, and verify that the simplified circuit is equivalent to the original by showing that the truth tables are identical.

- Q.10 Minimize the gates required to implement the function in Q.6 in SOP form.

- Q.11 Minimize the gates required to implement the function in Q.7 in SOP form.

- Q.12 Minimize the gates required to implement the function of the circuit in Figure 02 in SOP form.

- Q.13 Implement the logic circuits in Figure 01 using only NAND gates.

- Q.14 Implement the logic circuit in Figure 03 using only NAND gates.

- Q.15 Repeat Q.13 using only NOR gates.

- Q.16 Repeat Q.14 using only NOR gates.

Q.17 Show how the following expression can be implemented as stated using only NOR gates:

$X = AB[C(\overline{DE} + \overline{AB}) + \overline{BCE}]$

- Q.18 Repeat Q.17 using only NAND gates.

- Q.19 Implement the function in Q.5 by using only NAND gates.

- Q.20 Implement the function in Q.6 by using only NAND gates.

- Q.21 The output of the logic circuit and input waveforms in Figure 04 is passed through an inverter. Draw the output waveform.

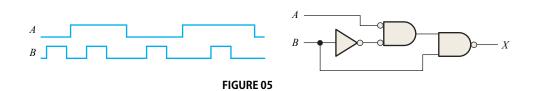

**Q.22** For the logic circuit in Figure 05, draw the output waveform in proper relationship to the inputs.

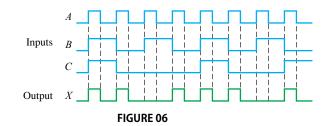

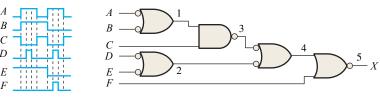

For the input waveforms in Figure 06, what logic circuit will generate the output waveform shown?

Q.24

For the circuit in Figure 07, draw the waveforms at the numbered points in the proper relationship to each other.

FIGURE 07