## **Subject: Digital Logic Design**

## **Major Assignment Final-Term**

**Course Code: CSC-201**

**EDP Code: 102007016**

**Summer Semester 2020**

## Name = MUHAMMAD ILYAS ID 12543

- Q.1 Draw and explain the logic diagram for each of the following:

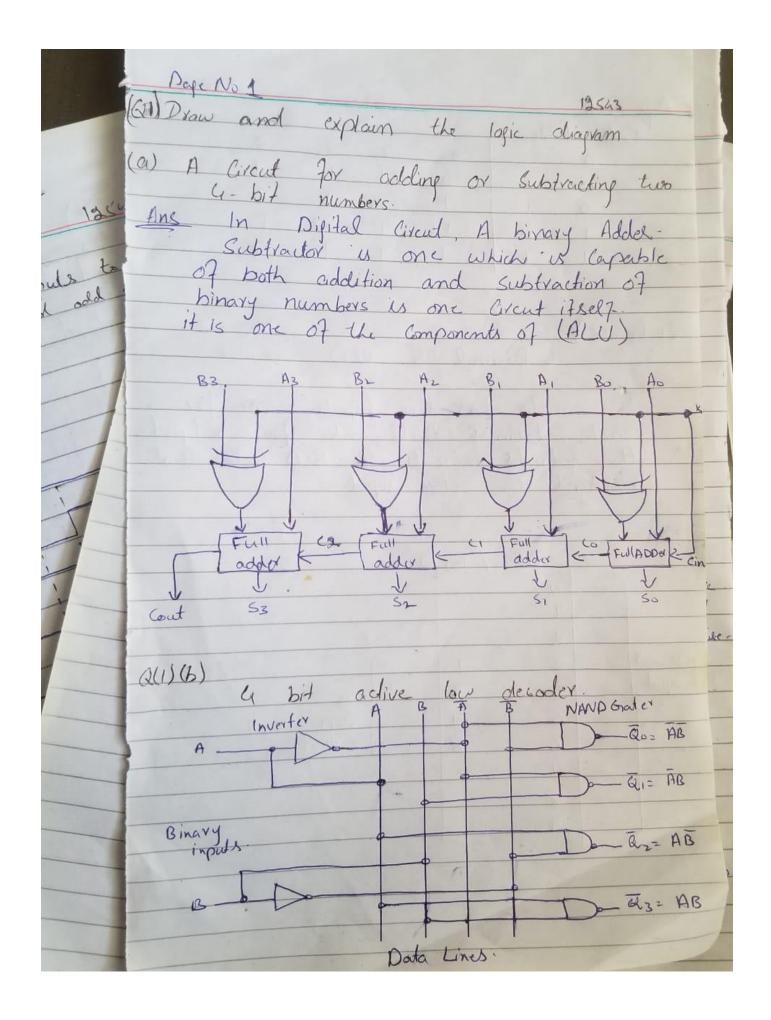

- a) A circuit for adding or subtracting two 4-bit numbers

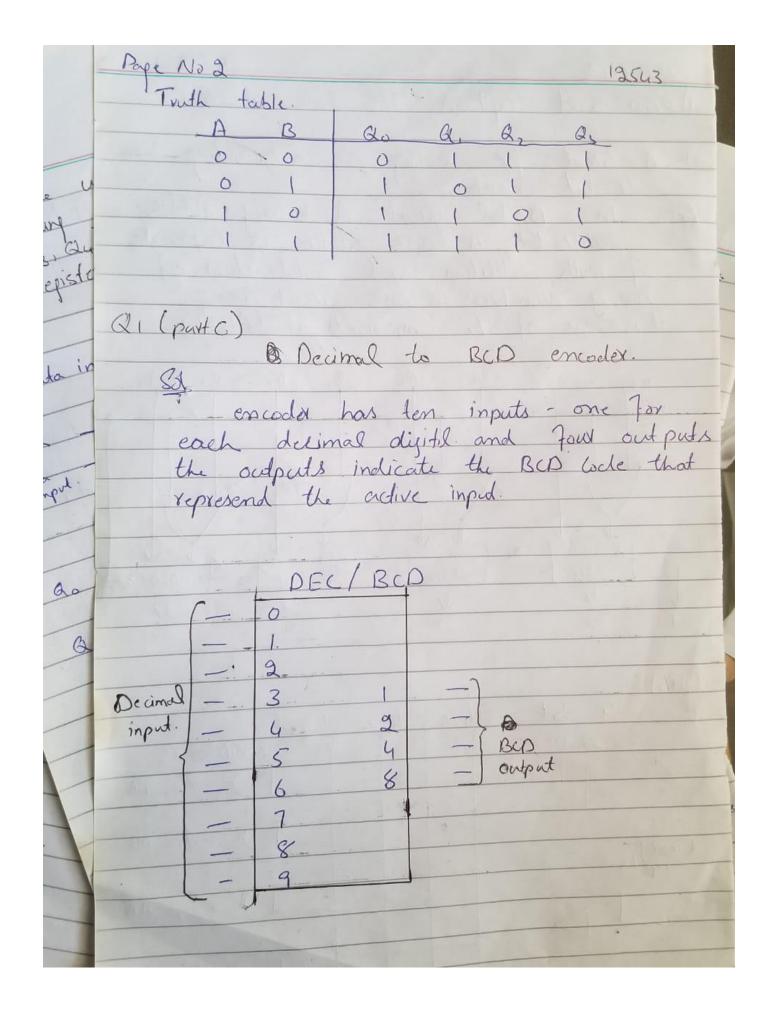

- b) 4-bit active low decoder

- c) Decimal to BCD encoder

- d) Frequency divider (Use 3 J-K flip-flops and assume 16 kHz frequency of the initial wave-form.)

- Q.2 For the 4-input multiplexer, data inputs are given as:

$$D_0 = 0$$

,  $D_1 = 1$ ,  $D_2 = 0$ ,  $D_3 = 1$

Find the output Y if the select inputs are given as:

- Q.3 Timing diagram in Figure 01 shows inputs to a 9-bit parity checker. Draw the  $\Sigma$  Even and  $\Sigma$  Odd output for the even parity checking.

- Q.4 The waveforms in Figure 02 are applied to the J, K, CLK,  $PR\bar{E}$ , and  $CL\bar{R}$  inputs as indicated. Determine the Q output, if the flip-flop is initially RESET.

- Q.5 Use the waveforms in Figure 03 to draw the timing diagram for the parallel outputs  $(Q_1,\ Q_2,\ Q_3,\ Q_4)$  for the shift register. Assume that register is initially cleared.

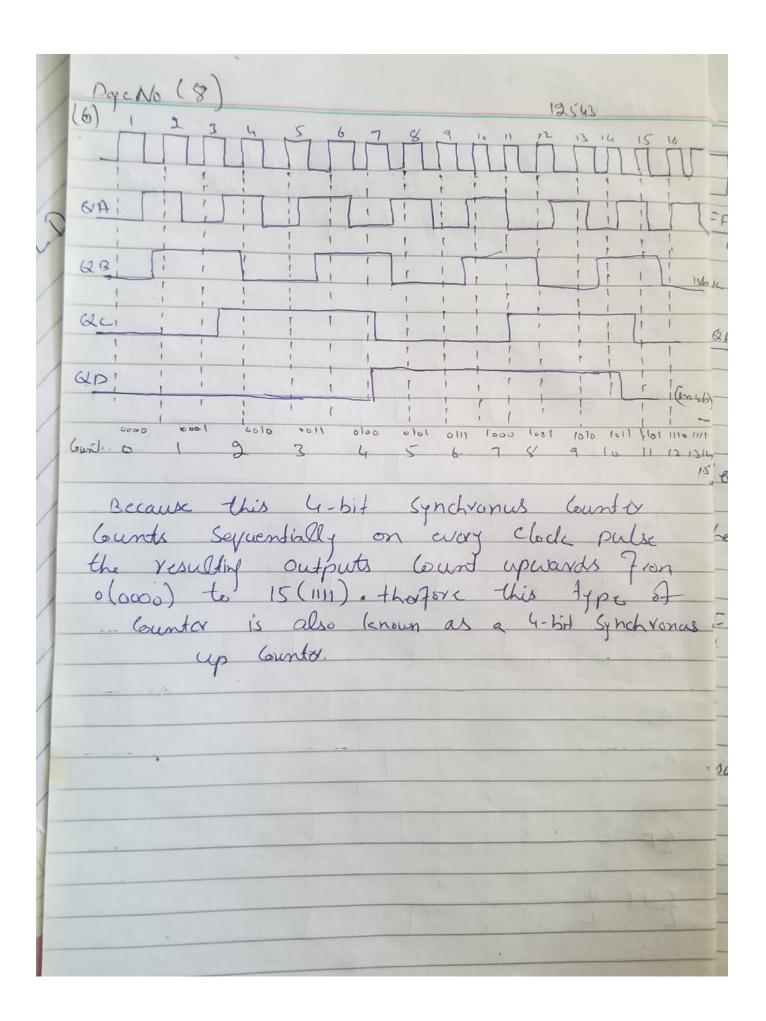

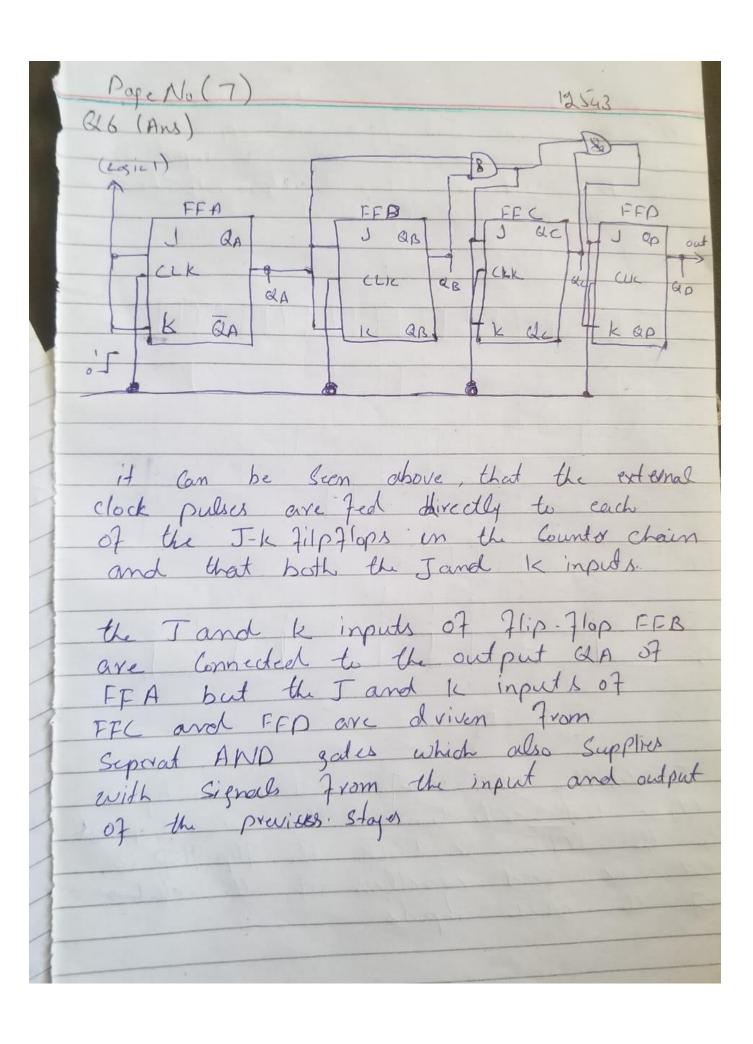

- Q.6 Draw the logic diagram and timing diagram for the 4-stage synchronous binary counter. Verify that the waveforms of the Q outputs represent the proper binary number after each clock pulse.

| Name         | M. ILYAS     |

|--------------|--------------|

| Subject      | DLD          |

| Submitted to | Sir-Amin     |

| Date         | 22-Sep. 2020 |

| TO           | 12543        |

|              |              |

|              |              |

|              |              |

|              |              |

Dae (No 6) as use the waveforms in Fig-3 to draw the timming diag for the parallel adputs (& as as as as ) for the shift register - Assume that register is initially cleared. Data in 0 Q the first data bit entired into the

Page No (5) elette wave forms inch 7 ig 2 are applied to the j, k, CLK, PRE and CLR input as indicated. Determine the & output, if the 7 lip-7 lop is initially Reset. 12543 PRE Fig (9) The Yesulding 1th woweform Shown in Fig (2) Notice that each time a Low is applied to the IPRE Or ICLR, the 71ip-710P is Set or resol regardless of the states of the other impuls.

12545 Parento (4) Asl Tinning diag in fig I shows inpuls to a 9-bit pavily chealer. Draw the Even and odd output for the even pavity chealing. A3 24 H A5 A6

| Page No (3)                                    | +0.51.2          |  |  |

|------------------------------------------------|------------------|--|--|

| Q2: For the 4- mout multipl                    | 19543            |  |  |

| Rg: For the 4-input multip!<br>Po=0, P: 1, Dz= | O Do = 1         |  |  |

|                                                | 0,03             |  |  |

| Find output y i].                              |                  |  |  |

| So = 1 S, = 6                                  |                  |  |  |

| So = 0 S = 1                                   |                  |  |  |

| So = 1 S, = 1                                  |                  |  |  |

| So= 0 S,= 0                                    |                  |  |  |

| Sol                                            | 1 1 10 0 0 0 0   |  |  |

| A 4x1 Mux has 4 inp                            |                  |  |  |

| two Select input (so an                        | ds,) and one out |  |  |

| · Put line Y.                                  |                  |  |  |

| i7 S, So= 00 than                              | y: 00            |  |  |

| 17 S, So=01 they 1: D,                         |                  |  |  |

| 17 S, So = 10 then Y= Dz                       |                  |  |  |

| 12 S.S. = 11 then                              | Y = 03           |  |  |

| Data input                                     | adput.           |  |  |

| S. So                                          | 3                |  |  |

| 0 0                                            | Do               |  |  |

| 0                                              | D,               |  |  |

| 0                                              | D <sub>2</sub>   |  |  |

|                                                | 03               |  |  |

|                                                |                  |  |  |

|                                                |                  |  |  |

|                                                |                  |  |  |