# **Major Assignment Final Term Summer**

Course Name: Digital Logic Design

# **Submitted By:**

Abdul Razzaq (12938)

BS (SE-8) Section: A

## **Submitted To:**

Sir Muhammad Amin

Dated: 22<sup>th</sup> September 2020

Department of Computer Science, IQRA National University, Peshawar Pakistan

#### **Circuit Diagram** $\mathbf{B}_0$ $B_1$ B2 **B**<sub>3</sub> M Aı Ao A2 A3 Cin Cout Cin Cout Cin Cout Cout Full Full Full Full Adder Adder Adder Adder S2

#### **Explanation:**

When M=1, the circuit is a subtractor and when M=0, the circuit becomes adder. The Ex-OR gate consists of two inputs to which one is connected to the B and other to input M. When M=0, B Ex-OR of 0 produce B. Then full adders add the B with A with carry input zero and hence an addition operation is performed.

When M=1, B Ex-OR of 0 produce B complement and also carry input is 1. Hence the complemented B inputs are added to A and 1 is added through the input carry, nothing but a 2's complement operation. Therefore, the subtraction operation is performed.

#### Q1 (b)

#### **Answer:**

### **Decoder**

**Truth Table**

| _ A | В | Q <sub>0</sub> | Q <sub>1</sub> | $Q_2$ | Q <sub>3</sub> |

|-----|---|----------------|----------------|-------|----------------|

| 0   | 0 | 1              | 0              | 0     |                |

| 0   | 1 | 0              | 1              |       | 0              |

| 1   | 0 | 0              | 0              | 1     | 0              |

| 1   | 1 | 0              | 0              | 0     | 1              |

|     |   | 1              |                |       |                |

#### **Explanation:**

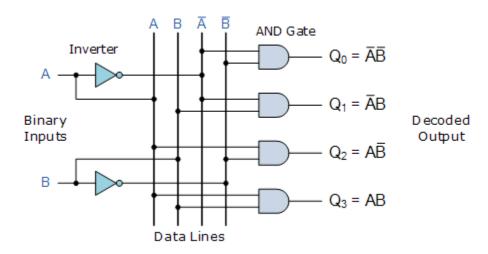

This simple example above of a 2-to-4 line binary decoder consists of an array of four AND gates. The 2 binary inputs labelled A and B are decoded into one of 4 outputs, hence the description of 2-to-4 binary decoder. Each output represents one of the miniterms of the 2 input variables, (each output = a miniterm).

The binary inputs A and B determine which output line from Q0 to Q3 is "HIGH" at logic level "1" while the remaining outputs are held "LOW" at logic "0" so only one output can be active (HIGH) at any one time. Therefore, whichever output line is "HIGH" identifies the binary code present at the input, in other words it "de-codes" the binary input.

### **Decimal to BCD Encoder**

### **Explanation:**

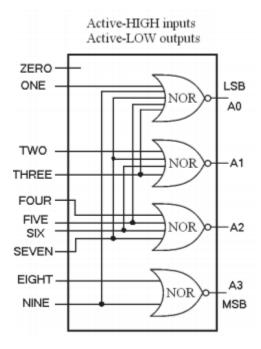

A decimal-to-BCD encoder is a digital circuit that has 10 input lines and 4 output lines. The inputs represent the 10 decimal numbers from 0 to 9, where only one input can be active. The outputs indicate the BCD code that represents the active input. Above circuit shows the logic diagrams of the decimal-to-BCD encoder using NOR gates. For the case of active-H i/ps and active-L o/ps, the logic diagram with NOR gates is used. By adding a SE inverter at the end of each output, one can get active-H o/ps. It can be noted that the encoder needs 1 NOR gate with 2 inputs (which is connected to the MSB output), 1 NOR gate with 5 inputs (which is connected to the LSB output), and 2 NOR gates with 4 inputs (which are connected to the middle two outputs).

## Q1 (d)

#### **Answer:**

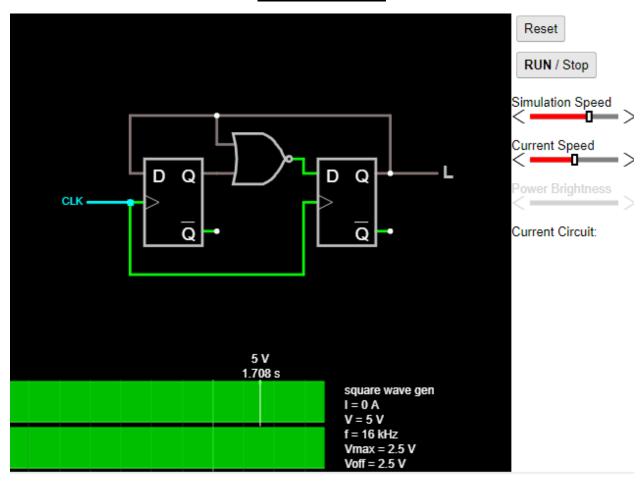

## **Frequency Divider**

This circuit shows how two D flip-flops can be used to divide the frequency of a clock signal by 3.

The truth table of a 4-to-1 multiplexer is shown below in which four input combinations 00, 10, 01 and 11 on the select lines respectively switches the inputs D0, D2, D1 and D3 to the output. That means when S1=0 and S0 =0, the output at Y is D0, similarly Y is D1 if the select inputs S1=0 and S0=1 and so on.

| Select Da             | Output         |                |  |

|-----------------------|----------------|----------------|--|

| <b>S</b> <sub>1</sub> | S <sub>0</sub> | Y              |  |

| 0                     | 0              | D <sub>0</sub> |  |

| 0                     | 1              | D <sub>1</sub> |  |

| 1                     | 0              | D <sub>2</sub> |  |

| 1                     | 1              | D <sub>3</sub> |  |

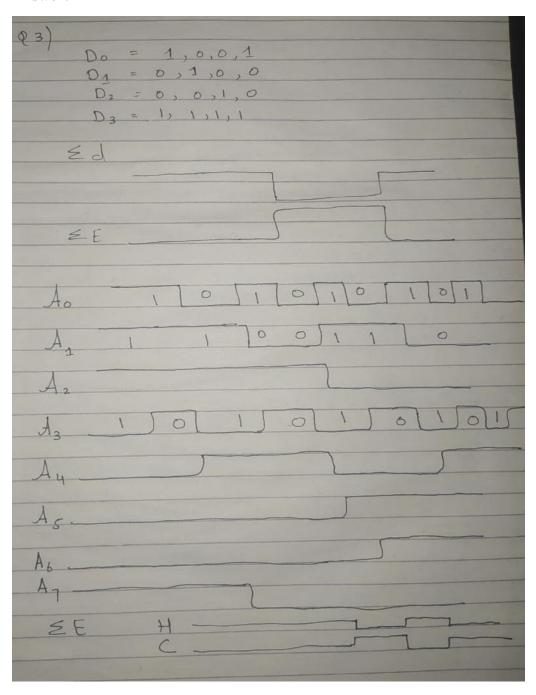

Q3

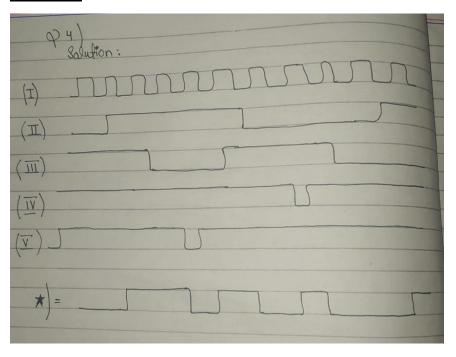

# Q4

# Answer:

# **Q** Output:

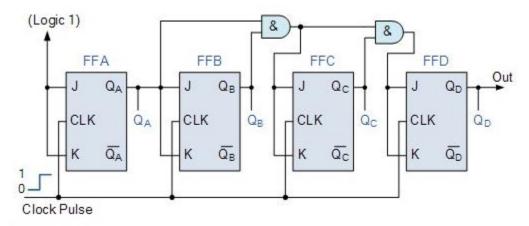

#### **Logic Diagram for 4-stage Synchronous Binary Counter**

#### **Explanation:**

It can be seen above, that the external clock pulses (pulses to be counted) are fed directly to each of the J-K flip-flops in the counter chain and that both the J and K inputs are all tied together in toggle mode, but only in the first flip-flop, flip-flop FFA (LSB) are they connected HIGH, logic "1" allowing the flip-flop to toggle on every clock pulse. Then the synchronous counter follows a predetermined sequence of states in response to the common clock signal, advancing one state for each pulse.

The J and K inputs of flip-flop FFB are connected directly to the output Q<sub>A</sub> of flip-flop FFA, but the J and K inputs of flip-flops FFC and FFD are driven from separate AND gates which are also supplied with signals from the input and output of the previous stage. These additional AND gates generate the required logic for the JK inputs of the next stage.

As there is no inherent propagation delay in synchronous counters, because all the counter stages are triggered in parallel at the same time, the maximum operating frequency of this type of frequency counter is much higher than that for a similar asynchronous counter circuit.

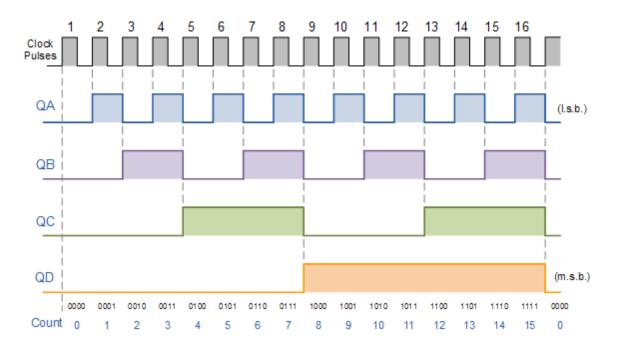

### **Timing diagram for the 4-stage Synchronous Binary Counter**

Because this 4-bit synchronous counter counts sequentially on every clock pulse the resulting outputs count upwards from  $0 \, (0000)$  to  $15 \, (1111)$ . Therefore, this type of counter is also known as a 4-bit Synchronous Up Counter.

However, we can easily construct a 4-bit Synchronous Down Counter by connecting the AND gates to the Q output of the flip-flops as shown to produce a waveform timing diagram the reverse of the above. Here the counter starts with all of its outputs HIGH (1111) and it counts down on the application of each clock pulse to zero, (0000) before repeating again.