## **:: ASSIGNMENT # 3 ::**

**ID:** 11533

Name: Ashir Ali Khan

**Subject: Computer Architecture**

**Teacher: Sir Muhammad Amin**

**Iqra National University**

| ASSIGNMENT: 3:-                                                                                                                                                                                                                                                                                                                                        |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| QUESTION: 1:-                                                                                                                                                                                                                                                                                                                                          |

| Paet: A:-                                                                                                                                                                                                                                                                                                                                              |

| Aniwel 1-                                                                                                                                                                                                                                                                                                                                              |

| Disabling Interrupts:-                                                                                                                                                                                                                                                                                                                                 |

| processor has the ability to and will ignore                                                                                                                                                                                                                                                                                                           |

| the specific interrupts. Those interrupts remain pending and will be checked after the processor                                                                                                                                                                                                                                                       |

| has enabled interrupts.                                                                                                                                                                                                                                                                                                                                |

| Interrupt service routine (ISR):-                                                                                                                                                                                                                                                                                                                      |

| priorities assigned to the different types of                                                                                                                                                                                                                                                                                                          |

| interrupt . Interrupt service routines with                                                                                                                                                                                                                                                                                                            |

| higher phiolities can interrupt ones with                                                                                                                                                                                                                                                                                                              |

| love priority, in which case the ISR with                                                                                                                                                                                                                                                                                                              |

| the lower priority is put on the stack until that ISR is completed.                                                                                                                                                                                                                                                                                    |

| DIC B CONFIE                                                                                                                                                                                                                                                                                                                                           |

| V V                                                                                                                                                                                                                                                                                                                                                    |

| X                                                                                                                                                                                                                                                                                                                                                      |

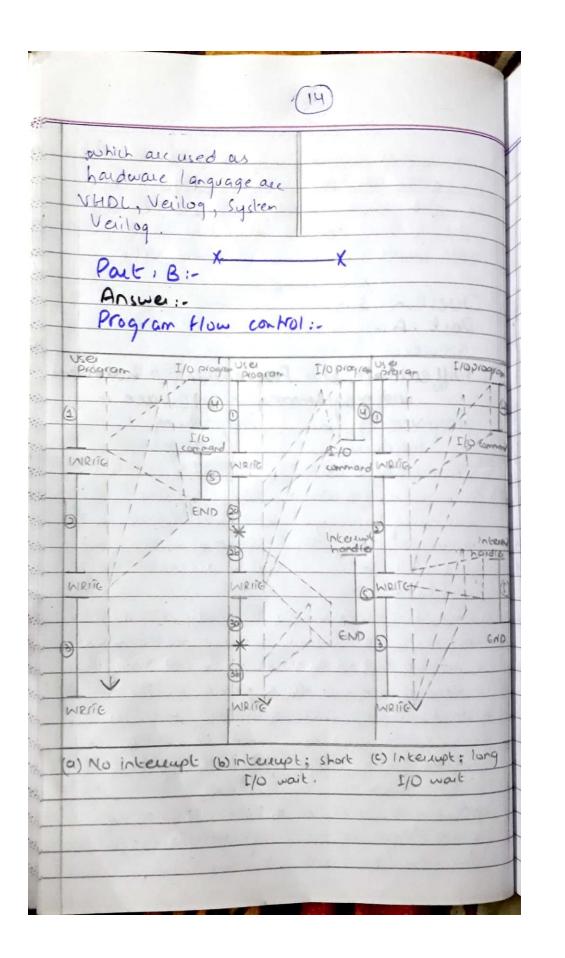

| Paut: B:-<br>Answer:-                                                                                                                                                                                                                                                                                                                                  |

| Paut: B:- X                                                                                                                                                                                                                                                                                                                                            |

| Paut: B:-<br>Answer:-<br>Memory:-                                                                                                                                                                                                                                                                                                                      |

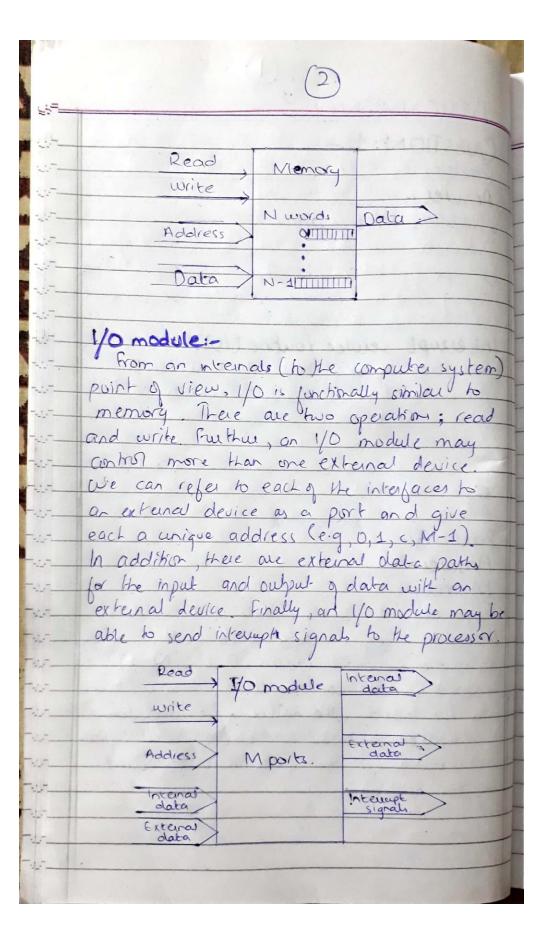

| Part: B:-  Answer:-  Memory:-  Typically, a memory module will consist of  N words of equal length. Each word is assigned                                                                                                                                                                                                                              |

| Paut: B:-  Answer:-  Memory:-  Typically, a memory module will consist of  N words of equal length tach word is assigned a unique numerical address (0,1,c,N-1).                                                                                                                                                                                       |

| Paut: B:-  Answer:-  Memory:-  Typically, a memory module will consist of  N words of equal length tack word is assigned a unique numerical address (0,1,c,N-1)  A word of data can be read from or written                                                                                                                                            |

| Paut: B:-  Answer:-  Memory:-  Typically, a memory module will consist of  N words of equal length tack word is assigned a unique numerical address (0,1,c,N-1)  A word of data can be read from or written  into the memory. The nature of the operation                                                                                              |

| Part: B:-  Answer:-  Memory:-  Typically, a memory module will consist of  N words of equal length tack word is assigned a unique numerical address (0,1,c,N-1)  A word of data can be read from or written  into the memory. The nature of the operation is indicated by read and write control signals.                                              |

| Part: B:-  Answer:-  Memory:-  Typically, a memory module will consist of  N words of equal length tack word is assigned a unique numerical address (0,1,c,N-1)  A word of data can be read from or written  into the memory. The nature of the operation  is indicated by read and write control signal.  The location for the operation is specified |

| Paut: B:-  Answer:-  Memory:-  Typically, a memory module will consist of  N words of equal length tack word is assigned a unique numerical address (0,1,c,N-1)  A word of data can be read from or written  into the memory. The nature of the operation                                                                                              |

| Part: B:-  Answer:-  Memory:-  Typically, a memory module will consist of  N words of equal length tack word is assigned a unique numerical address (0,1,c,N-1)  A word of data can be read from or written  into the memory. The nature of the operation  is indicated by read and write control signal.  The location for the operation is specified |

| Part: B:-  Answer:-  Memory:-  Typically, a memory module will consist of  N words of equal length tack word is assigned a unique numerical address (0,1,c,N-1)  A word of data can be read from or written  into the memory. The nature of the operation  is indicated by read and write control signal.  The location for the operation is specified |

| Part: B:-  Answer:-  Memory:-  Typically, a memory module will consist of  N words of equal length tack word is assigned a unique numerical address (0,1,c,N-1)  A word of data can be read from or written  into the memory. The nature of the operation  is indicated by read and write control signal.  The location for the operation is specified |

Processor:-The processor reads in instructions and data writer out data after processing, and uses control signals to control the overall operation of the system. Bill also receives interupto signals.

| nstructions | NAME OF THE PERSON OF THE PERS | Address >       |

|-------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------|

| Data        | CPU                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                 |

|             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | control signals |

| Intellipt   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Pata            |

Part : Ci-

Answer :-

Quick path Interconnect (QPI) protocol layers:

architecture, 3 encompassing the following layers

Physical :-Consist of the actual wires callying the signal, as well as circuitry and logic to support ancillary features required in the transmission and receipt of the 1s and Os. The unit of transfer at the physical rayer is 20 bits, which is called a phit (physical unit).

link "

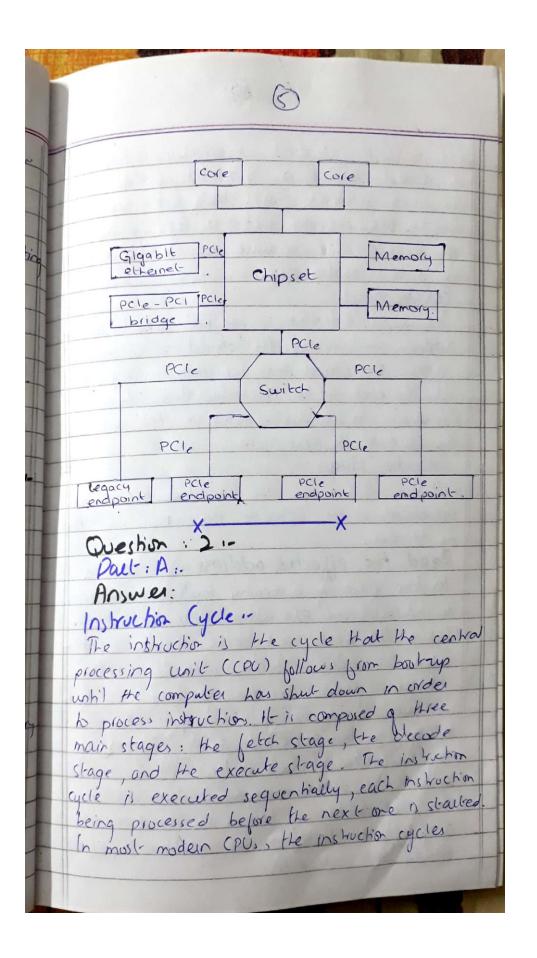

Responsible for reliable Eransmission and fla The control. The link layer's unit of teansfer is an 80-bit Flit ( Glow control unit Routing :-Provides the framework for the dilection packets Grough the pabric. Rest Protocol ~ The high-level set of rules for exchanging packet of data between devices. A packet is comprised of an integral numbers of File Part : D:-Answer: Physical and logical auchitecture of PCles soft complex device, also rejerred to as a chipset or a host bridge, connects the processor and memory subsystem to the PCI Express switch fabilic complising one or more and DCle switch devices. The root complex ach as a buffering devices, to deal with difference in data rater between 1/0 controllers and memory and processor components. The rows complex also translates between PCIE transaction formats and the processor and memos signal and control requirements. The chipset will hypically support multiple Pcle ports, some of which attach directly to a PCIE device, and one or more that attach to a switch that manager multiple pois PCle

streams.

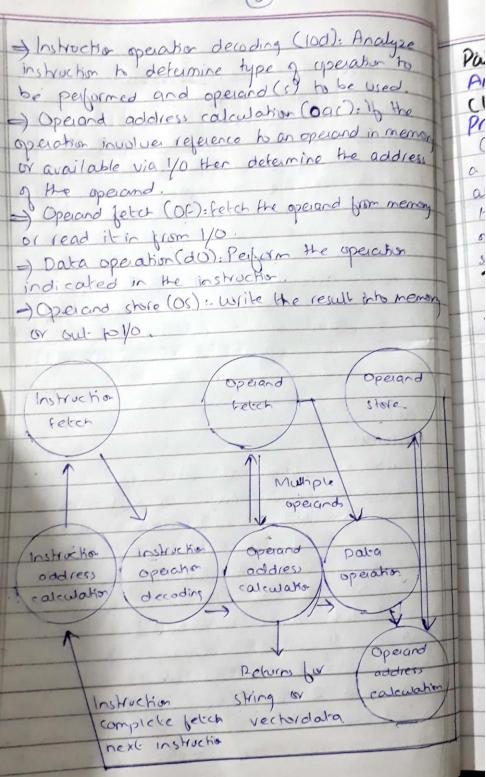

are instead executed concuerently, and great in parallel, through as instruction pipeline: the next instruction starts they being processed before the previous instruction how finished which is possible because the cycle is broken up into seperate steps. Fetch stage: next instruction is fetched from the memor address that is currently shored in the program counter and stored into the instroction register At the end of the fetch operation, the PC points to the next instruction that will be read at the next-cycle Decode stage 1-During this stage, the encoded instruction presented in the instruction register is interpreted by decoder Read the effective address: In the case of a memory instruction (direct or indirect), the execution phase will be during the next clock pulse. If the instruction has a an indirect address, the effective address is lead from main memory, and any required data is fetched from main memory his be processed and Hen placed to register (clock pulse: 1) if the instruction is direct mothing is done during His is an 1/0 instruction or a register instruction , He operation is performed Ordering the clock pulse

(1)

Execute stage:

The control unit of the CPU passes the

decoded information as a sequence of control

signals to the relevant function units of CPU

signals to the actions required by the instruction

such as reading values from registers, passing

them to the All to perform mathematical

or logic functions on them, and writing the

result back to a register. If the All is involved,

it sends a condition signal back to the CU.

The result generated by the operation is shored

in the main memory or sent to an output

device Based on the feedback from the All

the PC may be updated to a different addies.

from which the next instruction will be fetched.

Part: B

mon

eted

Answer:

Determine the address of the next instruction to be executed. Usually this involves adding a fixed number to the address of the previous Instruction, have example, if each instruction is 16 bits long and memory is organized into 16-bit words, then add 1 to the previous address. If instead, memory is organized as individually addressable 8-bit bytes, then add 2 to the previous address.

Instruction fetch (IF): Read instruction from its memory location into the processor.

12 (9) Partici-Answer :classes of interruph. program: Generated by some condition that occurs as a result of an instruction execution, such as alithretic overflow, division by 3010, attempt to execute an illegal machine instruction or refrences outside a user's allowed memory space. Times: Generated by a times within the processor. This allows the operating system to perform certain functions on a regular basis 1/0: rormal completion of a operation or to signal a valiety of elies conditions Generated by a failure such as power failure or memory parity enor Part: D: Answer:-

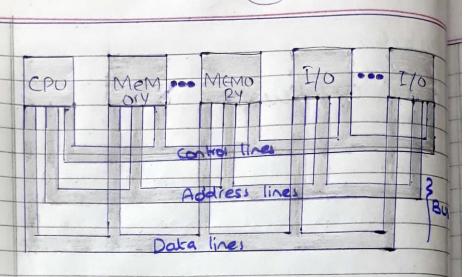

Bus Interconnection Scheme:

## Bus Interconnection Scheme

A bus is a communication pulturay connecting hur or more devices. A key characteristic of a bus is that it is a should transmission median Multiple devices connect to the bus and a signal transmitted by any one device is available for reception by all other devices altached to the bus. of two devices transmit during the same time perilod, their signals all overlap and become garbled This, only one device at a time can successfully transmit Typically, a consist of muliple communicate pathways, or lines. Each line is capable of transmitting signals represents binayo. An 8-bit un be transmitted over eigh lines. A bus that connect major computer components (processor, memory

(10) is called a syclem bus pata lines:-The data lines provide a part for moving data among system moduler. There lines. collectively, are called the data bus Addless lines .-The address lines are used to designate He source or destination of the data on the data bus for example, on an 8-pit address bus, address 011111111 and below might reference locations in a memory module (module 0) with 128 words of memory, and address 10000000 and above refers to devices altached to an 1/0 module (module 1) Control lines :-The control lines are used to control the access to and the use of the data and address lines Control signals transmit both command and timing information among system modules. Timing signal indicate the validity of data and addiess mormation. Command signals specify spe operations to be performed. Typical control lines include: · Memory Write ~ Causer data on the bus to be written into the addressed location. • Memory read : "ourses data from the addressed location to

be placed on the bus

(12) · I/O write 1-Causes data on the bus to be output to the addressed yo port • I/O read: Cause data from the addressed yo port to be placed on the bus · Transfer ACK 1-Indicates that data have been accepted from a placed on the bus · Bus requesti-Indicates that a module needs to gain control of the bus. · Bus grant: Indicates that a requesting module has been granted control of the bus · Interrupt request :-Indicates that an interrupt is pending · Interrupt ACK :-Acknowledges that the pending interrupt has been decognized · Clock 1-Is used to synchronize operations Reset -Initializes all modules. The operation of the bus is as follows, if one module wisher to send data to another it must do two the things, to obtain the use of the bus, and so transfer data via the bus, if one module wishes to request data

from another module, it must obtain the the other module over the appropriate control and address then . It must then wait for Hat second modure to send the douta

Question: 3:-Part: A.

Answer: -

Differentiate blu Programming in hardware Programming in Programming in hardware Software

components specifically a general - purpose for a particular computation

1) Programming in houder in Programming in software are means configuring a means supplying a specific small set of basic logic set of control signals to a haid wave,

2) Hardware programming 2) A software programming 3) Hardware programming 3) Software languages of the circuit. 4) Some of the examples 4) some examples of

9 HOL C'Hardware

Description (anguages)

language all'concurent language aiesegventia in nature and executed in nature and executed a piece of code in paralle a piece of code sequentially languages are used to cannot be used for h find the liming Delay find the liming Delay of PLO circuit somme languages

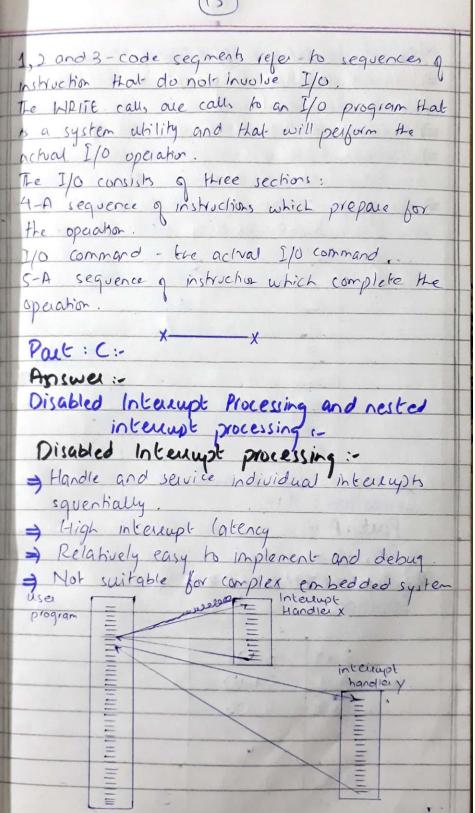

|                         | (16)                                                                                                                     |                                                                                    |

|-------------------------|--------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------|

| Medium or  Frables into | high inter high inter excepts before something the periority  ments  high inter excepts before something  gher periority | eupt latercy eupt latercy we the servicing of his complete. How priority interrupt |

| Answer:                 | ad soveral or                                                                                                            | Da-Ca                                                                              |

| Solution                |                                                                                                                          |                                                                                    |

| 300                     | 3005                                                                                                                     | 1.                                                                                 |

| 301                     | 5940                                                                                                                     |                                                                                    |

| 302                     | 7006                                                                                                                     |                                                                                    |

| •                       |                                                                                                                          | -                                                                                  |

|                         | 2002                                                                                                                     |                                                                                    |

| 940                     | 0002                                                                                                                     |                                                                                    |

| 941 [                   |                                                                                                                          |                                                                                    |

K

| ble will assume that the memory as the                                                           | - |

|--------------------------------------------------------------------------------------------------|---|

| plevious table:<br>300: 3005; 301: 5940; 302: 7006.                                              | + |

| Transforme, the steps will be as the following                                                   |   |

| step 1 : 3005 → 1R                                                                               | 1 |

| Step2: 3 -> AC                                                                                   | - |

| Step3: \$940 -> 12.                                                                              | + |

| $Step^21: 3+1=S \rightarrow AC$                                                                  | - |

| Steps: 7006 -) 12                                                                                | + |

| Step6: AC -> Device 6.                                                                           | 1 |

| Park P. X                                                                                        | + |

| Paet : Bi-                                                                                       | + |

| Answer:-                                                                                         | + |

| Step: 11-                                                                                        | + |

| a) The PC contain 300, the address of the first instruction. This value is loaded in to the MAR. | + |

| b) The value in location 300 (which is the                                                       | 1 |

| instruction with the value 1940 in Hexadecima)                                                   | 1 |

| is loaded into the MBR, and the PC is                                                            | 1 |

| incremented. These two steps can be done in                                                      | 1 |

| parallel.                                                                                        | 1 |

| c) The value in the MBR is loaded into the .                                                     | T |

| Step: 2:-                                                                                        | 1 |

| a) The address portion of the IR (940) is loaded                                                 | T |

| into the MAR.                                                                                    |   |

| b) The value in location 940 is loaded into the                                                  |   |

| MBK                                                                                              |   |

| c) The value of in the MBR is loaded into the                                                    |   |

| AC                                                                                               |   |

|                                                                                                  |   |

|                                                                                                  | - |

| Step. 3 -                                                                                           |

|-----------------------------------------------------------------------------------------------------|

| a) The value in the PC (301) is loaded in to the                                                    |

| MAR                                                                                                 |

| 6) The value in location 301 (which is the                                                          |

| instruction with the value 5992/ 15 october 100                                                     |

| the MRR and the PC is incremental                                                                   |

| of The value in the MBR is loaded into the                                                          |

| IR.                                                                                                 |

| Skep: 4:-                                                                                           |

| a) The paddless portion of the IR (941) is loaded                                                   |

| Into the MAR                                                                                        |

| b) The value in location 9410 is loaded into                                                        |

| the MBR                                                                                             |

| of the old value of the He and the value of                                                         |

| The old value of the AC and the value of the location MBR are added and the result is the AC        |

| SIGHT AM ILS                                                                                        |

| Step: S :-                                                                                          |

| a) The value in the PC (302) is loaded in to the                                                    |

| b) The value in location 302 (which is the instruction with the value 2941) is located into the MBR |

| with the value 2941) is loaded into the MRR                                                         |

| The safe                                                                                            |

| of the value in the MBR is loaded into the                                                          |

| 1K                                                                                                  |

| Step: 6 "                                                                                           |

| a) The address perhan of the IR (941) is loaded                                                     |

| THE TOTAL                                                                                           |

| b) The value in the AC'Is loaded into the MBR.                                                      |

| of The value in the MBR is stored in location                                                       |

| 1942                                                                                                |

|                                                                                                     |

Part: Cr-Answer:-(A) what is the maximum directly addressable memory capacity (in bytes)? = 16,777, 216 bytes = 161MB (8 bits = 16/14 for he opcode) (B) Discuss the impact on the system speed if He microprocessor bus has: (b.1) 32-bit local address but and a 16-bits local data bus, or. A 32-bit local address bus and a 16-bit Iscal data bus Instruction and data transfer would lake three by cycle each, one for address and two for the data. Since if the address bus is \$32 bits, the whole address can be transfered to momory at once and decoded there; however, since the data bus is only 16 bits, it will require 2 2 bus cycles to jetch the 32-bit instruction or operand (6.2) 16-bit local addiess but and a 16-bit local data bus A 16-bit local address bus and a 16-bit local data bus. Instruction and data Gansfer. would take four bus cycles each, his for the address and two for the data. Therefore that will have the process or perform

two transmission in order to send to memory (as the whole 32-bit address; this will repuire more complex memory protectace control to latch the two halver of the address refore it performs an access to it. In addition to this two-steps address issue, since the data bus is also \$16-bib, the microprocessor will need 2 bus cycles to fetch the 32-616 instruction or operand. () How many bits are needed for the program counter and the instruction registers For the PC needs 24 bits (24-bit addresses) and for the IR needs 3)-bits (32-bit ) addiesses) Part: D:-Answer ,-Since minimum bus cycle docation = 4 clock and bus clock 8MH2 Then, maximum bus cycle rate = 8M/4 Data transferred per bus cycle = 16 bit = 2 bytes Data transfér rate per serond - bus cycle rate x data per bus cycle = 21Mx2 4 Mbytes/sec To increase its performance: · By doubling the frequency, It may mean adopting a new chip manufacturing technology

(assuming each instruction will have the same will number of clock cycles). · By doubling the external data bus that means wider (may be never) or chip - data diwers latches and modifications to the control logic Therefore in the first situation the speed of the memory chips will need to double, not to slow down the micropraessor. Regarding the second silvation, the word length of the memory will must double to the able to send / Leceive 32-bit grantities Partie:-Answer:-(A): - Through a a single bus cycle, the 8-bit microprocessor transfer one byte while the 16-bit micropiaessor Gansfei two bytes. The 16-bit microplacessor has hvice the data transfer rate (B) By assuming that we have to perform 50 transfer of operand and instructions which 25 are one byte long and 25 are two bytes long. The 8-bit microprocessor needs 25+(2×25)=75 bus cycles for the transfer The 16-bit microprocessor needs 25+25=50 bus cycles. Therefore, the data transfer lates differ by a factor of 1.5

Part: F:-Arswer:lime taken to fetch the operands: hirst we need to find the time taken to fetch one speand from one memory location frequency and bus cycle. rate = 4MH2 Given clock Frequency clock Rate 4MH2 = U.25 Ms Therefore, brequery or bus cycle & O.S.Ms Then, imemory are cycle will take DISHSXY - 1 Ms. Hence the fetch one operand from memory 1Ms is required By applying this " If an odd-aligned word is rejevenced, two memory of cycles each consisting of four bus cycles, are required to transfer the word " from the Question, so we will have 3 cases. First case :- is if bothe operands are even-aligned, so He time required is to jetch both operand. Second case:-is if both operands are oddaligned, so the time required is IXY=4Ms to letch both operands.

Third case :- is if only one is odd-aligned. so the time required is 1x3 = 3 Ms to felch both operands X Partig: Solution :-By assuming that we have a mix of 100 instructions and operands from the question: 20% of the uperand and instructions are 32bits long, soit is DD BO 32-bil-40% of the operand and instructions are 16bits long, soil is 40 16-bit 401 of the operand and instructions are only 8bih = 1 byte long, so it is 40 bytes. The number of bus cycles receded for the 16-bit microprocessor will equal to: (20x2)+40+40 - 120 bus cycles The number of but cycles needed for the 32-bit microprocessor will equal to: 20+40+40 - 100 bus cycles By calculating the improvement achieved with 32-bit microprocessor to the 16-bit millopraessor will equal to 20/120=16.6%