# Digital Logic & Design (Lab)

### Name: Changaiz khan

### ID: 13206

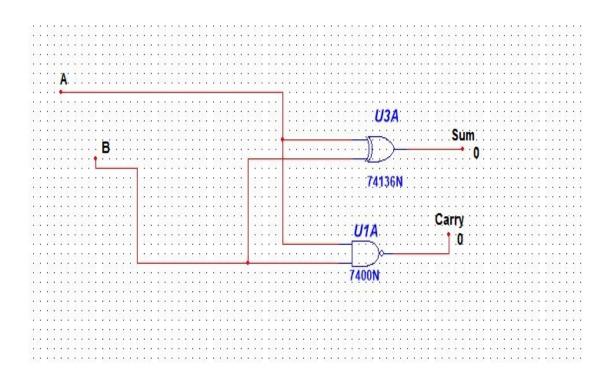

**Q.1** Design and verify the logic circuit for the following:

(a) Half adder using logic gates

| INPUTS |   | OUTPUTS |       |  |

|--------|---|---------|-------|--|

| A      | В | SUM     | CARRY |  |

| 0      | 0 | 0       | 0     |  |

| 0      | 1 | 1       | 0     |  |

| 1      | 0 | 1       | 0     |  |

| 1      | 1 | 0       | 1     |  |

From the equation, it is clear that this 1-bit adder can be easily implemented with the help of EXOR Gate for the output 'SUM' and an AND Gate for the carry. Take a look at the implementation below

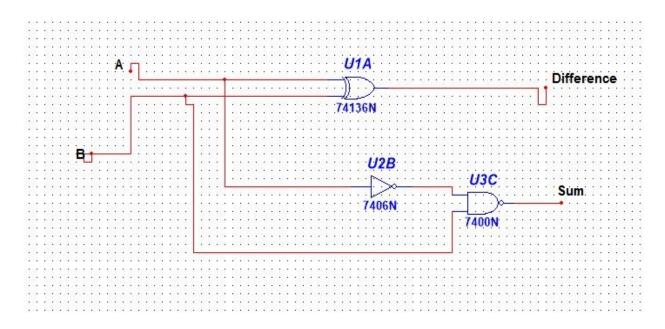

#### (b) Half-subtract or using logic gate

## **Truth Table**

The half subtractor truth table explanation can be done by using the logic gates like EX-OR logic gate and AND gate operation followed by NOT gate.

| First Bit | Second Bit | Difference<br>(EX-OR Out) | Borrow<br>(NAND Out) |

|-----------|------------|---------------------------|----------------------|

| 0         | 0          | 0                         | 0                    |

| 1         | 0          | 1                         | 0                    |

| 0         | 1          | 1                         | 1                    |

| 1         | 1          | 0                         | 0                    |

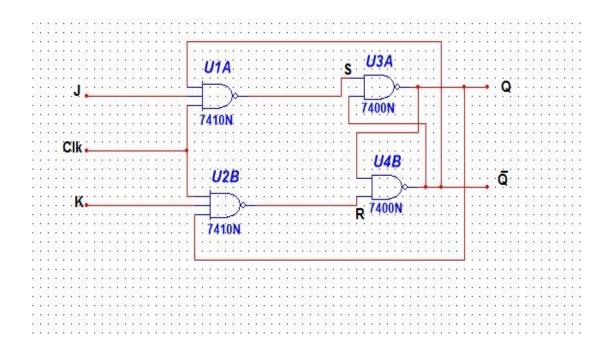

(c) J K Flip flop

The Truth Table for the JK Function

|                    | Clock | Inj | put    | Out | tput      | Description |

|--------------------|-------|-----|--------|-----|-----------|-------------|

|                    | Clk   | J   | K      | Q   | Q         | Description |

|                    | X     | 0   | 0      | 1   | 0         | Memory      |

| same as<br>for the |       | 0   | 0      | 1   | no change |             |

| Jk Latch           | _↑_   | 0   | 1      | 1   | 0         | Reset Q » 0 |

|                    | X     | 0   | 1      | 0   | 1         |             |

|                    | _↑_   | 1   | 0      | 0   | 1         | Set Q » 1   |

|                    | X     | 1   | 0      | 1   | 0         |             |

| toggle             | _↑_   |     | Tagala |     |           |             |

| action             | _↓_   | 1   | 1      | 1   | 0         | Toggle      |

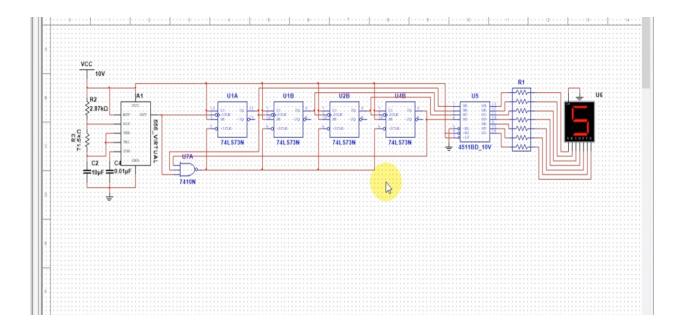

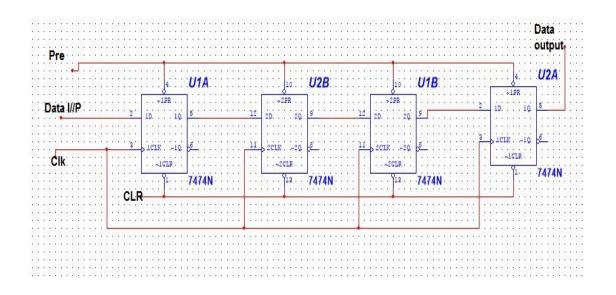

(d) Serial in-serial Out shift register

# TRUTH TABLE:

| CLK | Serial in | Serial out |

|-----|-----------|------------|

| 1   | 1         | 0          |

| 2   | 0         | 0          |

| 3   | 0         | 0          |

| 4   | 1         | 1          |

| 5   | X         | 0          |

| 6   | X         | 0          |

| 7   | X         | 1          |

## (e) Synchronous BCD Counter