Name: Muhammad Musa

Department: BS(CS)

Semester: 4th

*ID* # : <u>15366</u>

Sessional Assignment No : 4th

Subject: Computer Architecture

Submitted To: Muhammad Amin Sir

Dated: 13th June 2020

Tape units are sequential access. (x) Direct Access As with sequential access. direct access involves a shared write mechanism. However, individual blocks or records have a unique address based on Physical location. Access time is variable. Dist units are direct (x) Random Access: The time to access a given location is independent of the sequence of prior occesses and constant. Thus, any location can be selected at random and directly addressed and accessed. Main memory and some cache systems are random access. \* Associative Access: This is a random access type of memory that enables one to make a compasison of desired bit locations within a word for a specifical match, and to do this for all words simultaneously. Thus, a word is retrieved based on a postion of its contents rather them its address. Cache memories may employ associative access.

Ans: (iii) Importance of Memory hierarchy: errors the hierarchy such that the percentage of accesses to each successively lower level is substant ially less than that of the level above. · The three forms of memory just described are volatile and employ Semiconductor technology. The use of these levels exploits the fact the semiconductor memory comes in variety of types, which differ in and the semiconductors. variety of types, one cost. "Secondard memory or auxiliary memory are used to store program and data files and age usually visible the programmer only in terms of files and rewich. Ans: (in Slower also less expensive memory utilized within higher stoges for the majority expensive continously segisters in the processor additionally reserve. Fundamental memory be slower and less expensive furthermore will be outside of Processor.

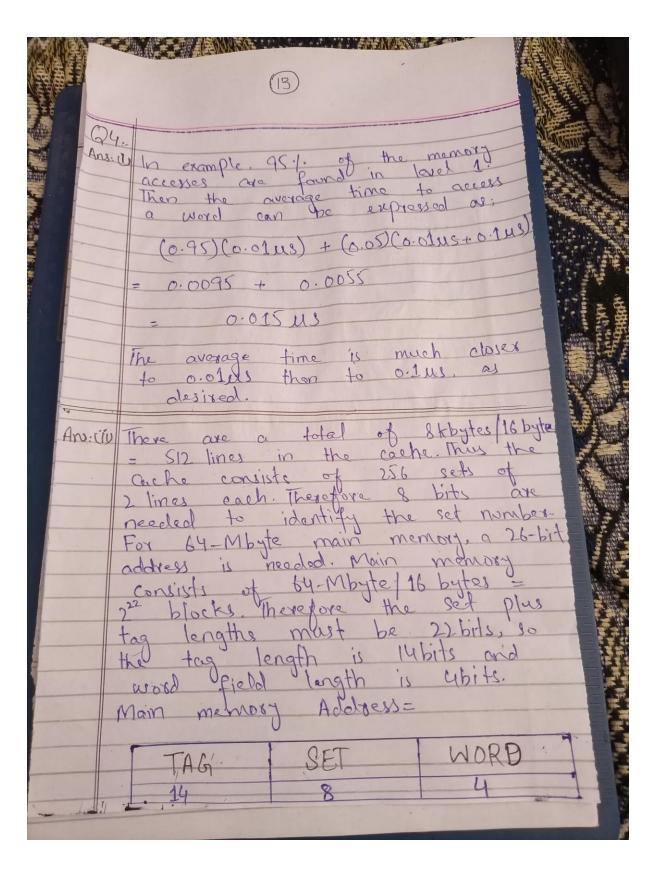

4 Answy Dixect Mapping - Simplest techniques. known direct mapping, maps each block of main memore one possible cache line. The mapping is expressed os: = j modulo m Associative Mappings Associative mapping overcomes the disadvantages of mapping by permitting each memory block to be loaded any line of the cache-In this case, the cache control Logic interprets a memory address simply as a Tag and a word Set-Associative Mapping VSet-Associative mapping is a compromise that strengths of both the direct and associative approaches while reducing their disadvantages. case, the cache consists In this number sets, each of which of a number of The relationships are = Vxk = j modulo v

(3) 02 Ans. is Memory Unit Iranstes: numbers Oxead out into memory at of transfer need teans an addressab memory. ransfersed Performance Parameters: Ansitis Memory two most important 05 chasacteristics and performance. Three performence 1. Acres Time; For random-access memory this is the time perform a read or wei is, the time from that are address is presented the memory to the instant the data have for use for nonavailable access memory, access time is position the read the desired write mechanism at location.

(6) Primarily applied to random-access memory and consists of the access time plus any additional time required before a second access ban commence this additional time may be required for transient to die out on signal lines or to regenerate date if they are read alestructively. Note that memory cycle time is concerned with the stefan bus, not the processor. system bus, not the processor. This is the sate at can be transferred into or out of a memory unit For random-access memory, it is equel to 1/(cycle time). For nonrandom-access memory; Ansitiil Disk Cache: Jisk Cache improved pexformance in two ways: Disk writes are clustered. Inst of many small toansfer of data, we have a few large transfers of data. This improves dist porformance and minimizes processor involvement.

7 8 data destined for write-ou be referenced by a program before the next dump to disk. In that case, the data are setoieved In that Rapidly from the software cache than slowly from the disk cache Ans: civi Principle of Locality: principle of states that data a referenced word are to be referenced in the future. An implication of locality is that we can predict with reasonable accuracy what instauctions and data. a program will use in the near the recent post. Cache and Physical Cachen Ans: (V) Logical cache also known as a vistual cache, stores using virtual addresses. The processor using virtual adolesses. The processes accesses the cache directly, without going through the MMU.

A physical cache stores data using main mamory physical addresses.

Advantage of logital cache is that cache access speed is fasted than for a physical eache, because

(8) the cache can respond before the MMU performs an address translation.

The disadvantage has to do

with the fact that most violual

memory systems supply each

application with the game virtual address space. Answij Replacement Algorithms: The cache has been filled, when a new block is into the cache existing blocks mapping, there possible line for any post block, and no choice is the associative and set-associative techniques, a replacement algorithm is needed. To achieve high speed. such an algorithm must implemented in hardware. Answij Possible approaches to Cache Cohesency: Possible approaches to coherency include the following · Bus watching with write through Each cache controlles monitors the address lines to detect other operations to memory ous masters

10 read-write mechanism. However, individual blacks or records have a unique actories based on physical beation.

Access is accomplished by direct

access to reach a foreral

vicinity plus seapential georgahing to

counting as waiting to reach the

final location. Random Access Each addressable location has a unique physically in memory how a with mism. wised-in adolessing mechanism. time to access a given location independent of the seguence of independent of the seguence of and is constant. 20100 Angio direct mappine technique is simple and mexpendive to implement its main disadvantage block. Ihus, hennen from two repeated tine. Associative ith associative mapping block to when a new

(11) block is read into the cache Replacement algorithms, discussed in thin Section. are designed maximize the hit setio. The disadvant aga is that the complex circuity of all cache lines in parallel. Set-Associative Mapping: For set-associative mapping the cache control logic interprets a memory address as three fields: Tag, bet and Word. The diset bits specify one of The of set birts specify one of V = 2d sets. With fally a set - associative mapping, the tag in a memory address is much smalles and is only compared to the k tags within a single set. "giii) Split Cache and Unified Cache:

> Has become common to split Ans: Cacho: . One dedicated to instructions. . One dedicated to data. . Both exist at the same level. typically as two L1 caches. -> Advantages of Unified Cache:

- Higher hit rate because it balances the load between instruction and data feather automatically.