NAME: AMIT SINGH

ID: 15478

SUBJECT: DIGITAL LOGIC DESIGN

SEMESTER: 3<sup>RD</sup>

PROGRAMME: BS (SOFTWARE ENGINEERING)

Q1) - 00 Do Po Q CIK DC C Q. 101 UK 2 1 3 Cherkpuse 4 Q. Qi Initially 00 01 Q. 2 ā. 0 34 Ø 0 0 92 Q. Do -D Q. 0 Do Uk Q2 Q Q. Q 8 3 6 1 ŀ 2

2 G3) CIK 9. Qi 82 The worst case delay occurs on CLK - Q. Qy) CLK 90 QI Q2 3(8ns) = 24ns

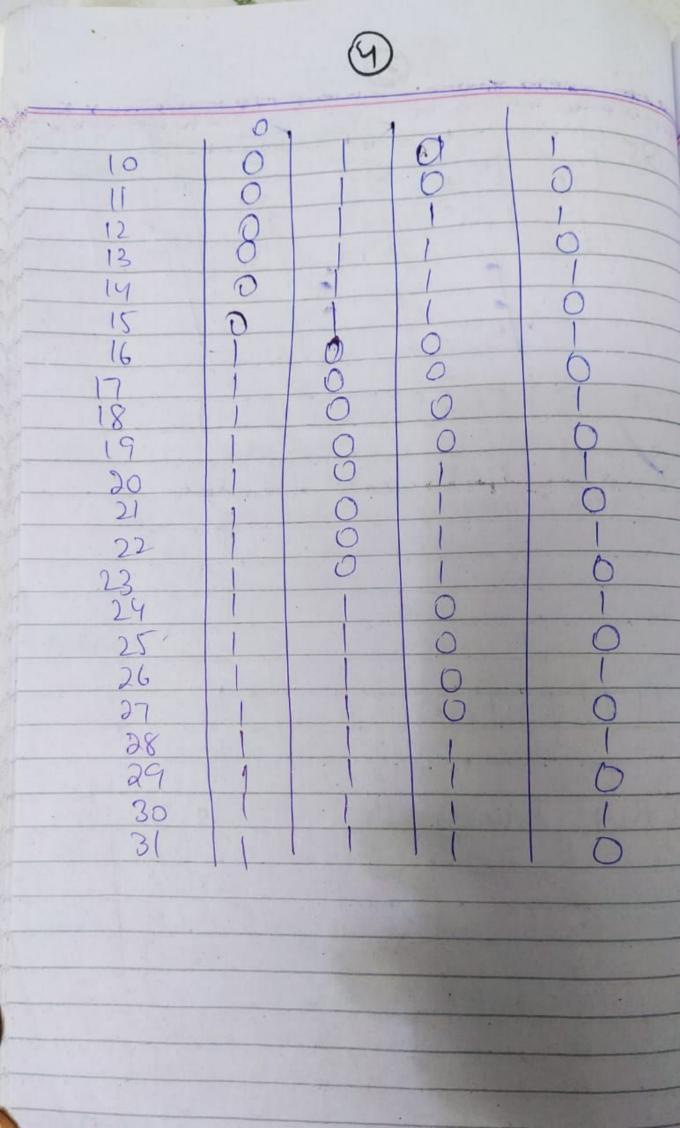

3 195 Sic Q JI 0 In Js C RQ Ĩ4 C CLK 100 4 like K3 1cy Clk 0. 0 02 03 Qu CRUSE Intrally QI Q3 豆 0 00 00000 2000 2 0 3.456 õ 0 000 0 800 0