## **:: ASSIGNMENT # 4 ::**

**ID:** 11533

Name: Ashir Ali Khan

**Subject: Computer Architecture**

**Teacher: Sir Muhammad Amin**

**Iqra National University**

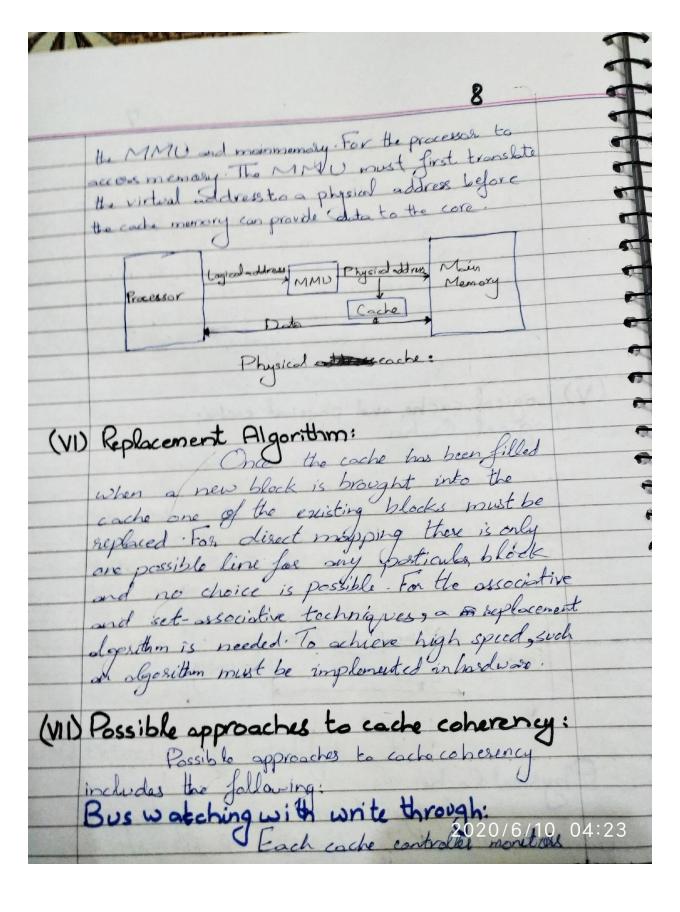

Q2 Write note on each of the following: (i) Memory unit of transfer: of bits that can be read as written into the memory at a time, In case of main memory, It is mostly equal to wordsize. In case of external memory, unit of transfer is not limited to the wordsize. It is often longer and is reflered to as blocks: (11) Memory performance parameters: of memory are capacity and parameters performance. Three performance parameters are used: Access time (latency): is the time it takes to perform a read of welte sposition that is, the time from the instant that an address is presented to the memory to the instant that the data non-random- access memory, access time is the time it take to position the read-minited mechanism at the desired location. Temory cycle time: This concept is primarily applied to random-scens memory and consists of the access time plus any additional time required before a second access commence. This additional time may be required

the address lines to detect write operations to memory by other bus mosters. If another moster writes to a is shored memory that also resides in the cache the cache controller invalidates that cache entry. This depends on the use of a write through policy by Mache antrollers Hardware transparency all upolities to min memory via all caches. There if one processor modifies a west its caches this update is written to main memory In addition any natching words in other cache are similarly Non-cacheable memory: Only a postion of non-cocheable memory can be identified chip select logic or high address bits 2020/6/10 04:23

|                                                                                                                                                                | A    |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

| 14                                                                                                                                                             | 7    |

| Therefore no of cache lines is 512 since its two way associative the cache consists of 2 set each consists of 256 cache lines.                                 | 4    |

| associative the cache consists of 2 set each consists of                                                                                                       | 10 1 |

| - Number of bits nequired for set field in main money address format is 8-bits because 2 = 256  - Second step is to calculate number of blocks in main monosy: |      |

| monory address format is 8-bits because 2 = 256                                                                                                                | -    |

| · Second step is to conculate number of blocks in                                                                                                              | -    |

| mainmemosy:  Juntes of blacks in mainmenting = 64MB                                                                                                            | •    |

|                                                                                                                                                                |      |

| $-2^{4} \times 2^{26} \times 2^{3}$ $2^{4} \times 2^{3}$                                                                                                       |      |

| = 2 <sup>22</sup> blocks-                                                                                                                                      |      |

| There for the set plus tag must be of 22 bits 350                                                                                                              |      |

| Therefor the set plus tag must be of 22 bits 350 the tag length is 14 and the word length is 49 bits:                                                          |      |

| is 40 bits:                                                                                                                                                    | 0    |

| Mainmemory address = 14 8 4                                                                                                                                    |      |

|                                                                                                                                                                | •    |

| (110 F 4 .                                                                                                                                                     |      |

| (iii) For the main                                                                                                                                             | •    |

| Solotion                                                                                                                                                       | •    |

| Address (H) BBBBBB                                                                                                                                             | 9    |

| Address (Binasy) 10111011101110111011                                                                                                                          |      |

|                                                                                                                                                                |      |

| b Tog (22) / Lord (2) 2 EFEEH / 3H<br>c Tog (9) Set (13) / Lord (2) 177H / OFEEH / 3H                                                                          |      |

| 1 2 Mord (13) Mord (2) MITH OFEEH/3H                                                                                                                           |      |

|                                                                                                                                                                |      |