Haroon Rashid

Reg# 16549

Semester: 6<sup>th</sup>

Major Assignment: DLD Final Term

Submitted to: Sir Muhammad Amin

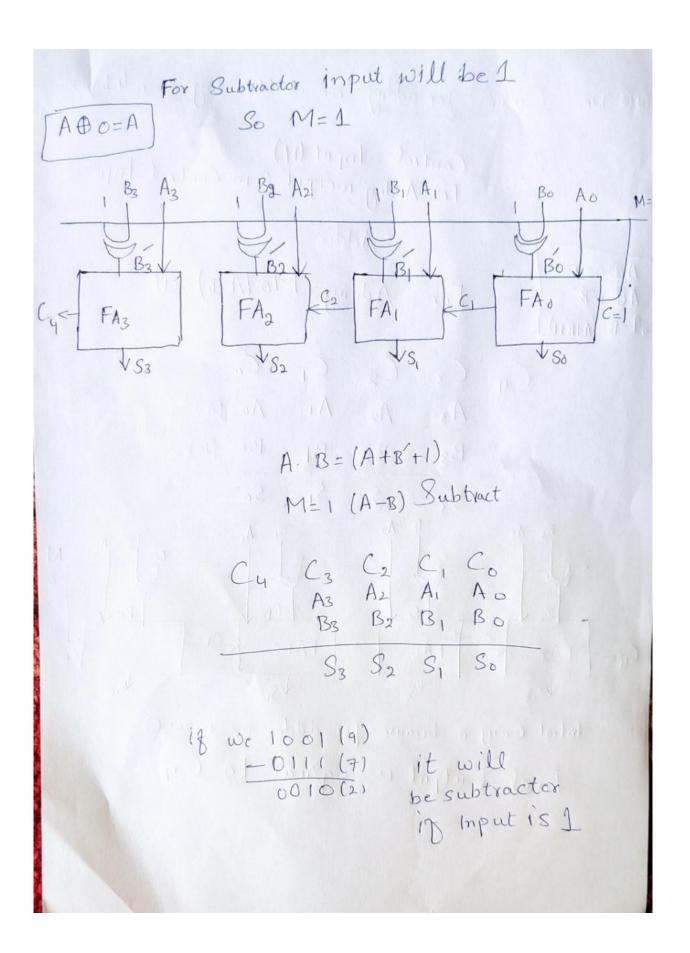

Quan Circuit for adding or subtracting two 4 bits number Control Input (M) For Adding welmput O in Control Input Addex For Adding Mo (A+B) add ADO-B A 1=B A-B=(A+B+1) C4 C3 C2 C1 C0 A3 A2 A1 A0 (A) Two

B3 B2 B1 B0 (B) Two S3 S2 S1 S0 Ca FAI Intial Carry= 0 because for adder we input () Final Output is equal to Cy

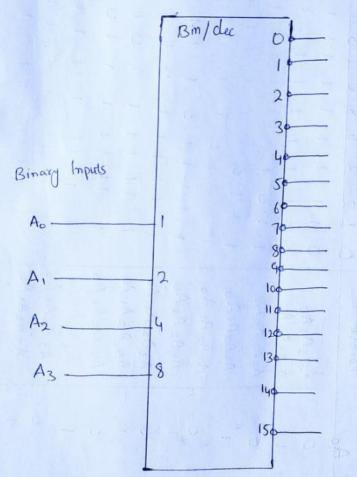

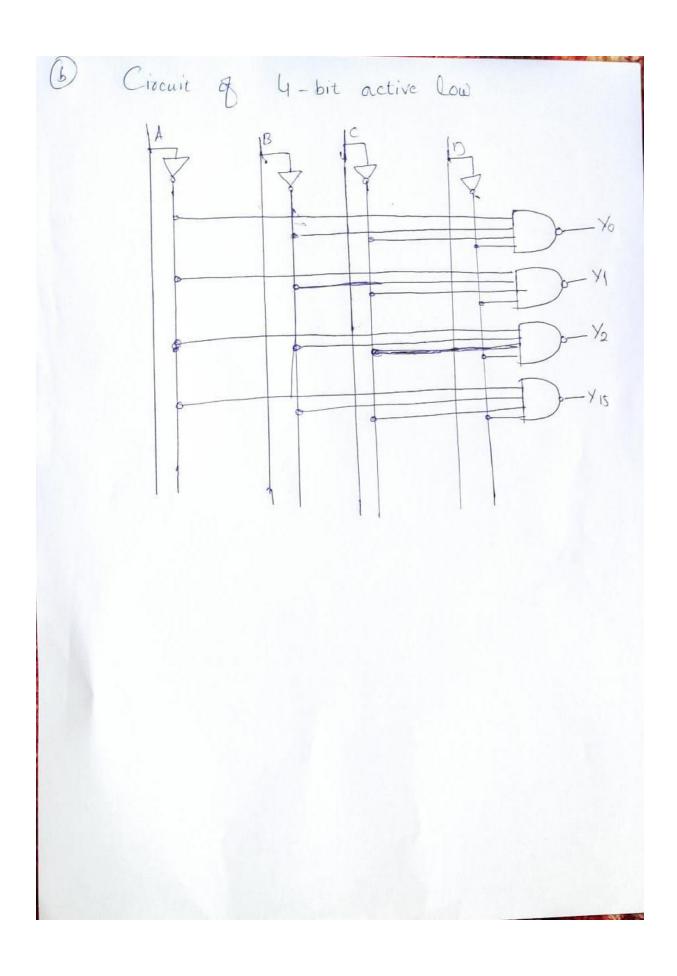

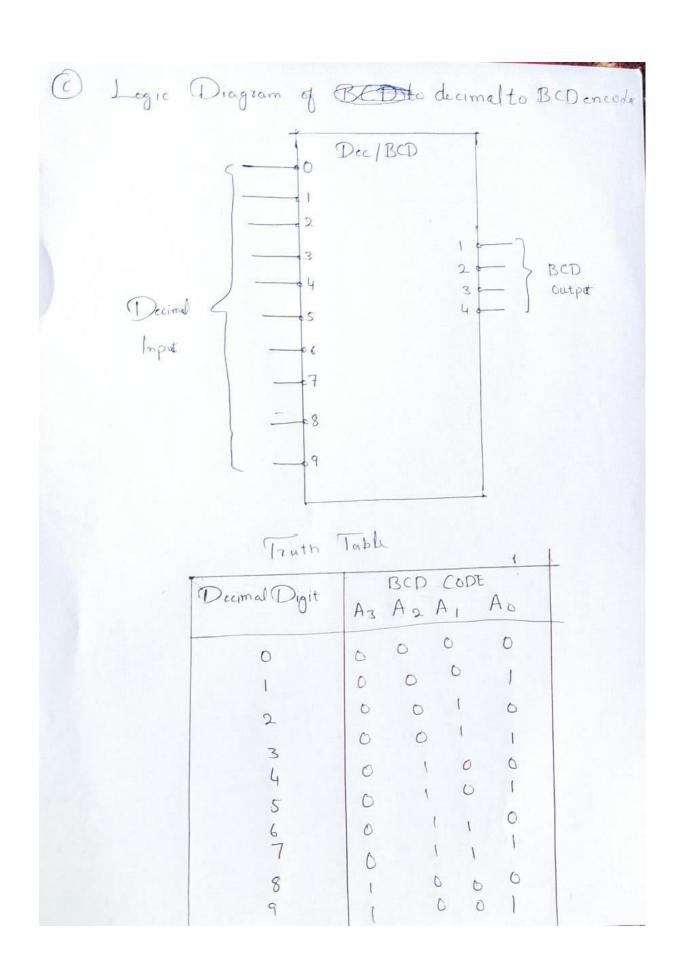

b) Draw a circuit of 4-bit active low decoder

4- bit Decoder for Active low

Binary Inputs Ao, A, , A2, A3

In an actowactive - Low output is required for each decoded number, the entire decoder can be implemented with NAND gates & inventers.

| Decoc   | ding Junctions & t                                          | ruth table 19             | · 4-bit activ-Low decodes Outputs       |

|---------|-------------------------------------------------------------|---------------------------|-----------------------------------------|

| Decimal | Binary Inputs                                               | Decoding                  | Outpus                                  |

| Digit   | A <sub>3</sub> A <sub>2</sub> A <sub>1</sub> A <sub>0</sub> | Function                  | 0 1 2 3 4 5 6 7 8 9 10 11 12 13 14 15   |

| 0       | 0 0 0 0                                                     | A3A2A1A0                  | 01111111111111                          |

| Ī       | 0 0 0 1                                                     | ĀzĀzĀI AO                 | 101111111111111111111111111111111111111 |

| 2       | 0 1 0                                                       | A3 A2 A1 A0               | 110111111111111111111111111111111111111 |

| 3       | 0 0 1 1                                                     | A3 A2 A1 A0               | 1110                                    |

|         | 0 1 0 0                                                     | A3 A2 A1 A6               | 11110                                   |

| 4 5     | 0 ( 0 1                                                     | A, A, A, A                | 1 1 1 1 1 0 1 1 1 1 1 1 1 1 1           |

| 6       | 0 1 1 0                                                     | A3 A2 A1 A0               | 111111011111111                         |

| 7       |                                                             | A3 A2A, A0<br>A3 A2 A, A0 | 111111111111111111111111111111111111111 |

| 8       |                                                             | A3 A2 A1 A0               | 1111111110111111                        |

| q       | 000                                                         | A3 A2 A, A0               | 11111 111111111111111111111111111111111 |

| 10      | 0 1 6                                                       | A3 A2 A1 A0               | 1 1111 11 111                           |

| 11      | 1 0                                                         | A 3 A2 A1 Ac              | , , ,, ,, ,, ,, ,, ,, ,, ,, ,, ,, ,, ,, |

| 12      | 1 0 6                                                       | A3A2ĀIA                   | 0 , 11 11 11 1 1 1 1 1 1 1 1 1 1 1 1    |

| 13      |                                                             | A D A2 A IAI              | 6 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 |

|         | 1 1 1                                                       | A3 A2 A A                 |                                         |

| 15      | 1                                                           | 13.11                     |                                         |

|         |                                                             |                           |                                         |

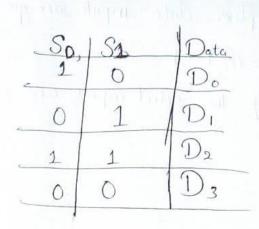

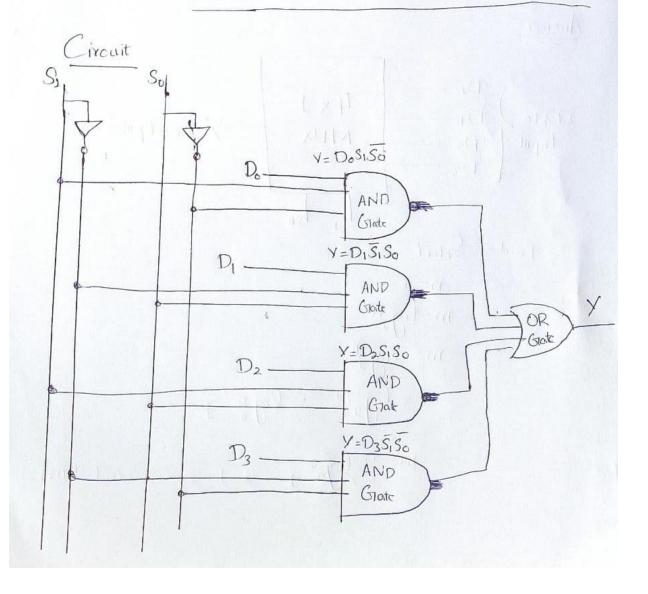

Q2 For the 4-Input multiplexa, data inputs are given

$$D=0$$

,  $D_1=1$ ,  $D_2=0$ ,  $D=1$

Find the Output  $Y$  if the Select inputs are given as

a)  $S_0=1$ ,  $S_1=0$

$S_0=0$ ,  $S_1=1$

$S_0=0$ ,  $S_1=0$

Answer

Data

$$\begin{cases} D_0 \\ D_1 \\ D_2 \\ D_3 \end{cases}$$

Hux  $\begin{cases} Y \text{ (output)} \\ Y \text{ (output)} \end{cases}$

Find  $\begin{cases} S_{\text{clust}} \\ S_{\text{ines}} \\ Y \text{ (output)} \end{cases}$

$\begin{cases} S$

$$\begin{array}{c|c} \hline D_{ata} & Output(Y) \\ \hline D_o & \\ \hline D_1 & \\ \hline D_2 & \\ \hline D_2 & \\ \hline D_3 & \\ \end{array}$$

Q3- Timing diagram in Figure 01 Shows input to a 9-bit parity checker. Draw the E Even & Eadd output for the even parity checker

Answer - Parity Chick The combinational circuit at the received is the parity checker. This checker takes the received message including the parity bit as input. It gives output 'I' there is some error found & gives output in Output's it no error is Jound in the message including the Parity Lit.

Parity Checker

Even Parity

Checker

Checker

Even Parity Checker: In Parity Checker it

the error bit (E) is equal to 1, then we have

an error bit E=0 then indicates there is

no error.

Error Bit (E)= 1, error occurs

Error Bit (E)=0, no error

Odd Parity Checter.

In odd parity checker it an error bit (E) is equal to 12, then it indicates there is no matter error. It an error bit E=0 then indicates there is an error Error Bit (E)=1, no error

Error Bit (E)=0, error occurs.

The parity checker worst be able to deted it there are errors in more than '1' bit I the correct of data is also not possible, these are the main disadvantages by the parity Checker.

The below table Shows the truth table for the even parity checker in which PEC=1 if the error occurs, i.e, it cold number of Is PEC=0 if no error.

|       | The T | / |     |   |                      |

|-------|-------|---|-----|---|----------------------|

| * - A | *     | В | C   | P | Parity error chud Cp |

|       | 0     | 0 | 0   | 0 | 0                    |

|       | 0     | 0 | 0   | 7 | 1                    |

|       | 0     | 0 | 1   | 0 | 1                    |

| -     | 0     | 0 |     | 1 | 0                    |

| ~     | 0     |   | 0   | 0 | 1                    |

|       | 0     |   | 0   | 1 | 0                    |

| 1     | 0     |   | 1   | 0 | 0                    |

|       | 0     |   | 1   | 1 | J                    |

|       | 1     | 0 | 0   | 0 | 1                    |

|       | 1     | 0 | 0   | 1 | 0                    |

| -     | 1     | 0 |     | 0 | Ō                    |

| 2     | 1     | 0 |     | 1 | 1                    |

|       |       |   | 0   | 0 | O                    |

| -     |       |   | 0   | 1 |                      |

| -     | , 1   | 4 | 1   | 0 |                      |

|       | - 1   |   | , 1 |   |                      |

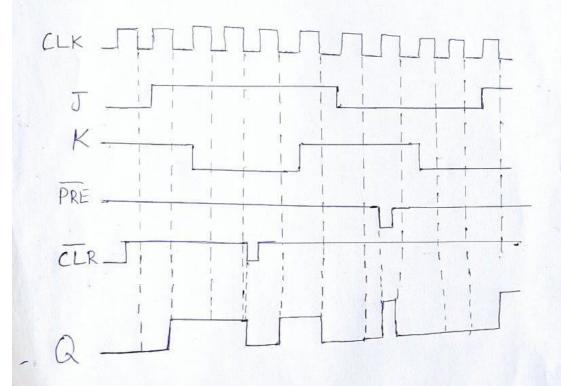

Q4. The waveforms in Figure 02 are applied to the J,K, CLK, PRE, & CLR inputs as indicated. Determine the Q output, if the Flip-Flop is Initially Reset.

Answer:

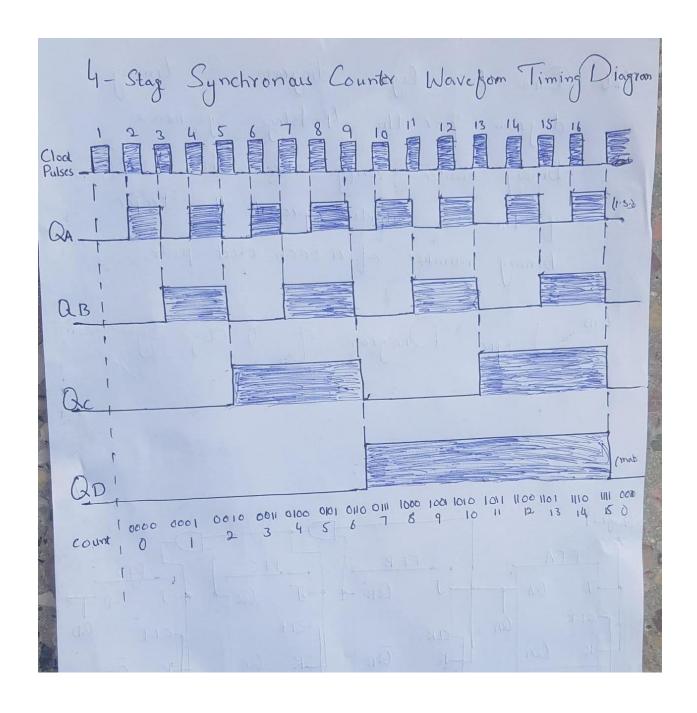

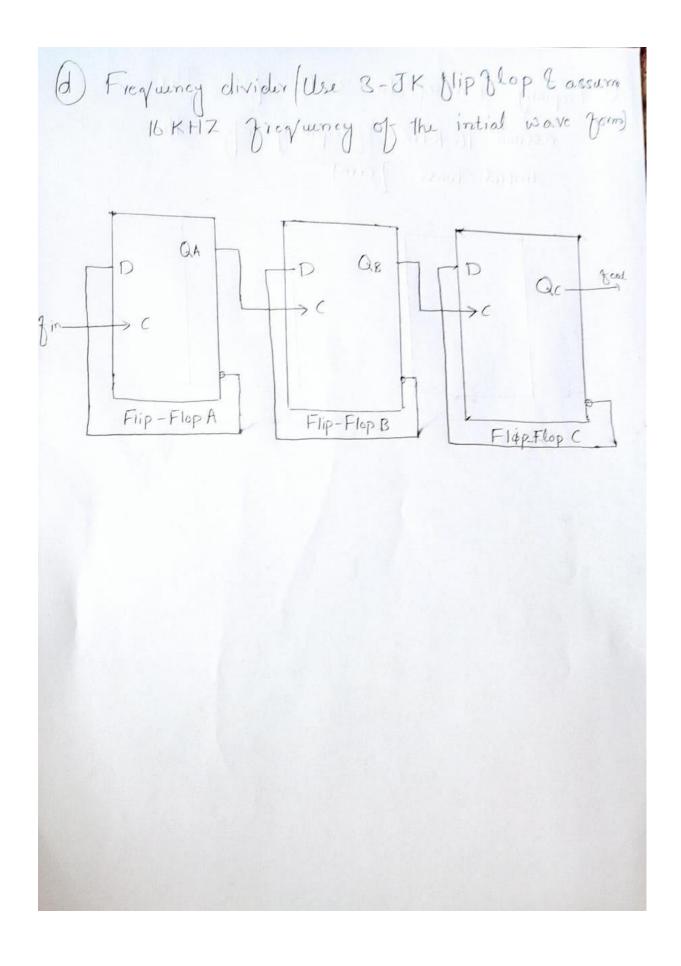

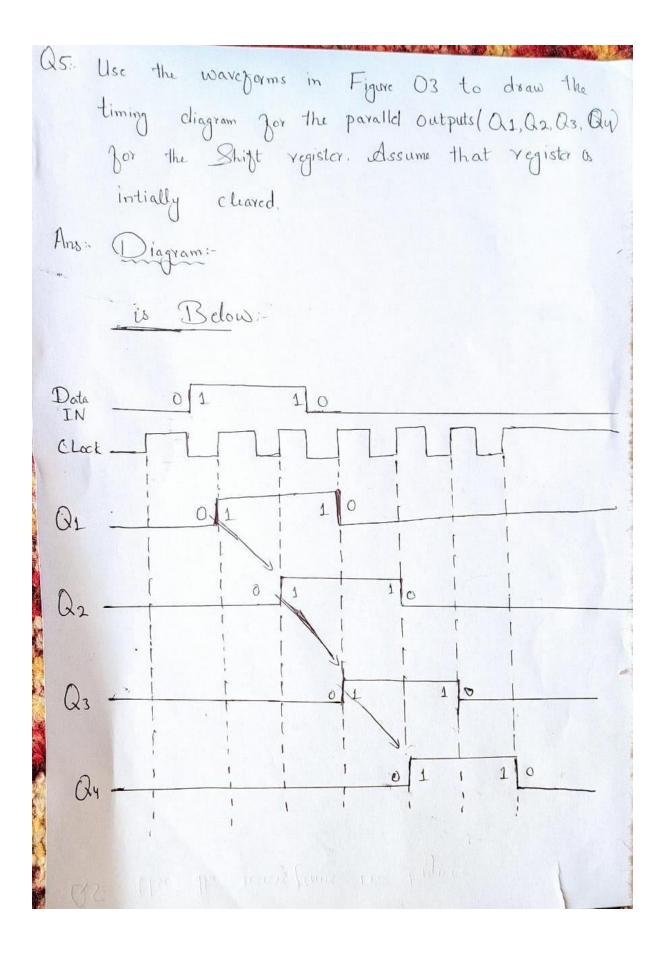

Qb: Draw the logic diagram & timing diagram for the 4-1stage Synchronous binary Counter. Verify that the wave Jams of the Q outputs represent the Proper binary number after each clock puls. Logic Diagram of 4 Stage Synchrony (L99 k1) 4-Stage Synchrous binary Country