#### Department of Electrical Engineering Mid-term

Date: 24/08/2020

#### **Course Details**

| Course Title:<br>Instructor: | Electronic Circuit Design <u>Dr Sheharyar</u> | Module: Total Marks: | 6th<br>30 |

|------------------------------|-----------------------------------------------|----------------------|-----------|

|                              |                                               |                      |           |

#### **Student Details**

Name: <u>Talha Khan</u> Student ID: <u>13845</u>

Student Signature:

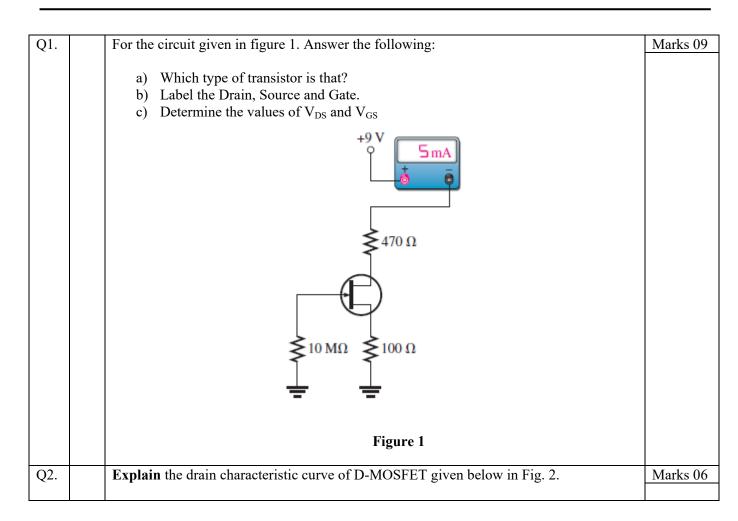

|     | ID(mA) Ohmic Saturation Region $V_{GS} = +0.5V$ $V_{GS} = 0$ $V_{GS} = -0.5V$ $V_{GS} = -1.0V$ $V_{GS} = -2.0V$ $V_{GS} = -2.0V$ Figure 2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |  |

|-----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

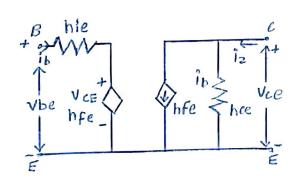

| Q3. | <b>Sketch</b> the hybrid equivalent for common emitter transistor. Write equations for the transistor in common emitter configuration.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |  |  |

| Q4. | Explain why both types of MOSFETs have an extremely high input resistance at the gate. (Marks 01)  In what mode an <i>n</i> -channel D-MOSFET with a positive <i>V</i> GS is operating? (Marks 01)  Why must the gate-to-source voltage of an <i>n</i> -channel JFET always be either 0 or negative? (Marks 01)  Briefly discuss that how BJT differs from FET? (Marks 04)  MOSFET is also called IGFET, give reason why? (Marks 01)  Why JFET is called Squared Law Device? (Marks 01)  What can be the main disadvantage of common-base amplifier as compared to the common-emitter and emitter-follower amplifiers? (Marks 01) |  |  |  |

# Page (1)

Q(I)

Ans:-

(a) This is a PNP Transistor.

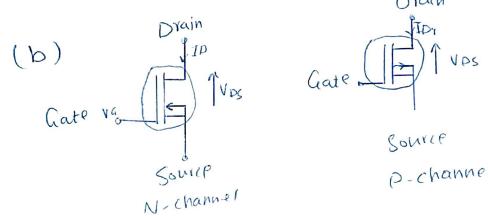

Orain O-channel

## page (2)

page (3)

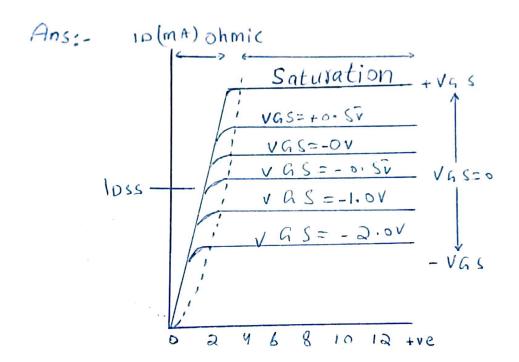

Q(2)

Characteristic Curve of Pepletion Mode MOSFET page (4)

Drain(D)

Drain(D)

Cate value (S)

Source (S)

N-Channel

This characteristic mainly gives the relationship between dain-source voltage (VDS) and drain current (ID).

The small voltage at the gate controls the current flow through the channel. The channel between drain and source acts as a good conductor with zero bios voltage at gate terminal.

# page (5)

The Channel width and drain current increases if the gate voltage is Positive and these two (channel width and drain current) decreases if the gate voltage is negative.

Cut-off Region:

If the gate-source

voltage is less than the threshold voltage then we say othat the transistor is operating in the cut-off region.

(i.e fully OFF). In this region drain current is zero and the transistor acts as an open chait.

VGS < VTH => IDS = 0

# page (6)

Saturation Region:- In this region

the gode voltage is much greater than threshold voltage and the drain current out its manimum value and the transistor is in fully (ON) state. In this region the transistor acts as a closed circuit.

UGS > 7 VTH and (Vas - VTH) 2 VDS C 2 (Vas - VTH)

=> 1DS = Manimum

The gate voltage at which the transistor (ON) and starts the current flow through the Channel is called threshold voltage.

# Page (7)

ohmic Region:

If the gate is

greater than threshold voltage

and the drain-source voltage

lies between VTH and (Vas - VTH)

then we say othat the transistor

is in linear region and at the state

the transistor acts as a variable

resistor.

Vas>VTH and VTH < VDS < (VGS - VTH) =>

MOSFET acts as a Variable

resistor.

# page (8)

This threshold voltage value range for N-Channel devices is in between 0.50 to 0.70 and for P-channel devices is in between -0.50 to -0.80.

The behavior of a mosfet transistor in depletion and enhancement modes depending on the gate voltage is Summarized as follows.

| MOSFET TYPE                  | Vas = + VE | Vas=0 | Vas=-VE |

|------------------------------|------------|-------|---------|

| (1) N - Channel Depletion    | ON         | ON    | OFF     |

| aIN - Channel<br>Enhancement | οN         | off   | o FF    |

| (31 P-Channel Depletion      | off        | ON    | oN      |

| [4] P-Channel Enhancement    | FF (       | OFF ( | D N     |

|                              |            |       |         |

# page (9)

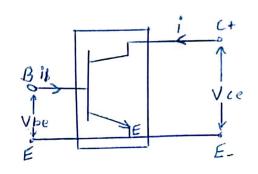

Q(3)

Ans:-

In Common emitter transistor configuration the input signal is applied blue the base and emitter terminals of the

#### page (10)

transistor and output appears between the collector and emitter terminals. The input voltage (Vbe) and the output current (ie) are given by the following eq.

Vbe = hie . 1b thre . Vc

ie = hfe.ib + hoe . Vc

Current Gain:

It is given by the relation

Ai= - (hfe/(1+hoe. TL))

where & is the A.C load resistor. Its value is equal to the parallel combination of Resistance Rc and RL. Since here of a transistor is a Positive number, therefive A; of a Common emitter amplifier is negative

### Page (11)

Input Resistance:

The resistance looking into the amplifier input terminals (i.e base of a transistor) is given by the relation.

Rishiethre. Ai. r. = hie-((hre. hfe)/(hoe+(1/r.)).

The input resistance of the amplifier

Stage (called Stage input resistance Ris)

depends upon the biosing arrangement

For a fixed bias circuit, the Stage input

resistance is,

Ris=RillRB

If the circuit has no biasing resistances then Ris=Ri.

# Page [12)

Voltage Gain:

It is given by the relation,

Av=Ai.va/Ri

Since the current gain(Ai) of a common emitter amplifier is negative, therefore the voltage gain(Av) is also negative. It means that there is a Phase difference of 180° blu the input and output. In other words, the input signal is inverted at the output fo a common emitter amplifier. The voltage gain, in terms of h-parameters, is given by the relation.

Av= hfe. Y1/Chie+ dh. rL) where

Dh= hie . hoe - hre . hfe

## Page (13)

Output Resistance:

The resistance looking into the amplifier output terminals is given by the relation,

Ro= (Rs+hie)/(Rs. hoet Dh) where

Rs= Resistance of the source, and

Dh= hie . hoe - hre . hfe

The so output resistance of the stage,

Roe = RollrL

The output resistance

Overall Voltage Gain:

Av= (Av. Ris)/(Rs + Ris)

Overall Current Gain:

Aie = Aj - Rs/(Rs + Rjs)

# page (10)

Q 4

Explain why both type of MOSFETs have an extremely high input resistance at the gate.

Ans:-

Cate rests on a thin oxide layer over the Source-drain Channel. The oxide layer, effectively a dielectric, acts as a capacitor and isolates gate and rest of the Substrate body, Source, Ovain and Channel. Honce no connection exists between gate and rest of the Parts, which means input impedance of a MOSFET is very high.

# page (16)

Q(4)

In what mode an n-channel D-MOS -FET with a positive vas is open operating?

Ans:- The enhancement-mode.

Qui why must the gate-to-source voltage of an n-channel JFET always be either o or negative?

Ans: The gate-to-source voltage of an n-channel JFET must be zero or negative in order to maintain the required reverse bias condition.

### Page (16)

Q(u) Briefly discuss that now BJT differs from FET?

Ans:-

BJT and FET are two different kinds of transistor and also known as active semiconductor devices.

BJT is a Bipolar Junction transistor and FET is a Field Effect transistor. The major difference between BJT and FET is that, in a field effect transistor only majority charge carries flows whereas in BJT both majority and minority charge carriers flows.

# Page (17)

Q(4) MOSFET is also called IGFET, give reason why?

The Insulated-Gate Field-Effect

Transistor (IGFET), also known as the

Metal Omide Field Effect Transistor

[MOSFET), is a derivative of the

Field effect transistor (FET). Today,

most transistors are of the MOSFET

type as components of digital

integral circuits.

Qui why JEET is called square

# Page (18)

Ans:-

con The input-output toansfer Chavacteristic of the JFET is not as straight forward as it is for the BJT.

(2) In a B)T, R(hFE) define the relationship between IB (input current) and Ic (output current).

(3) In a SFET, the relationship bla Vas (in Put voltage) and Io (out put current) is used to define the transfer.

(u) As a result, FET's are referred to a square law devices.

# page (19)

0(4)

(7) Ans:-In the common base amplifier configuration the input current exceeds all other current, including the output current, the current gain of this amplifier is actually less than 1.