| Department of Electrical Engineering<br>Assignment<br>Date: 14/04/2020 |                           |                             |          |  |  |

|------------------------------------------------------------------------|---------------------------|-----------------------------|----------|--|--|

|                                                                        | <u>Course Details</u>     |                             |          |  |  |

| Course Title:<br>Instructor:                                           | Electronic Circuit Design | Module: _<br>Total Marks: _ | 04<br>30 |  |  |

|                                                                        | Student Details           |                             |          |  |  |

| Name:                                                                  | syed M zahoor             | Student ID: _               | 12595    |  |  |

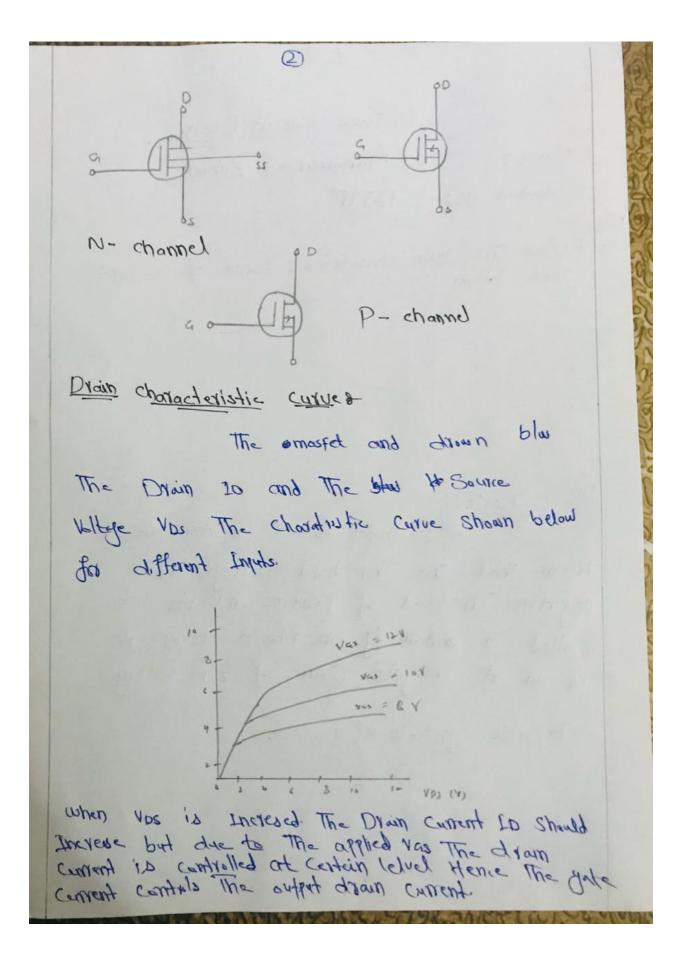

| Q1. | (a) | <b>Explain</b> the drain characteristic curve of D-MOSFET given below.                                                                                                                                                                                                                                                                                                                                         |                               |

|-----|-----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------|

|     |     | $I_{D(mA)}$ $V_{GS} = +0.5V$ $V_{GS} = 0$ $V_{GS} = -0.5V$ $V_{GS} = -0.5V$ $V_{GS} = -2.0V$ | CLO 1                         |

|     | (b) | <b>Sketch</b> the hybrid model and write equations for the transistor in common emitter configuration.                                                                                                                                                                                                                                                                                                         | Marks<br>06                   |

| Q2. |     | A certain operational amplifier has a common mode gain of 0.6 and an open loop differential voltage gain of 400,000. <b>Evaluate</b> the CMRR & express it in decibels.                                                                                                                                                                                                                                        | CLO 1<br>Marks<br>05<br>CLO 2 |

| Q3. | (a) | <b>Explain</b> the concept behind negative feedback in operational amplifiers.                                                                                                                                                                                                                                                                                                                                 |                               |

|     | (b) | <b>State</b> the following statement as <b>True</b> or <b>False</b> and also give the reason for your answer:<br>"The output of a summing amplifier is positive"                                                                                                                                                                                                                                               | Marks<br>06<br>CLO 2          |

Electronic Circuit Design Name & Sted Muhammad Zahoot Student 10:- 12595 Qa @ Explain The drain characteristic curve of D-Mosfet given below. b (ap) saturation region Vas +va Yes= 0.54 - VUSED Ipsi ] YM=-VC 4 6 8 10 12 Vps L .....) Ans D-MOSFET?-A D-moster is a deplition moster mean that the threshold vollage is negative Instead of positive and its abo Called a somermally on Mosfet because it is on at a gate Source of Zero vollage. Schematic Stanbols of D-Mosfet: aste substrate 22 G 50 Source

3 Q1 Sketch The hybrid model and write equations for 6 Anso The transistor in common emitter configuration In The common emitted of The configuration The Input Signal is applied between The base and emitted terminals of the times timesites and The output appels blu The collector and emitter terminals. The input Untege (vse) and The output current (ie) are given by The following equ. Vbe= hie= ib +hie. Vc ie = hfe. ib +hoe. vc (on figuration:-B 16 Tran W B hie 4.1

Q

$$G_{1}$$

$A_{02} = Open loop differential voltage grain

$= 460,000$

$common mode grain = Acm = 0.6$

$find :=$

$cMRR = p$

$Siddian$

$We know that

$cMRR = 20 \log \left(\frac{A_{01}}{Acm}\right)$

$= \frac{A_{02}}{Acm} = \frac{40.000}{0.6}$

$= 66.666.64$

$= 20 \log (66666.66)$

$CMRR = 94.44 dB Ans$$$

6 00 (A) Explain The concept behind negative feedback In operational amplifiers. Anso Negative feedbacks-It is The Process where It is The process where If a Portion of The output voltage of an amplifies is returned to the Input with with a those angle that sposes (or Subtract from) The Input Signal. concept behind The negative feedback= Negative feedback is The process of Seedback a Fraction of The output Signal back to The Input but to make The feedback negative we must feed it back to negative or Investing output. terminal of the opening using an externinal feedback connection resultor Called Rf. This feedback connection blue the output and The Investing inputs terminal force The differential Input voltge toward Jaro. 210 Rih Veat vih

6 (03) @ State The following Stademin as True or falle also given the reason for you answer: The output of a Summing amplifier is Positive" Any-The symming Amplifies is another type of operational amplifier count configuration that is used to combine the voltage present on two a more Input toto a Single output ultige. The Statement is false because when The Summing point is connected to The inverted Input Pf The op-amp The circuit will produce the negative Sum of any number of Input Voltage likewise when the Summing Input is Connected to the non Inverting Input of the om-amplified it will produce The Positive Sum of The Stright villages. Quertanal +tegni 1941/2002. in birrs deglar