## :: FINAL TERM ASSIGNMENT ::

**ID:** 11533

Name: Ashir Ali Khan

**Subject: Computer Architecture**

**Teacher: Sir Muhammad Amin**

**Iqra National University**

Question: (a) Discuss the concept of word addressable units, and brit of for internal memories. FOR INTERNA Memory: nory, the w bits. To clarify this point ese related concepts for Word - The "nativo to the instruct mately there are the CRAY CGO has sord length but uses a 46-bit representation. The Inde x 86 20,20,45,450 4.6-48

has a wide variety of instruction length expressed as multiples of layles, an expressed as multiples a word size of 32 bits ADPREMANCE UNITE: - In some systems the addressable units is the work many systems allow addressing byte level. In any case, the relationship between the tempth bits A of an address and the number NI of addressable units is 2 = NI UNIT OF TRANSPER: - For main mersory, this is the number bits read out of or written into memory at time. The transfer need not egua addressable unit - For word for an merrory, data are often transfered external in much larger units than la word, and these are referred to as backs -) FOR GETCENAR MEMBEY: - Uswally black which is much larger than can be veguely addresse

Word intentionally Closter on M\$ disks. QUESTION: (b) How least recently used (LRU) and less the trequently used (LFU) replacement door a door that are implemented for a cache memory with two-may set associative mapping? GAST RECENTLY USED (LRU):-Replace the black in the set that has been in the cache largest with no reference to it. For two-way set associative, this is easily implemented. Each line includes a USE bit- inthon a line is reflerenced il-25 USE bit is sel to 1. and the USC bil- of other line in that set is set to Mhon of black is to be read into the set, the line whose USE bit is O'b used we are assuming that more recently used menory locations are of

the best hit ratio. LRU is relatively east Frequently Used (LFU):-LFU could be implanented by associating a counter with each technique not bossed on usage (i to pick a line of nat rapdom rep provide only slightly interior par P37-0

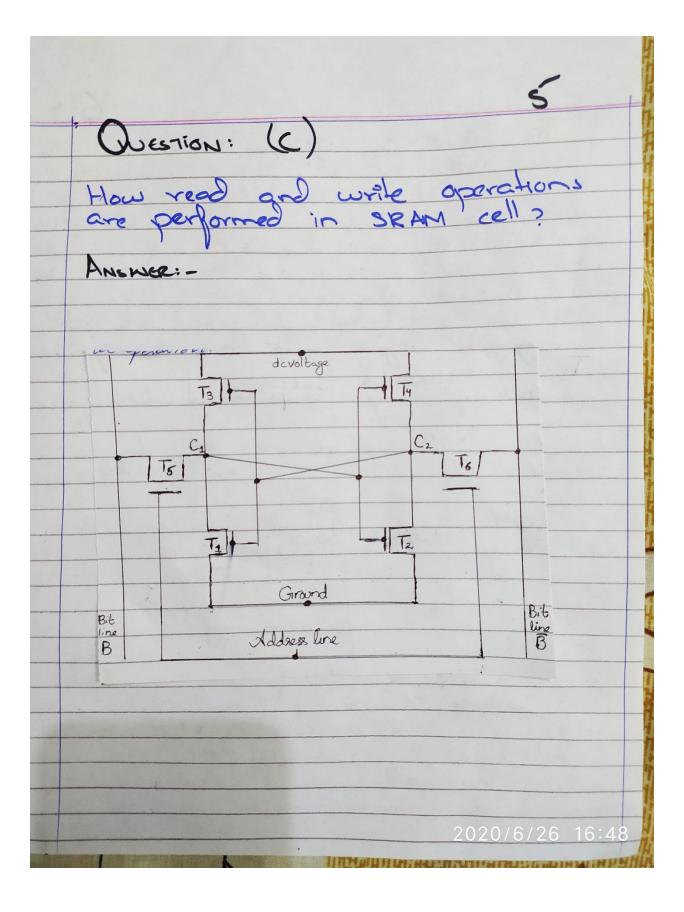

This signe is a typical SRAM struct pr an individual cell. Four transis LT2, T2, T3, T4) are cross cornected arrangement that produces a s edo logic state 1, point and (z point is low; in this and Ty are of and To and To a and point (2 is high; in this and Trand Trans In and by are on off. Both states are stable as long as the direct correct (de ) voltage is and Unlike the DRAM, no regrest is preeded to retain data. The SRAM laddress line is used to open or close a swith The address line Controls two transistors (Ts and Ts) ! Whong signal is applied to the line of he two transistors are switched or allowing a read or write operation. for the with operation of voltage signal is applied to the bit line; high voltage represents I and a voltage apacitor 15 fede out represen On the signal is then applied to addres line, allowing a transferred to the capacitor 2020/6/26 16:49

for the read operation, when line is selected, the transistor from the cell discharges +1 QUESTION: (d) Discou the 16-Mbit DRAM (4M x4) organization in detail.

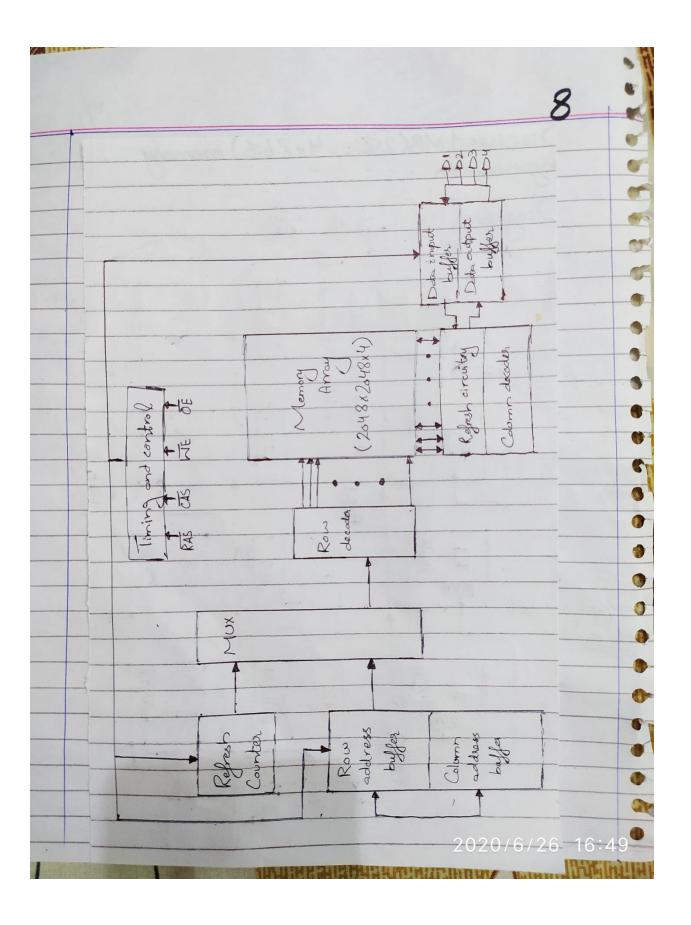

In the case of othis diagram: 4 bits are read or written at a time - Memory array is organized as four arrays 2048 by 2048 ctements > Address lines sopply the address of > log 2 IN lines are needed E. & : 11 address lines are needed to select one of 2042 rows.) These lines are fed into a row decoder, The same procedure is applied to select coloms. - Male that there are only 11 address lines Half the number you would expect a N2048 - 2048 array First, a row address select (RAS) to define the row address of A second a colono adres bela toldfine the column address of Nrite anable (NE) signal specifies that a winde opportion

-) signal specifies that a read operation is to be performed, Petreshing technique -Refresh (ounter: step through all of Memory row is chosen TRAS Pine is activated -) Data are read out and written into the same location. VUESTION: (2) What are the reasons for DUD's greater capacity over CD: The DUD's greater capacity is fue to three differences from CDs. 1. Bits are more packed closely on a DUD. The spacing between words of a co is 1-6 mm

minimum distance between the pit along the spiral is 0.834 mm. The DVD bses a laser with shorter u -length 3 achieves a loop spacing of 0.74mm 3 a minimum Distance bet the pit of 0.4mm. The result of these two improvements is about a seven fold-increase in capacity, to about 4-768 2.) The DUD employs a second layer of pits & lands on top of first layer. A down layer DUD has a semi reflective layer on top of the replactive layer, 3 by adjusting folus, the lasers in DUD drives can read each layer separately This technique almost doubles the capacite of the disk, to about 8.5 GB. The lower replactivity of the second layer limits it's storage capacity so that a full doubling is not achieved. 3.) The DUD ROM can be two sided, whereas. data are recorded on only one side of a CD. This brings total capacity upto ITGB. As with the CD, DUDS correr writeable as well as year only vessions. 2020/6/26 16:50

At a time, which makes them vessatile had slow, Infact, EERROM chips are too slow to one many products that make quick change to the data stored on the chip. FLASH MEMORY: to this Rimitation with Flash spe of Ectron that ones in-constrained to cross by applying lactical field to the entire the called blacks. Florish memory works much laster than traditional Eteps because it write date in chuncks, usually 512 bytes in size instead Port (b) soft error in

HARS FAILURES-Physica 1 or switch Hard errors aca environmental à error nondestructive event and or more + errors can be caused by are clearly undesirable modern man memory system include logic for bot Correcting soon -2020/6/26 16:

Bart: (c) Read and write mechanism Anoma:-WRITE MECHANISM 1 Magnetization

The write mechanism exploits the 9(805) reverses ECHANISM :a coil

the disk rotate, proper the heads generales a correct as the one already recorded. structure of the head for reciding on this case essentially for writing 3 thorse of the sar Lead can be used for the but Soch single head are used in I disk systems & in older rigid disk Contemporary rigid disk systems use tioned las convenience dose to partially shielded magneto resistive line sensor. The MR resistance Atal the magnetize op signals. The me design 2020/6/26 16:51

18 Part: (8) Parallel access & independent access Answer: -PARALLEL ACCESS RAD SCHORES DIDERENDONT ACCES: RAID In Independent In Parallel access Raid schemes all member disks access Raid scheme participate in the execution each member dist sychronized so that can be given time Blu-ray T 2020/6/26 16:51

ANSWER:-> The pit on on HD-DUD are differen Sizo than on Blu-ray Disc, which means that the pits on the disc much be read by a losser of specific light wavelength. -) A HD-DUD has a 15GB per layer strage Capacity, while a Blu-ray Disz has 25 GB per layer storage Capacity. disc menos are constructed and navigated. discs also have a surface layer (the clear plas surface of and scratch tay discs. surface layer Blutray layer to as DUD, while focus with that operfore. This leads to higher Costs for Blu-Ray discs 2020/6/26 16:51

-) The Bo-ray disc has a higher track DUESTION: 3 the following. Part (a) Memory access method

into soils of latage called records. Accordences most be made in a specific linear sequence. Hored addressited information is sood to separate victored and assist in the retrieval process. A shared read write most be moved from its correct location to the decised location of passing a record intermediate victored Thus, the time to access a cabitary record is highly veriable appearate, are soquential access. DIRECT ACCESS:access adirect access involves a hared read-write mechanisme Howe individual black or records have a orique addresss based on rysical location. Acress is accomplishing direct acress to reach a general vicinity plus sequentia searching countings or wasting

reach the final location. Again, are direct access -ac mes -000 age, Prid sequence rectly accessed. d some random access ISSOCIATIVE: his is 1000 Parison words simply lar is redrieved

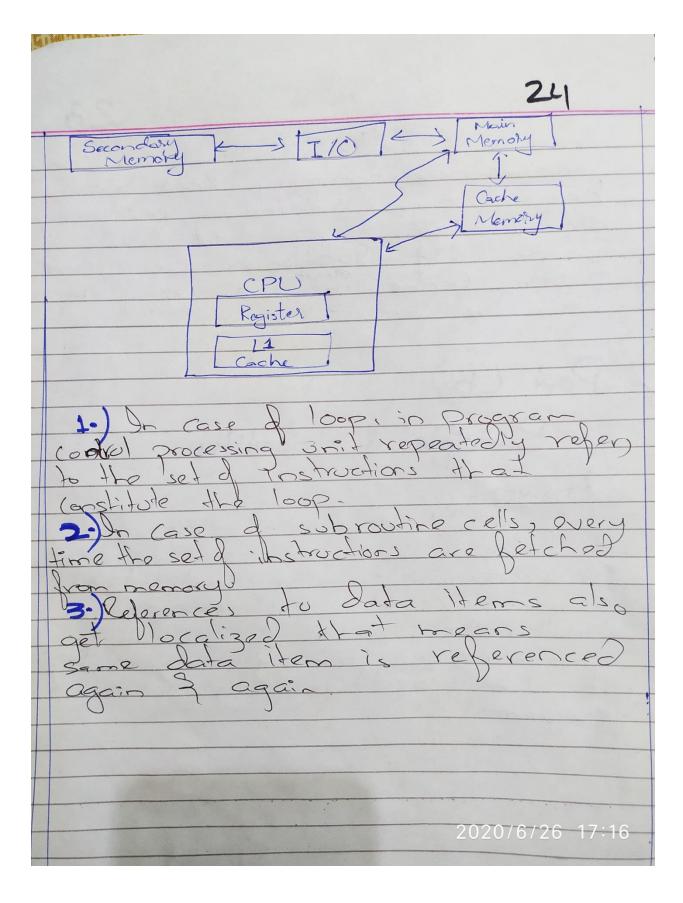

Part (b) Principle of locality The property of

25 SLOW CPU Man First attempt Cache hit Cache (PL) Main Memary Nemary Cache miss sirec

and if food will go through one First way is that the CPU show the required data or instruction so it and that's it but what raquired again. (PU agair 2.) The socond way is to store the data or instruction in the cache memory so that if it is needed soon again in the near future it Particol Possible approaches to Cache Coherency 2020/6/26 17:16

Answee:Possible approaches to cache

Coharency include the following.

-) Bus Watching With Weite THROUGH:-Cach cache controller monitors the Dakes lines to detect write oppositions memory by other has masters. It rather master writes to a location This strategy depends on the use of a write-through policy by all cach (ontrollers. - HARDWARE TRANSPARENCY :-Additional hardware is used to merory jig cache are ref addition pany matching words

-) NON-CACHEABLE MEMORY:-Only a partion of main momery is

shared by more that one processor gan

this is designated as non-cacheable.

In such a system all access to shared

manage are cache misses, because the

shared memory is never copied into the

cache. The nor carchoable memory can

be identified using this - select logic

or high address bits Part :- (d) Practical issues peculiar to There are two practical issues peculiar to SSDs that are not faced by HDDs: JSDD performance has a tendence to show down as the device is used. The entire block must be read

meray and placedo soffer. Plash k from the both The Chire to the bocomes uno sal Techniques for delay or Ising wear, leveling algorithms acros ack of devices action.

Part: (e) Read a write operation

31 se preson ar end of a recorded. ieved rom the cen is technique nicreases capacit -15 stell

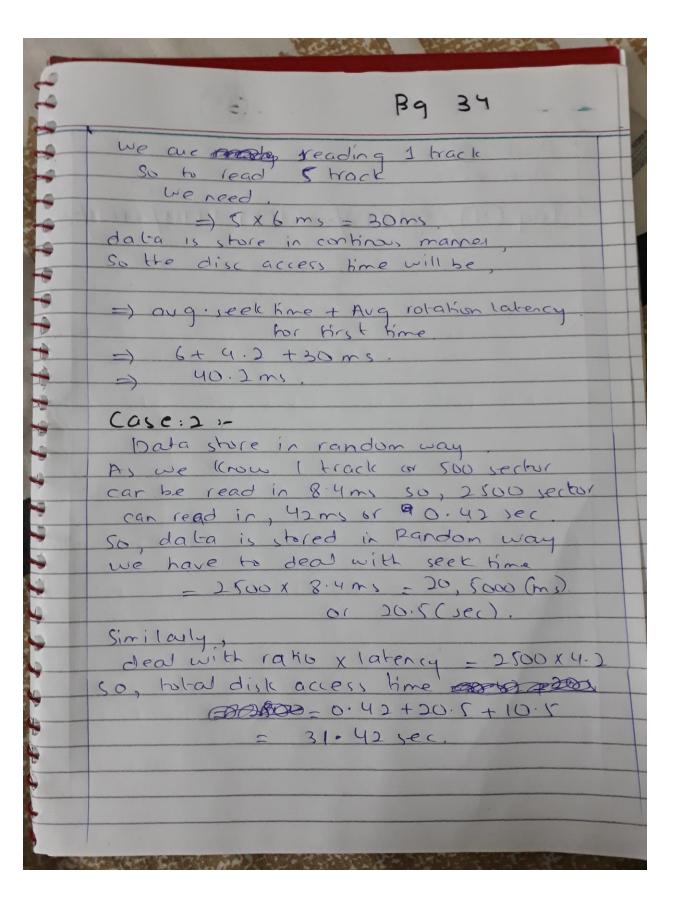

## Pq (32) Question: 4:-Part: a:-Solution :-. The average time to access a word can be expressed as (0.95) (0.01 MS) + (0.05) (0.01 MS + 0.1 MS)= 0.0095 + 0.0055 - 0.015HS · The average access time is much closes to 6:01 Ms than to 0.1 Ms, as desired · Note: 95% at L1 cache and 5% at L2 cache Part : C :-Answer: -Position 12 11 10 D8 D7 D6 D5 C8 D4 D3 D2 C4 D1 Rila 0 1 0 101 Block 110 101 101 100 100 011 011 010 010 001 001 000 0101 10 The check bits are in bit numbers 8, 4, 2 and 1 check bit 8 calculated by values in bit numbers 12, 11, 10, and 9' (1010)=0 check bit 4 calculated by valves in bit number: U, 7, 6, and 5 (1101) =

33331 Pg 33 check bit 2 calculated by values in bit numbers: 11,10,7,6 and 3 (01100) = 0. check bit 1 calculated by values in bit numbers 11,9,7,5 and 3 (00110)=0 Thus, the check bits are: 0010. Part : D :-Answer 1-Solution -Given data: seek time = 6ms. rotation speed = 7200. number of sector = SNO. Size of each sector = 512b. we have to read 2500 sector which is approx 1.28 mb. We know, Disc access time = Aug seek + Ag rotation 1200 rotation require 60 sec. Trotation ue cando in 8.4 ms on avg- 10tation latency = 4.2 ms Case: 1 = Data are stare in continous way we need h read strack and in 1 rotation