# ELECTRONIC DEVICES AND CIRCUITS

**Second Edition**

**JIMMIE J. CATHEY**

Covers all course fundamentals supplements any class text

Hundreds of fully worked problems

**Hundreds of review questions**

The ideal guide for independent study

The perfect aid for better grades

THE ORIGINAL AND MOST POPULAR COLLEGE COURSE SERIES AROUND THE WORLD

# **Theory and Problems of**

# ELECTRONIC DEVICES AND CIRCUITS

**Second Edition**

JIMMIE J. CATHEY, Ph.D.

Professor of Electrical Engineering University of Kentucky

#### **Schaum's Outline Series**

McGRAW-HILL

New York Chicago San Francisco Lisbon London Madrid Mexico City Milan New Delhi San Juan Seoul Singapore Sydney Toronto

Copyright © 2002, 1988 by The McGraw-Hill Companies, Inc. All rights reserved. Manufactured in the United States of America. Except as permitted under the United States Copyright Act of 1976, no part of this publication may be reproduced or distributed in any form or by any means, or stored in a database or retrieval system, without the prior written permission of the publisher.

0-07-139830-9

The material in this eBook also appears in the print version of this title: 0-07-136270-3

All trademarks are trademarks of their respective owners. Rather than put a trademark symbol after every occurrence of a trademarked name, we use names in an editorial fashion only, and to the benefit of the trademark owner, with no intention of infringement of the trademark. Where such designations appear in this book, they have been printed with initial caps.

McGraw-Hill eBooks are available at special quantity discounts to use as premiums and sales promotions, or for use in corporate training programs. For more information, please contact George Hoare, Special Sales, at george\_hoare@mcgraw-hill.com or (212) 904-4069.

#### **TERMS OF USE**

This is a copyrighted work and The McGraw-Hill Companies, Inc. ("McGraw-Hill") and its licensors reserve all rights in and to the work. Use of this work is subject to these terms. Except as permitted under the Copyright Act of 1976 and the right to store and retrieve one copy of the work, you may not decompile, disassemble, reverse engineer, reproduce, modify, create derivative works based upon, transmit, distribute, disseminate, sell, publish or sublicense the work or any part of it without McGraw-Hill's prior consent. You may use the work for your own noncommercial and personal use; any other use of the work is strictly prohibited. Your right to use the work may be terminated if you fail to comply with these terms.

THE WORK IS PROVIDED "AS IS". McGRAW-HILL AND ITS LICENSORS MAKE NO GUARANTEES OR WARRANTIES AS TO THE ACCURACY, ADEQUACY OR COMPLETENESS OF OR RESULTS TO BE OBTAINED FROM USING THE WORK, INCLUDING ANY INFORMATION THAT CAN BE ACCESSED THROUGH THE WORK VIA HYPERLINK OR OTHERWISE, AND EXPRESSLY DISCLAIM ANY WARRANTY, EXPRESS OR IMPLIED, INCLUDING BUT NOT LIMITED TO IMPLIED WARRANTIES OF MERCHANTABILITY OR FITNESS FOR A PARTICULAR PURPOSE. McGraw-Hill and its licensors do not warrant or guarantee that the functions contained in the work will meet your requirements or that its operation will be uninterrupted or error free. Neither McGraw-Hill nor its licensors shall be liable to you or anyone else for any inaccuracy, error or omission, regardless of cause, in the work or for any damages resulting therefrom. McGraw-Hill has no responsibility for the content of any information accessed through the work. Under no circumstances shall McGraw-Hill and/or its licensors be liable for any indirect, incidental, special, punitive, consequential or similar damages that result from the use of or inability to use the work, even if any of them has been advised of the possibility of such damages. This limitation of liability shall apply to any claim or cause whatsoever whether such claim or cause arises in contract, tort or otherwise.

DOI: 10.1036/0071398309

The subject matter of electronics may be divided into two broad categories: the application of physical properties of materials in the development of electronic control devices and the utilization of electronic control devices in circuit applications. The emphasis in this book is on the latter category, beginning with the terminal characteristics of electronic control devices. Other topics are dealt with only as necessary to an understanding of these terminal characteristics.

This book is designed to supplement the text for a first course in electronic circuits for engineers. It will also serve as a refresher for those who have previously taken a course in electronic circuits. Engineering students enrolled in a nonmajors' survey course on electronic circuits will find that portions of Chapters 1 to 7 offer a valuable supplement to their study. Each chapter contains a brief review of pertinent topics along with governing equations and laws, with examples inserted to immediately clarify and emphasize principles as introduced. As in other Schaum's Outlines, primary emphasis is on the solution of problems; to this end, over 350 solved problems are presented.

Three principal changes are introduced in the second edition. SPICE method solutions are presented for numerous problems to better correlate the material with current college class methods. The first-edition Chapter 13 entitled "Vacuum Tubes" has been eliminated. However, the material from that chapter relating to triode vacuum tubes has been dispersed into Chapters 4 and 7. A new Chapter 10 entitled "Switched Mode Power Supplies" has been added to give the reader exposure to this important technology.

SPICE is an acronym for Simulation Program with Integrated Circuit Emphasis. It is commonly used as a generic reference to a host of circuit simulators that use the SPICE2 solution engine developed by U.S. government funding and, as a consequence, is public domain software. PSpice is the first personal computer version of SPICE that was developed by MicroSim Corporation (purchased by OrCAD, which has since merged with Cadence Design Systems, Inc.). As a promotional tool, MicroSim made available several evaluation versions of PSpice for free distribution without restriction on usage. These evaluation versions can still be downloaded from many websites. Presently, Cadence Design Systems, Inc. makes available an evaluation version of PSpice for download by students and professors at <a href="https://www.orcad.com/Products/Simulation/PSpice/eval.asp">www.orcad.com/Products/Simulation/PSpice/eval.asp</a>.

The presentation of SPICE in this book is at the netlist code level that consists of a collection of element-specification statements and control statements that can be compiled and executed by most SPICE solution engines. However, the programs are set up for execution by PSpice and, as a result, contain certain control statements that are particular to PSpice. One such example is the .PROBE statement. Probe is the proprietary PSpice plot manager which, when invoked, saves all node voltages and branch currents of a circuit for plotting at the user's discretion. Netlist code for problems solved by SPICE methods in this book can be downloaded at the author's website <a href="https://www.engr.uky.edu/~cathey">www.engr.uky.edu/~cathey</a>. Errata for this book and selected evaluation versions of PSpice are also available at this website.

The book is written with the assumption that the user has some prior or companion exposure to SPICE methods in other formal course work. If the user does not have a ready reference to SPICE analysis methods, the three following references are suggested (pertinent version of PSpice is noted in parentheses):

1. SPICE: A Guide to Circuit Simulation and Analysis Using PSpice, Paul W. Tuinenga, Prentice-Hall, Englewood Cliffs, NJ, 1992, ISBN 0-13-747270-6 (PSpice 4).

- 2. Basic Engineering Circuit Analysis, 6/e, J. David Irwin and Chwan-Hwa Wu, John Wiley & Sons, New York, 1999, ISBN 0-471-36574-2 (PSpice 8).

- 3. Basic Engineering Circuit Analysis, 7/e, J. David Irwin, John Wiley & Sons, New York, 2002, ISBN 0-471-40740-2 (PSpice 9).

JIMMIE J. CATHEY

| CHAPTER 1 | Circuit Analysis: Port Point of View                 | 1       |

|-----------|------------------------------------------------------|---------|

|           | 1.1 Introduction                                     | 1       |

|           | 1.2 Circuit Elements                                 | 1       |

|           | 1.3 SPICE Elements                                   | 2 3     |

|           | 1.4 Circuit Laws                                     | 3       |

|           | 1.5 Steady-State Circuits                            | 4       |

|           | 1.6 Network Theorems                                 | 4       |

|           | 1.7 Two-Port Networks                                | 8       |

|           | 1.8 Instantaneous, Average, and RMS Values           | 13      |

| CHAPTER 2 | Semiconductor Diodes                                 | 30      |

|           | 2.1 Introduction                                     | 30      |

|           | 2.2 The Ideal Diode                                  | 30      |

|           | 2.3 Diode Terminal Characteristics                   | 32      |

|           | 2.4 The Diode SPICE Model                            | 33      |

|           | 2.5 Graphical Analysis                               | 35      |

|           | 2.6 Equivalent-Circuit Analysis                      | 38      |

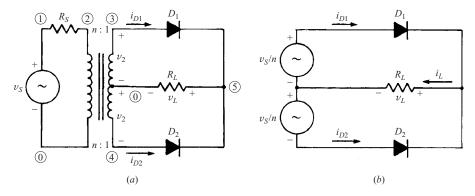

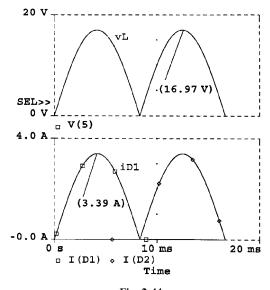

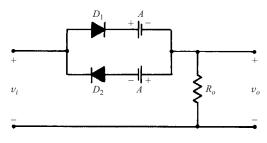

|           | 2.7 Rectifier Applications                           | 40      |

|           | 2.8 Waveform Filtering                               | 42      |

|           | 2.9 Clipping and Clamping Operations                 | 44      |

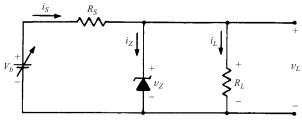

|           | 2.10 The Zener Diode                                 | 46      |

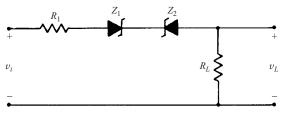

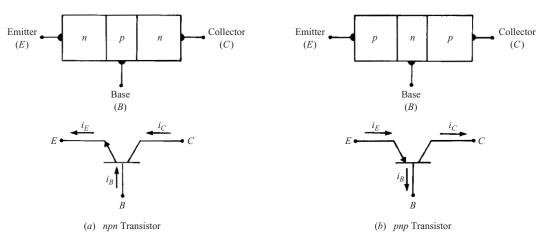

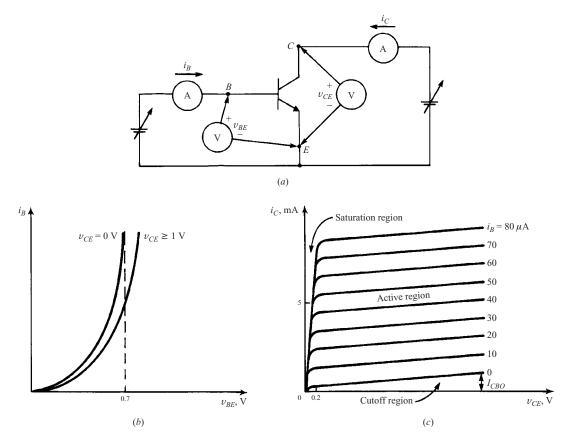

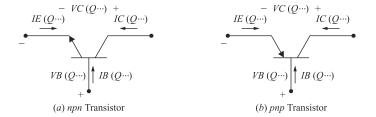

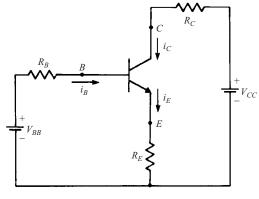

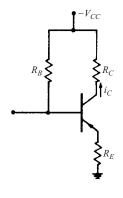

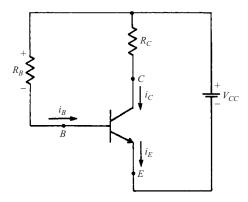

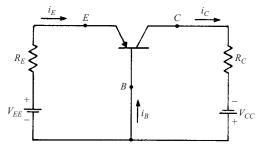

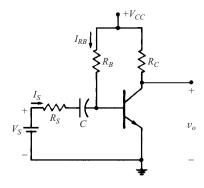

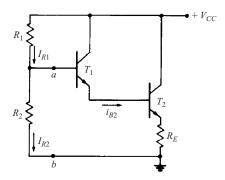

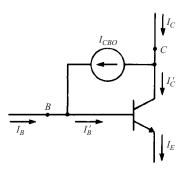

| CHAPTER 3 | Characteristics of Bipolar Junction Transistors      | 70      |

|           | 3.1 BJT Construction and Symbols                     | 70      |

|           | 3.2 Common-Base Terminal Characteristics             | 71      |

|           | 3.3 Common-Emitter Terminal Characteristics          | 71      |

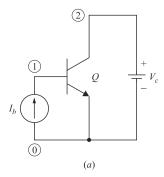

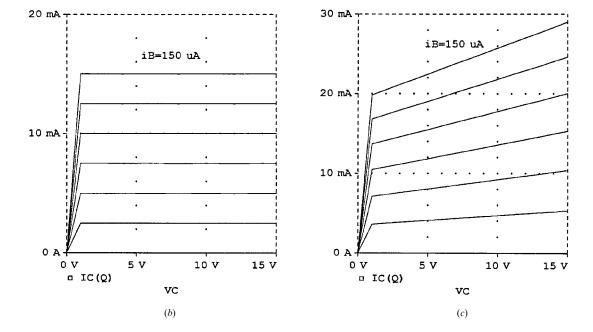

|           | 3.4 BJT SPICE Model                                  | 72      |

|           | 3.5 Current Relationships                            | 77      |

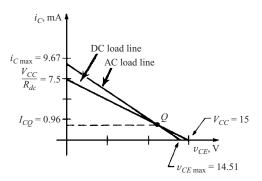

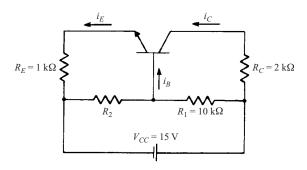

|           | 3.6 Bias and DC Load Lines                           | 78      |

|           | 3.7 Capacitors and AC Load Lines                     | 82      |

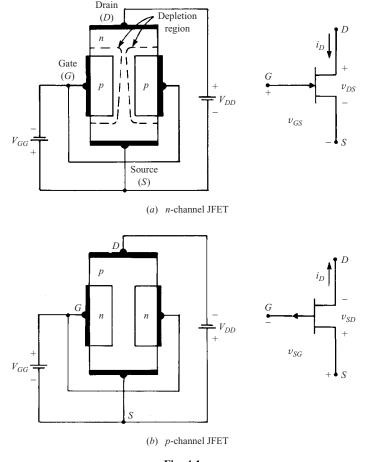

| CHAPTER 4 | Characteristics of Field-Effect Transistors and Trio | des 103 |

|           | 4.1 Introduction                                     | 103     |

|           | 4.2 JFET Construction and Symbols                    | 103     |

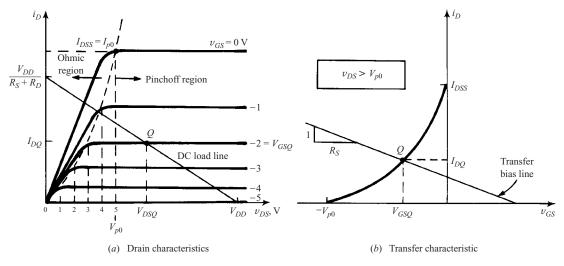

|           | 4.3 JFET Terminal Characteristics                    | 103     |

|           |                                                      |         |

vi Contents

|           | 4.4 JFET SPICE Model                                       | 105 |

|-----------|------------------------------------------------------------|-----|

|           | 4.5 JFET Bias Line and Load Line                           | 107 |

|           | 4.6 Graphical Analysis for the JFET                        | 110 |

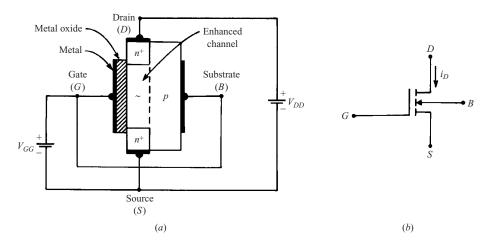

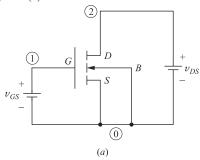

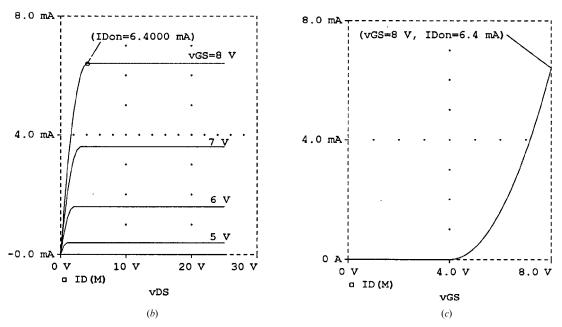

|           | 4.7 MOSFET Construction and Symbols                        | 110 |

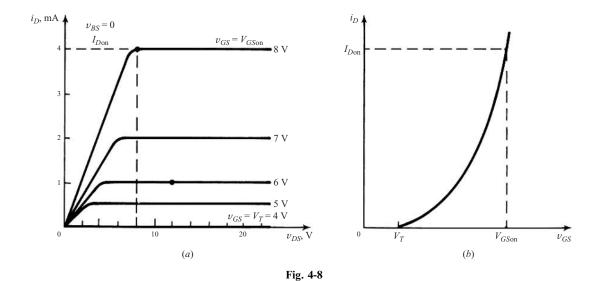

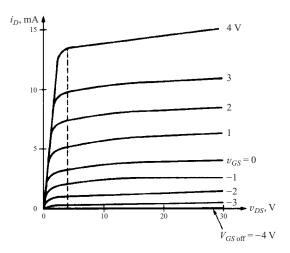

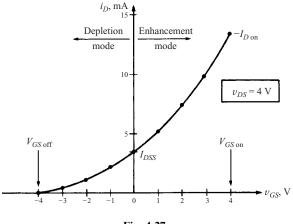

|           | 4.8 MOSFET Terminal Characteristics                        | 110 |

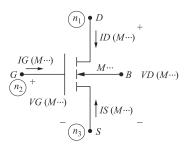

|           | 4.9 MOSFET SPICE Model                                     | 111 |

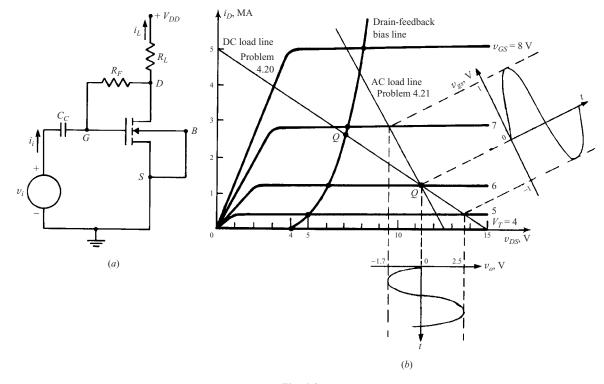

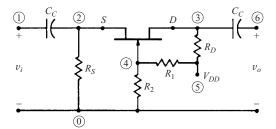

|           | 4.10 MOSFET Bias and Load Lines                            | 114 |

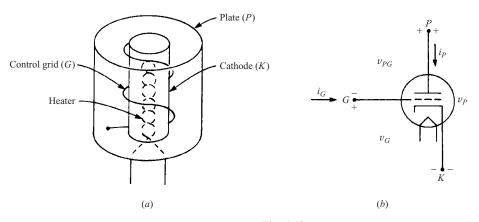

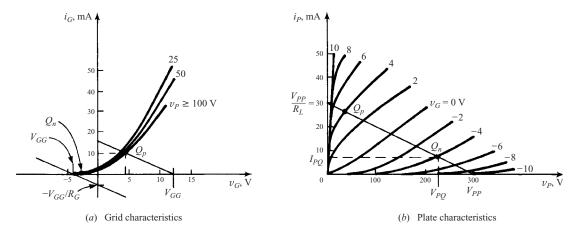

|           | 4.11 Triode Construction and Symbols                       | 115 |

|           | 4.12 Triode Terminal Characteristics and Bias              | 115 |

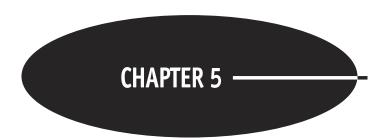

| CHAPTER 5 | Transistor Bias Considerations                             | 136 |

|           | 5.1 Introduction                                           | 136 |

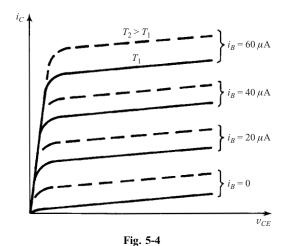

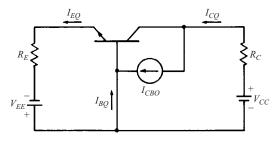

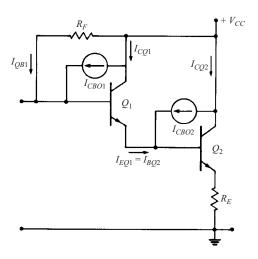

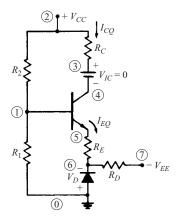

|           | 5.2 $\beta$ Uncertainty and Temperature Effects in the BJT | 136 |

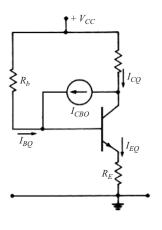

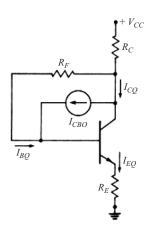

|           | 5.3 Stability Factor Analysis                              | 139 |

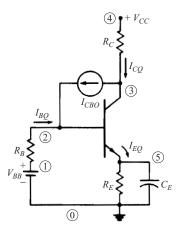

|           | 5.4 Nonlinear-Element Stabilization of BJT Circuits        | 139 |

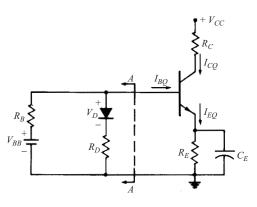

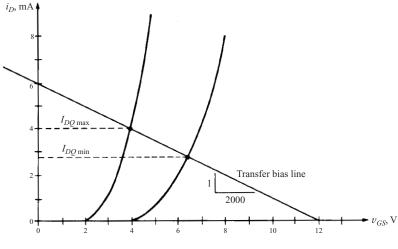

|           | 5.5 <i>Q</i> -Point-Bounded Bias for the FET               | 140 |

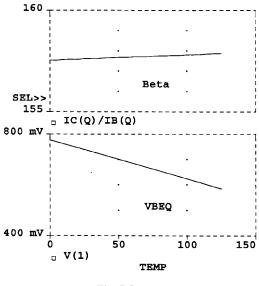

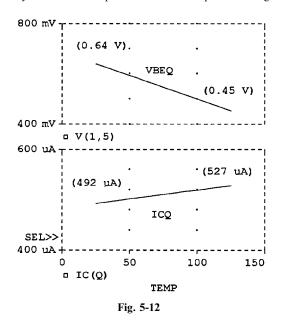

|           | 5.6 Parameter Variation Analysis with SPICE                | 141 |

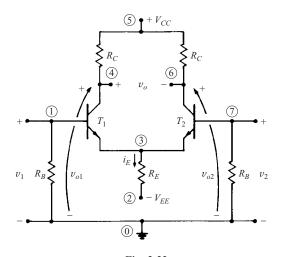

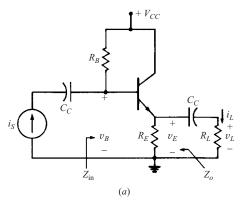

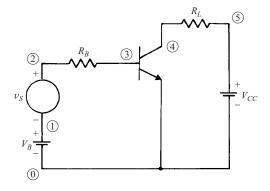

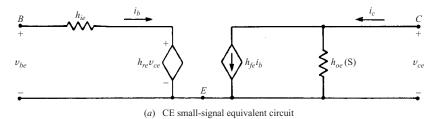

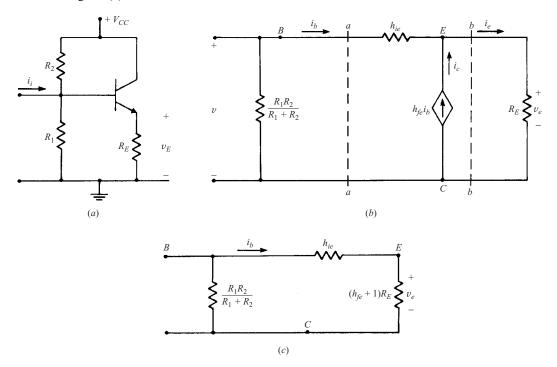

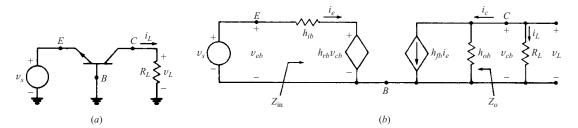

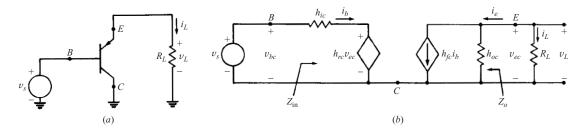

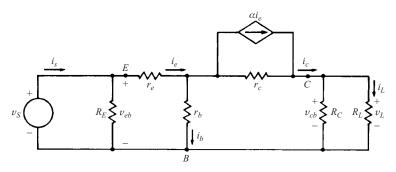

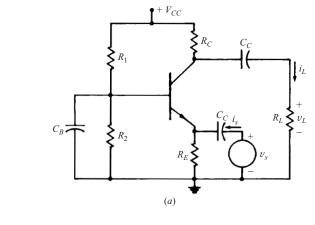

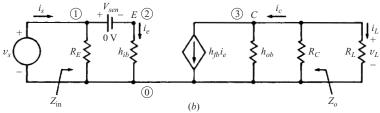

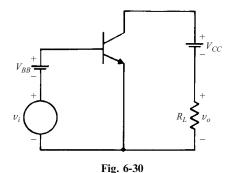

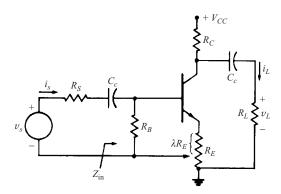

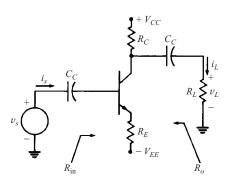

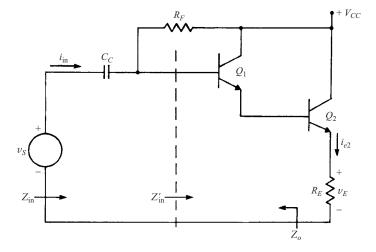

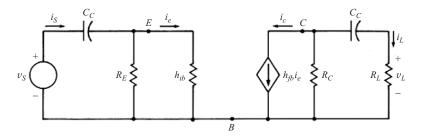

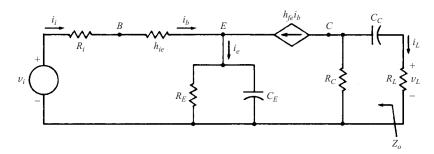

| CHAPTER 6 | Small-Signal Midfrequency BJT Amplifiers                   | 163 |

|           | 6.1 Introduction                                           | 163 |

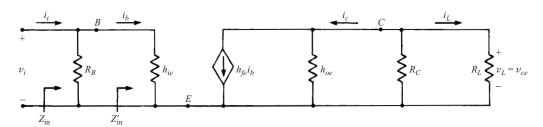

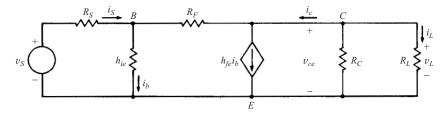

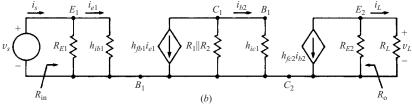

|           | 6.2 Hybrid-Parameter Models                                | 163 |

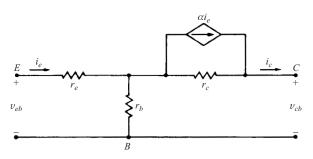

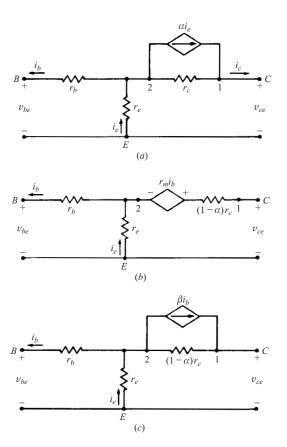

|           | 6.3 Tee-Equivalent Circuit                                 | 166 |

|           | 6.4 Conversion of Parameters                               | 167 |

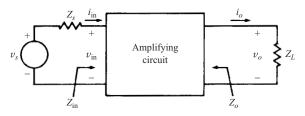

|           | 6.5 Measures of Amplifier Goodness                         | 168 |

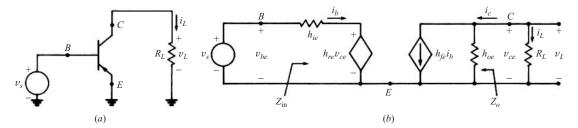

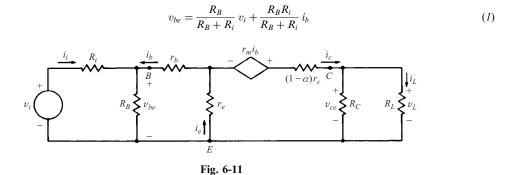

|           | 6.6 CE Amplifier Analysis                                  | 168 |

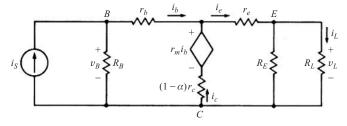

|           | 6.7 CB Amplifier Analysis                                  | 170 |

|           | 6.8 CC Amplifier Analysis                                  | 171 |

|           | 6.9 BJT Amplifier Analysis with SPICE                      | 172 |

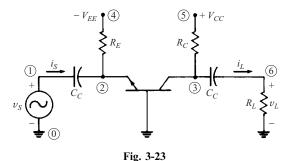

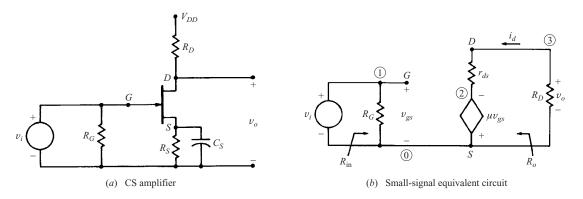

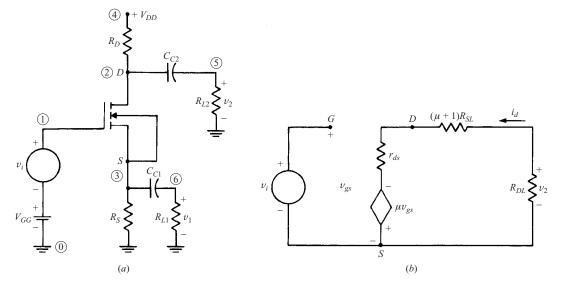

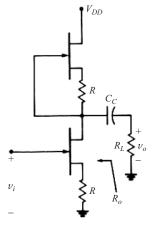

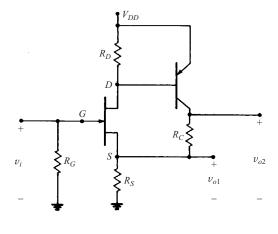

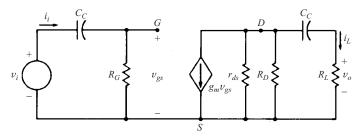

| CHAPTER 7 | Small-Signal Midfrequency FET and Triode Amplifiers        | 200 |

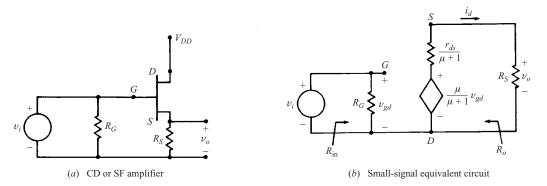

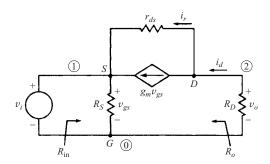

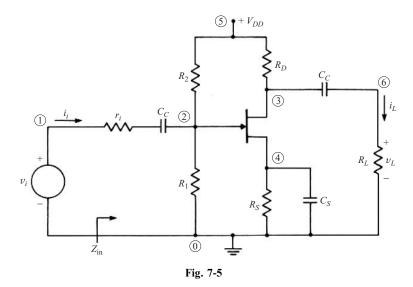

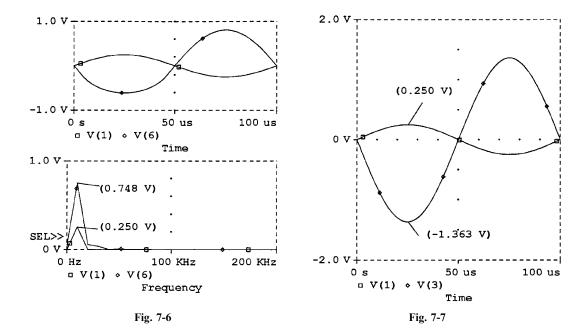

|           | 7.1 Introduction                                           | 200 |

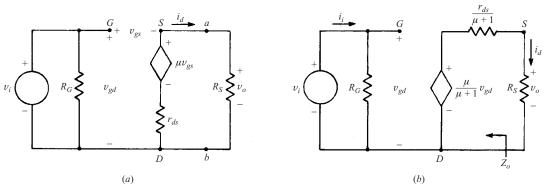

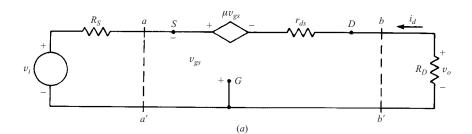

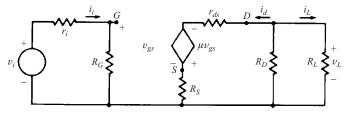

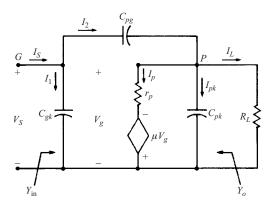

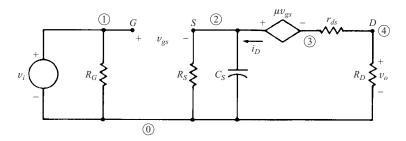

|           | 7.2 Small-Signal Equivalent Circuits for the FET           | 200 |

|           | 7.3 CS Amplifier Analysis                                  | 201 |

|           | 7.4 CD Amplifier Analysis                                  | 202 |

|           | 7.5 CG Amplifier Analysis                                  | 203 |

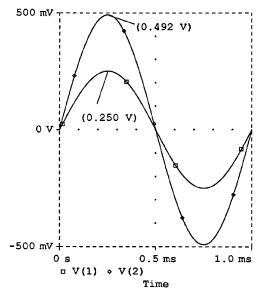

|           | 7.6 FET Amplifier Gain Calculation with SPICE              | 203 |

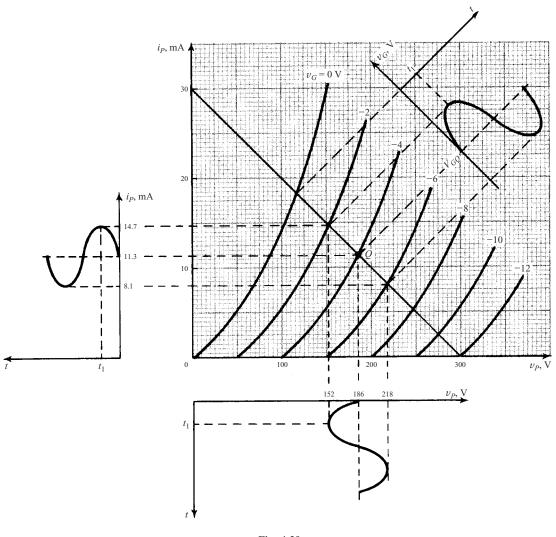

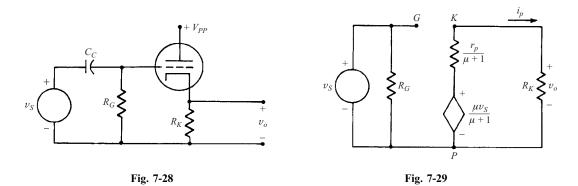

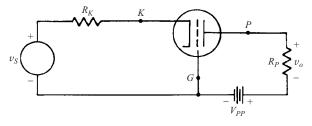

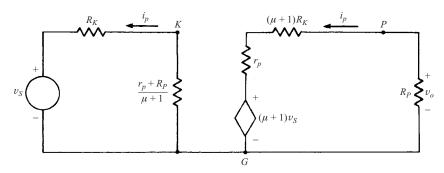

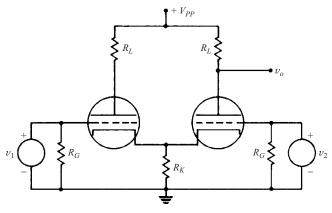

|           | 7.7 Graphical and Equivalent Circuit Analysis of Triode    | 205 |

|           | Amplifiers                                                 | 205 |

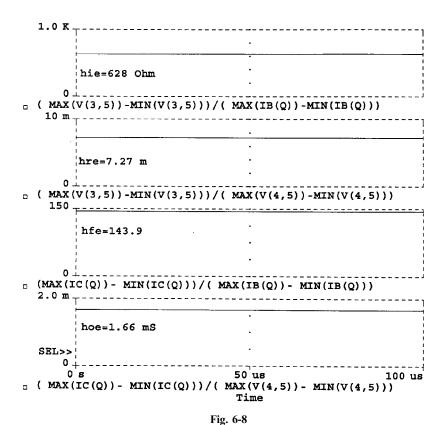

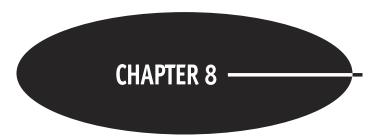

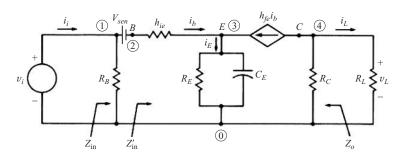

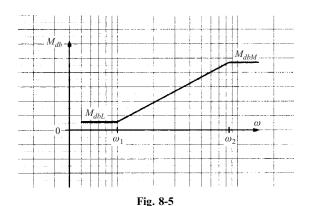

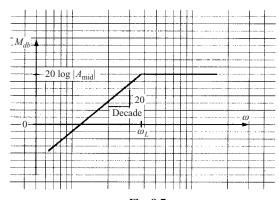

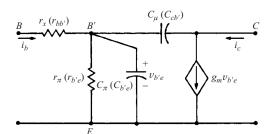

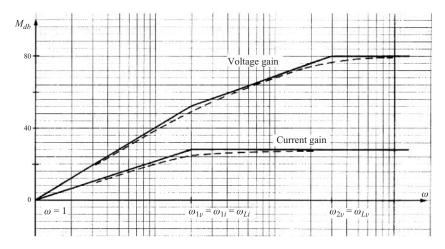

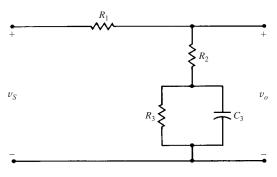

| CHAPTER 8 | Frequency Effects in Amplifiers                            | 226 |

|           | 8.1 Introduction                                           | 226 |

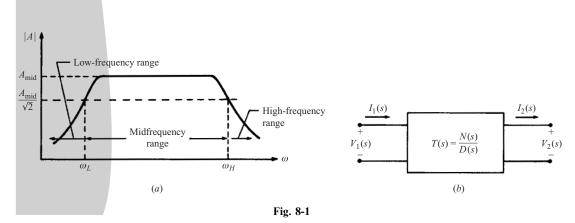

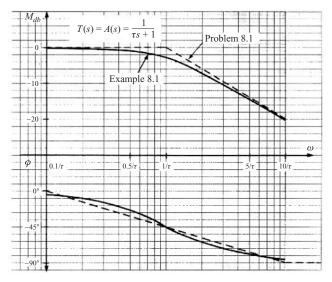

|           | 8.2 Bode Plots and Frequency Response                      | 227 |

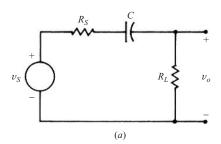

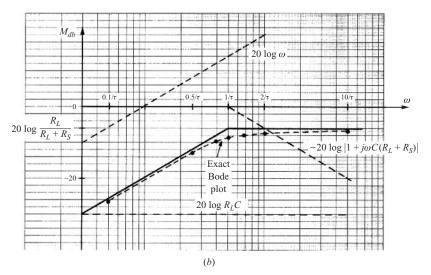

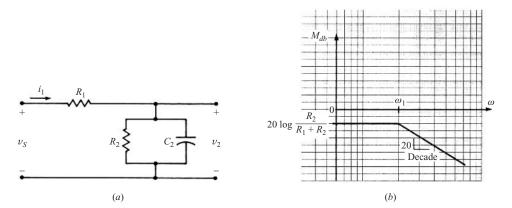

|           | 8.3 Low-Frequency Effect of Bypass and Coupling Capacitors | 229 |

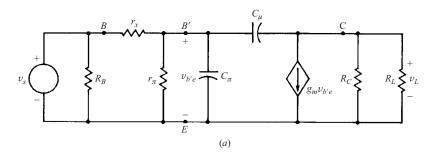

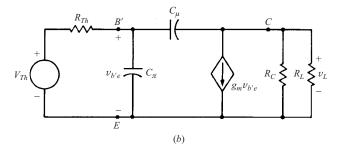

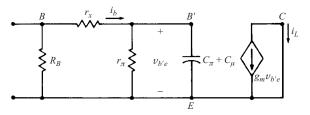

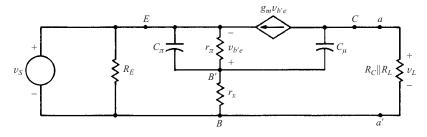

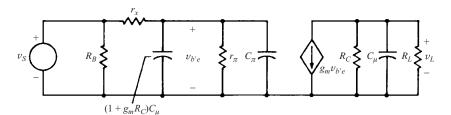

|           | 8.4 High-Frequency Hybrid- $\pi$ BJT Model                 | 232 |

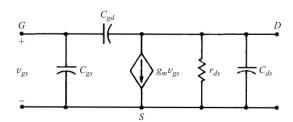

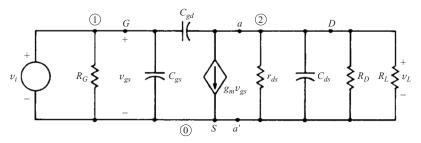

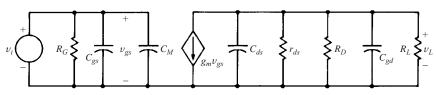

|           | 8.5 High-Frequency FET Models                              | 234 |

|           | 8.6 Miller Capacitance                                     | 235 |

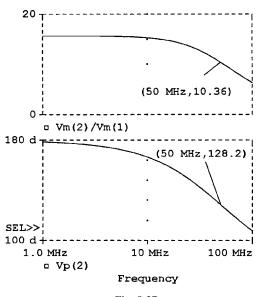

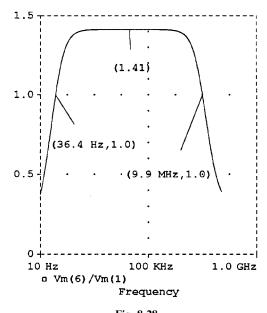

|           | 8.7 Frequency Response Using SPICE                         | 236 |

| ontents | vii |

|---------|-----|

|---------|-----|

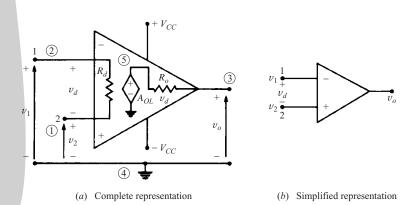

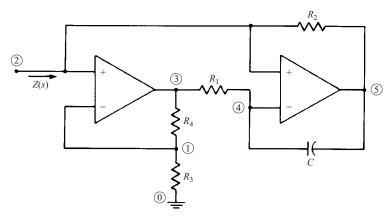

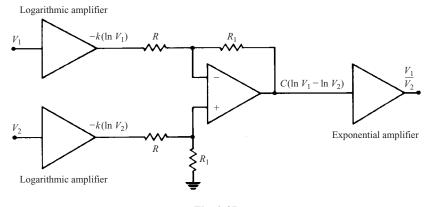

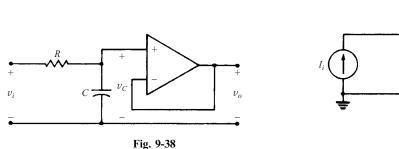

| CHAPTER 9  | Operational Amplifiers                           | 258 |

|------------|--------------------------------------------------|-----|

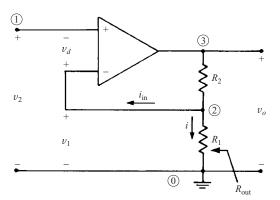

|            | 9.1 Introduction                                 | 258 |

|            | 9.2 Ideal and Practical OP Amps                  | 258 |

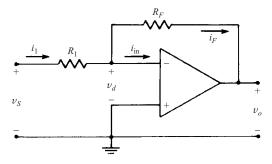

|            | 9.3 Inverting Amplifier                          | 259 |

|            | 9.4 Noninverting Amplifier                       | 260 |

|            | 9.5 Common-Mode Rejection Ratio                  | 260 |

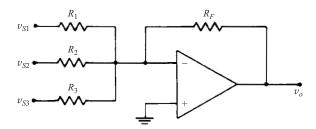

|            | 9.6 Summer Amplifier                             | 261 |

|            | 9.7 Differentiating Amplifier                    | 262 |

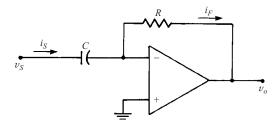

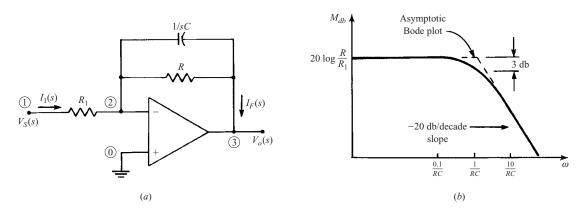

|            | 9.8 Integrating Amplifier                        | 262 |

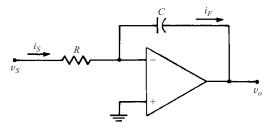

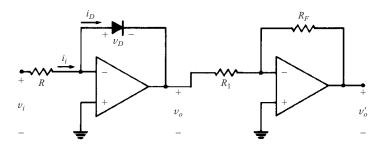

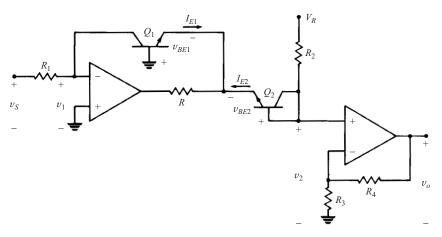

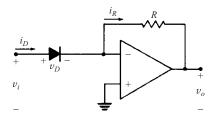

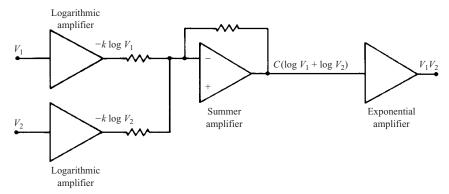

|            | 9.9 Logarithmic Amplifier                        | 263 |

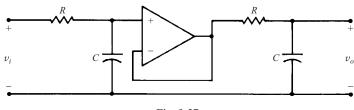

|            | 9.10 Filter Applications                         | 264 |

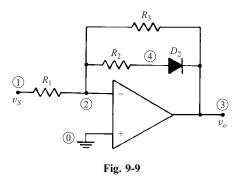

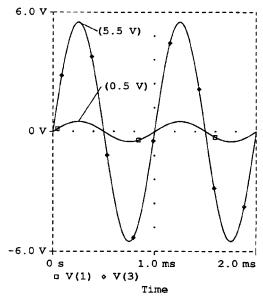

|            | 9.11 Function Generators and Signal Conditioners | 264 |

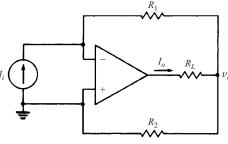

|            | 9.12 SPICE Op Amp Model                          | 265 |

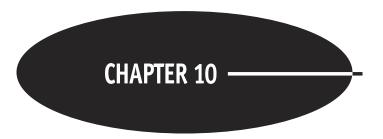

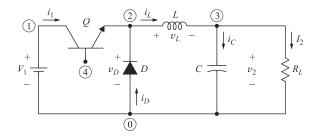

| CHAPTER 10 | Switched Mode Power Supplies                     | 287 |

|            | 10.1 Introduction                                | 287 |

|            | 10.2 Analytical Techniques                       | 287 |

|            | 10.3 Buck Converter                              | 289 |

|            | 10.4 Boost Converter                             | 290 |

|            | 10.5 Buck-Boost Converter                        | 292 |

|            | 10.6 SPICE Analysis of SMPS                      | 294 |

| INDEX      |                                                  | 305 |

# Circuit Analysis: Port Point of View

#### 1.1. INTRODUCTION

Electronic devices are described by their nonlinear terminal voltage-current characteristics. Circuits containing electronic devices are analyzed and designed either by utilizing graphs of experimentally measured characteristics or by linearizing the voltage-current characteristics of the devices. Depending upon applicability, the latter approach involves the formulation of either small-perturbation equations valid about an operating point or a piecewise-linear equation set. The linearized equation set describes the circuit in terms of its interconnected passive elements and independent or controlled voltage and current sources; formulation and solution require knowledge of the circuit analysis and circuit reduction principles reviewed in this chapter.

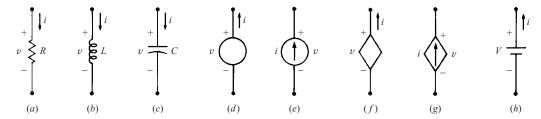

#### 1.2. CIRCUIT ELEMENTS

The time-stationary (or constant-value) elements of Fig. 1-1(a) to (c) (the resistor, inductor, and capacitor, respectively) are called *passive elements*, since none of them can continuously supply energy to a circuit. For voltage v and current i, we have the following relationships: For the resistor,

$$v = Ri$$

or  $i = Gv$  (1.1)

where R is its resistance in ohms  $(\Omega)$ , and  $G \equiv 1/R$  is its conductance in siemens (S). Equation (1.1) is known as Ohm's law. For the inductor,

$$v = L \frac{di}{dt}$$

or  $i = \frac{1}{L} \int_{-\infty}^{t} v \, d\tau$  (1.2)

where L is its *inductance* in henrys (H). For the capacitor,

$$v = \frac{1}{C} \int_{-\infty}^{t} i \, d\tau \qquad \text{or} \qquad i = C \, \frac{dv}{dt} \tag{1.3}$$

where C is its *capacitance* in farads (F). If R, L, and C are independent of voltage and current (as well as of time), these elements are said to be linear: Multiplication of the current through each by a constant will result in the multiplication of its terminal voltage by that same constant. (See Problems 1.1 and 1.3.)

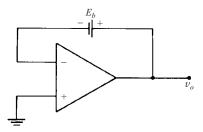

The elements of Fig. 1-1(d) to (h) are called *active elements* because each is capable of continuously supplying energy to a network. The *ideal voltage source* in Fig. 1-1(d) provides a terminal voltage v that is independent of the current i through it. The *ideal current source* in Fig. 1-1(e) provides a current i that is independent of the voltage across its terminals. However, the *controlled* (or *dependent*) voltage source in Fig. 1-1(f) has a terminal voltage that depends upon the voltage across or current through some other element of the network. Similarly, the *controlled* (or *dependent*) current source in Fig. 1-1(g) provides a current whose magnitude depends on either the voltage across or current through some other element of the network. If the dependency relation for the voltage or current of a controlled source is of the first degree, then the source is called a *linear* controlled (or dependent) source. The *battery* or *dc voltage source* in Fig. 1-1(h) is a special kind of independent voltage source.

Fig. 1-1

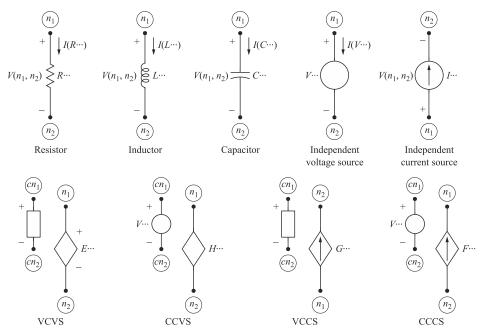

#### 1.3. SPICE ELEMENTS

The passive and active circuit elements introduced in the previous section are all available in SPICE modeling; however, the manner of node specification and the voltage and current sense or direction are clarified for each element by Fig. 1-2. The universal ground node is assigned the number 0. Otherwise, the node numbers  $n_1$  (positive node) and  $n_2$  (negative node) are positive integers

Fig. 1-2

selected to uniquely define each node in the network. The assumed direction of positive current flow is from node  $n_1$  to node  $n_2$ .

The four controlled sources—voltage-controlled voltage source (VCVS), current-controlled voltage source (CCVS), voltage-controlled current source (VCCS), and current-controlled current source (CCCS)— have the associated controlling element also shown with its nodes indicated by  $cn_1$  (positive) and  $cn_2$  (negative). Each element is described by an *element specification statement* in the SPICE netlist code. Table 1-1 presents the basic format for the element specification statement for each of the elements of Fig. 1-2. The first letter of the element name specifies the device and the remaining characters must assure a unique name.

| Element        | Name | Signal Type           | Control Source | Value                     |

|----------------|------|-----------------------|----------------|---------------------------|

| Resistor       | R··· |                       |                | Ω                         |

| Inductor       | L··· |                       |                | Н                         |

| Capacitor      | C    |                       |                | F                         |

| Voltage source | V··· | AC or DC <sup>a</sup> |                | $V^{b}$                   |

| Current source | I··· | AC or DC <sup>a</sup> |                | $\mathbf{A}^{\mathrm{b}}$ |

| VCVS           | E    |                       | $(cn_1, cn_2)$ | V/V                       |

| CCVS           | Н    |                       | V···           | V/A                       |

| VCCS           | G    |                       | $(cn_1, cn_2)$ | A/V                       |

| CCCS           | F··· |                       | V···           | A/A                       |

|                |      |                       | •              |                           |

Table 1-1

#### 1.4. CIRCUIT LAWS

Along with the three voltage-current relationships (1.1) to (1.3), Kirchhoff's laws are sufficient to formulate the simultaneous equations necessary to solve for all currents and voltages of a network. (We use the term *network* to mean any arrangement of circuit elements.)

Kirchhoff's voltage law (KVL) states that the algebraic sum of all voltages around any closed loop of a circuit is zero; it is expressed mathematically as

$$\sum_{k=1}^{n} v_k = 0 (1.4)$$

where n is the total number of passive- and active-element voltages around the loop under consideration.

Kirchhoff's current law (KCL) states that the algebraic sum of all currents entering every node (junction of elements) must be zero; that is

$$\sum_{k=1}^{m} i_k = 0 \tag{1.5}$$

where m is the total number of currents flowing into the node under consideration.

a. Time-varying signal types (SIN, PULSE, EXP, PWL, SFFM) also available.

b. AC signal types may specify phase angle as well as magnitude.

#### 1.5. STEADY-STATE CIRCUITS

At some (sufficiently long) time after a circuit containing linear elements is energized, the voltages and currents become independent of initial conditions and the time variation of circuit quantities becomes identical to that of the independent sources; the circuit is then said to be operating in the steady state. If all nondependent sources in a network are independent of time, the steady state of the network is referred to as the dc steady state. On the other hand, if the magnitude of each nondependent source can be written as  $K \sin(\omega t + \phi)$ , where K is a constant, then the resulting steady state is known as the sinusoidal steady state, and well-known frequency-domain, or phasor, methods are applicable in its analysis. In general, electronic circuit analysis is a combination of dc and sinusoidal steady-state analysis, using the principle of superposition discussed in the next section.

#### 1.6. NETWORK THEOREMS

A linear network (or linear circuit) is formed by interconnecting the terminals of independent (that is, nondependent) sources, linear controlled sources, and linear passive elements to form one or more closed paths. The superposition theorem states that in a linear network containing multiple sources, the voltage across or current through any passive element may be found as the algebraic sum of the individual voltages or currents due to each of the independent sources acting alone, with all other independent sources deactivated.

An ideal voltage source is deactivated by replacing it with a short circuit. An ideal current source is deactivated by replacing it with an open circuit. In general, controlled sources remain active when the superposition theorem is applied.

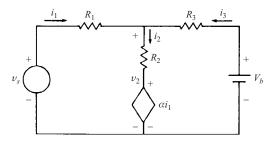

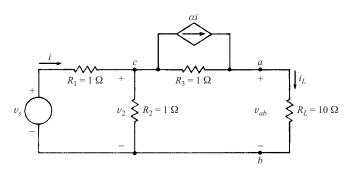

#### **Example 1.1.** Is the network of Fig. 1-3 a linear circuit?

The definition of a linear circuit is satisfied if the controlled source is a linear controlled source; that is, if  $\alpha$  is a constant.

Fig. 1-3

**Example 1.2.** For the circuit of Fig. 1-3,  $v_s = 10 \sin \omega t \, V$ ,  $V_b = 10 \, V$ ,  $R_1 = R_2 = R_3 = 1 \, \Omega$ , and  $\alpha = 0$ . Find current  $i_2$  by use of the superposition theorem.

We first deactivate  $V_b$  by shorting, and use a single prime to denote a response due to  $v_s$  alone. Using the method of node voltages with unknown  $v_2'$  and summing currents at the upper node, we have

$$\frac{v_s - v_2'}{R_1} = \frac{v_2'}{R_2} + \frac{v_2'}{R_3}$$

Substituting given values and solving for  $v_2'$ , we obtain

$$v_2' = \frac{1}{3}v_s = \frac{10}{3}\sin \omega t$$

Then, by Ohm's law,

$$i_2' = \frac{v_2'}{R_2} = \frac{10}{3} \sin \omega t \text{ A}$$

Now, deactivating  $v_s$  and using a double prime to denote a response due to  $V_b$  alone, we have

$$i_3'' = \frac{V_b}{R_3 + R_1 \| R_2}$$

where

$$R_1 \| R_2 \equiv \frac{R_1 R_2}{R_1 + R_2}$$

so that

$$i_3'' = \frac{10}{1 + 1/2} = \frac{20}{3} \text{ A}$$

Then, by current division,

$$i_2'' = \frac{R_1}{R_1 + R_2} i_3'' = \frac{1}{2} i_3'' = \frac{1}{2} \frac{20}{3} = \frac{10}{3} A$$

Finally, by the superposition theorem,

$$i_2 = i_2' + i_2'' = \frac{10}{3}(1 + \sin \omega t) A$$

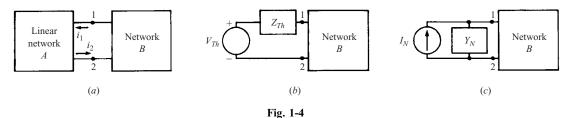

Terminals in a network are usually considered in pairs. A *port* is a terminal pair across which a voltage can be identified and such that the current into one terminal is the same as the current out of the other terminal. In Fig. 1-4, if  $i_1 \equiv i_2$ , then terminals 1 and 2 form a port. Moreover, as viewed to the left from terminals 1,2, network A is a one-port network. Likewise, viewed to the right from terminals 1,2, network B is a one-port network.

Thévenin's theorem states that an arbitrary linear, one-port network such as network A in Fig. 1-4(a) can be replaced at terminals 1,2 with an equivalent series-connected voltage source  $V_{Th}$  and impedance  $Z_{Th}$  (=  $R_{Th}$  +  $jX_{Th}$ ) as shown in Fig. 1-4(b).  $V_{Th}$  is the open-circuit voltage of network A at terminals 1,2 and  $Z_{Th}$  is the ratio of open-circuit voltage to short-circuit current of network A determined at terminals 1,2 with network B disconnected. If network A or B contains a controlled source, its controlling variable must be in that same network. Alternatively,  $Z_{Th}$  is the equivalent impedance looking into network A through terminals 1,2 with all independent sources deactivated. If network A contains a controlled source,  $Z_{Th}$  is found as the driving-point impedance. (See Example 1.4.)

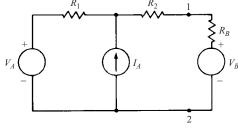

**Example 1.3.** In the circuit of Fig. 1-5,  $V_A = 4 \, \text{V}$ ,  $I_A = 2 \, \text{A}$ ,  $R_1 = 2 \, \Omega$ , and  $R_2 = 3 \, \Omega$ . Find the Thévenin equivalent voltage  $V_{Th}$  and impedance  $Z_{Th}$  for the network to the left of terminals 1,2.

Fig. 1-5

With terminals 1,2 open-circuited, no current flows through  $R_2$ ; thus, by KVL,

$$V_{Th} = V_{12} = V_A + I_A R_1 = 4 + (2)(2) = 8 \text{ V}$$

The Thévenin impedance  $Z_{Th}$  is found as the equivalent impedance for the circuit to the left of terminals 1,2 with the independent sources deactivated (that is, with  $V_A$  replaced by a short circuit, and  $I_A$  replaced by an open circuit):

$$Z_{Th} = R_{Th} = R_1 + R_2 = 2 + 3 = 5 \Omega$$

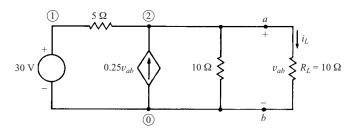

**Example 1.4.** In the circuit of Fig. 1-6(a),  $V_A = 4 \text{ V}$ ,  $\alpha = 0.25 \text{ A/V}$ ,  $R_1 = 2 \Omega$ , and  $R_2 = 3 \Omega$ . Find the Thévenin equivalent voltage and impedance for the network to the left of terminals 1,2.

Fig. 1-6

With terminals 1,2 open-circuited, no current flows through  $R_2$ . But the control variable  $V_L$  for the voltage-controlled dependent source is still contained in the network to the left of terminals 1,2. Application of KVL yields

$$V_{Th} = V_L = V_A + \alpha V_{Th} R_1$$

so that

$$V_{Th} = \frac{V_A}{1 - \alpha R_1} = \frac{4}{1 - (0.25)(2)} = 8 \text{ V}$$

Since the network to the left of terminals 1,2 contains a controlled source,  $Z_{Th}$  is found as the driving-point impedance  $V_{dp}/I_{dp}$ , with the network to the right of terminals 1,2 in Fig. 1-6(a) replaced by the driving-point source of Fig. 1-6(b) and  $V_A$  deactivated (short-circuited). After these changes, KCL applied at node a gives

$$I_1 = \alpha V_{dp} + I_{dp} \tag{1.6}$$

Application of KVL around the outer loop of this circuit (with  $V_A$  still deactivated) yields

$$V_{dp} = I_{dp}R_2 + I_1R_1 (1.7)$$

Substitution of (1.6) into (1.7) allows solution for  $Z_{Th}$  as

$$Z_{Th} = \frac{V_{dp}}{I_{dp}} = \frac{R_1 + R_2}{1 - \alpha R_1} = \frac{2 + 3}{1 - (0.25)(2)} = 10 \,\Omega$$

Norton's theorem states that an arbitrary linear, one-port network such as network A in Fig. 1-4(a) can be replaced at terminals 1,2 by an equivalent parallel-connected current source  $I_N$  and admittance  $Y_N$  as shown in Fig. 1-4(c).  $I_N$  is the short-circuit current that flows from terminal 1 to terminal 2 due to network A, and  $Y_N$  is the ratio of short-circuit current to open-circuit voltage at terminals 1,2 with network B disconnected. If network A or B contains a controlled source, its controlling variable must be in that same network. It is apparent that  $Y_N \equiv 1/Z_{Th}$ ; thus, any method for determining  $Z_{Th}$  is equally valid for finding  $Y_N$ .

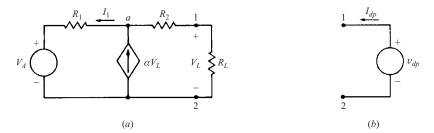

**Example 1.5.** Use SPICE methods to determine the Thévenin equivalent circuit looking to the left through terminals 3,0 for the circuit of Fig. 1-7.

In SPICE independent source models, an ideal voltage source of 0 V acts as a short circuit and an ideal current source of 0 A acts as an infinite impedance or open circuit. Advantage will be taken of these two features to solve the problem.

Load resistor  $R_L$  of Fig. 1-7(a) is replaced by the driving point current source  $I_{dp}$  of Fig. 1-7(b). The netlist code that follows forms a SPICE description of the resulting circuit. The code is set up with parameter-assigned values for  $V_1$ ,  $I_2$ , and  $I_{dp}$ .

```

Ex1_5.CIR - Thevenin equivalent circuit

.PARAM V1value=0V I2value=0A Idpvalue=1A

V1 1 0 DC {V1value}

R1 1 2 10hm

I2 0 2 DC {I2value}

R2 2 0 30hm

R3 2 3 50hm

G3 2 3 (1,0) 0.1; Voltage-controlled current-source

Idp 0 3 DC {Idpvalue}

.END

```

If both  $V_1$  and  $I_2$  are deactivated by setting V1value = I2value = 0, current  $I_{dp} = 1$  A must flow through the Thévenin equivalent impedance  $Z_{Th} = R_{Th}$  so that  $v_3 = I_{dp}R_{Th} = R_{Th}$ . Execution of  $\langle Ex1\_5.CIR \rangle$  by a SPICE program writes the values of the node voltages for nodes 1, 2, and 3 with respect to the universal ground node 0 in a file  $\langle Ex1\_5.OUT \rangle$ . Poll the output file to find  $v_3 = V(3) = R_{Th} = 5.75 \Omega$ .

In order to determine  $V_{Th}$  (open-circuit voltage between terminals 3,0), edit  $\langle \text{Ex1\_5.CIR} \rangle$  to set V1value = 10V, I2value = 2A, and Idpvalue = 0A. Execute  $\langle \text{Ex1\_5.CIR} \rangle$  and poll the output file to find  $V_{Th} = v_3 = \text{V(3)} = 14 \text{ V}$ .

**Example 1.6.** Find the Norton equivalent current  $I_N$  and admittance  $Y_N$  for the circuit of Fig. 1-5 with values as given in Example 1.3.

The Norton current is found as the short-circuit current from terminal 1 to terminal 2 by superposition; it is

$$I_N = I_{12}$$

= current due to  $V_A$  + current due to  $I_A = \frac{V_A}{R_1 + R_2} + \frac{R_1 I_A}{R_1 + R_2}$

=  $\frac{4}{2+3} + \frac{(2)(2)}{2+3} = 1.6 \text{ A}$

The Norton admittance is found from the result of Example 1.3 as

$$Y_N = \frac{1}{Z_{Th}} = \frac{1}{5} = 0.2 \,\mathrm{S}$$

We shall sometimes double-subscript voltages and currents to show the terminals that are of interest. Thus,  $V_{13}$  is the voltage across terminals 1 and 3, where terminal 1 is at a higher potential than terminal 3. Similarly,  $I_{13}$  is the current that flows *from* terminal 1 *to* terminal 3. As an example,  $V_L$  in Fig. 1-6(a) could be labeled  $V_{12}$  (but not  $V_{21}$ ).

Note also that an active element (either independent or controlled) is restricted to its assigned, or stated, current or voltage, no matter what is involved in the rest of the circuit. Thus the controlled source in Fig. 1-6(a) will provide  $\alpha V_L$  A no matter what voltage is required to do so and no matter what changes take place in other parts of the circuit.

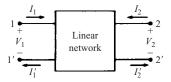

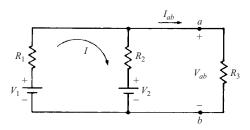

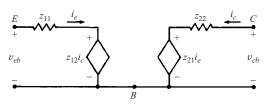

#### 1.7. TWO-PORT NETWORKS

The network of Fig. 1-8 is a *two-port* network if  $I_1 = I_1'$  and  $I_2 = I_2'$ . It can be characterized by the four variables  $V_1$ ,  $V_2$ ,  $I_1$ , and  $I_2$ , only two of which can be independent. If  $V_1$  and  $V_2$  are taken as independent variables and the linear network contains no independent sources, the independent and dependent variables are related by the *open-circuit impedance parameters* (or, simply, the *z parameters*)  $z_{11}$ ,  $z_{12}$ ,  $z_{21}$ , and  $z_{22}$  through the equation set

$$V_1 = z_{11}I_1 + z_{12}I_2 (1.8)$$

$$V_2 = z_{21}I_1 + z_{22}I_2 (1.9)$$

Fig. 1-8

Each of the z parameters can be evaluated by setting the proper current to zero (or, equivalently, by open-circuiting an appropriate port of the network). They are

$$z_{11} = \frac{V_1}{I_1} \bigg|_{I_2 = 0} \tag{1.10}$$

$$z_{12} = \frac{V_1}{I_2} \bigg|_{I_1 = 0} \tag{1.11}$$

$$z_{21} = \frac{V_2}{I_1} \bigg|_{I_2 = 0} \tag{1.12}$$

$$z_{22} = \frac{V_2}{I_2} \bigg|_{I_1 = 0} \tag{1.13}$$

In a similar manner, if  $V_1$  and  $I_2$  are taken as the independent variables, a characterization of the two-port network via the *hybrid parameters* (or, simply, the *h-parameters*) results:

$$V_1 = h_{11}I_1 + h_{12}V_2 (1.14)$$

$$I_2 = h_{21}I_1 + h_{22}V_2 (1.15)$$

Two of the h parameters are determined by short-circuiting port 2, while the remaining two parameters are found by open-circuiting port 1:

$$h_{11} = \frac{V_1}{I_1} \bigg|_{V_2 = 0} \tag{1.16}$$

$$h_{12} = \frac{V_1}{V_2} \bigg|_{I_1 = 0} \tag{1.17}$$

$$h_{21} = \frac{I_2}{I_1} \bigg|_{V_1 = 0} \tag{1.18}$$

$$h_{22} = \frac{I_2}{V_2} \bigg|_{I_1 = 0} \tag{1.19}$$

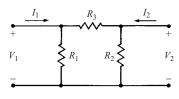

**Example 1.7.** Find the z parameters for the two-port network of Fig. 1-9. With port 2 (on the right) open-circuited,  $I_2 = 0$  and the use of (1.10) gives

$$z_{11} = \frac{V_1}{I_1} \bigg|_{I_2 = 0} = R_1 \| (R_2 + R_3) = \frac{R_1 (R_2 + R_3)}{R_1 + R_2 + R_3}$$

Fig. 1-9

Also, the current  $I_{R2}$  flowing downward through  $R_2$  is, by current division,

$$I_{R2} = \frac{R_1}{R_1 + R_2 + R_3} I_1$$

But, by Ohm's law,

$$V_2 = I_{R2}R_2 = \frac{R_1R_2}{R_1 + R_2 + R_3}I_1$$

Hence, by (1.12),

$$z_{21} = \frac{V_2}{I_1} \bigg|_{I_2 = 0} = \frac{R_1 R_2}{R_1 + R_2 + R_3}$$

Similarly, with port 1 open-circuited,  $I_1 = 0$  and (1.13) leads to

$$z_{22} = \frac{V_2}{I_2} \bigg|_{I_1 = 0} = R_2 \| (R_1 + R_3) = \frac{R_2 (R_1 + R_3)}{R_1 + R_2 + R_3}$$

The use of current division to find the current downward through  $R_1$  yields

$$I_{R1} = \frac{R_2}{R_1 + R_2 + R_3} I_2$$

and Ohm's law gives

$$V_1 = R_1 I_{R1} = \frac{R_1 R_2}{R_1 + R_2 + R_3} I_2$$

Thus, by (1.11),

$$z_{12} = \frac{V_1}{I_2} \bigg|_{I_1=0} = \frac{R_1 R_2}{R_1 + R_2 + R_3}$$

**Example 1.8.** Find the *h* parameters for the two-port network of Fig. 1-9. With port 2 short-circuited,  $V_2 = 0$  and, by (I.16),

$$h_{11} = \frac{V_1}{I_1} \Big|_{V_2 = 0} = R_1 \| R_3 = \frac{R_1 R_3}{R_1 + R_3}$$

By current division,

$$I_2 = -\frac{R_1}{R_1 + R_2} I_1$$

so that, by (1.18),

$$h_{21} = \frac{I_2}{I_1} \Big|_{V_2 = 0} = -\frac{R_1}{R_1 + R_3}$$

If port 1 is open-circuited, voltage division and (1.17) lead to

$V_1 = \frac{R_1}{R_1 + R_3} V_2$

and

$$h_{12} = \frac{V_1}{V_2} \bigg|_{I_1 = 0} = \frac{R_1}{R_1 + R_3}$$

Finally,  $h_{22}$  is the admittance looking into port 2, as given by (1.19):

$$h_{22} = \frac{I_2}{V_2} \bigg|_{I_1 = 0} = \frac{1}{R_2 ||(R_1 + R_3)} = \frac{R_1 + R_2 + R_3}{R_2 (R_1 + R_3)}$$

The z parameters and the h parameters can be numerically evaluated by SPICE methods. In electronics applications, the z and h parameters find application in analysis when small ac signals are impressed on circuits that exhibit limited-range linearity. Thus, in general, the test sources in the SPICE analysis should be of magnitudes comparable to the impressed signals of the anticipated application. Typically, the devices used in an electronic circuit will have one or more dc sources connected to bias or that place the device at a favorable point of operation. The input and output ports may be coupled by large capacitors that act to block the appearance of any dc voltages at the input and output ports while presenting negligible impedance to ac signals. Further, electronic circuits are usually frequency-sensitive so that any set of z or h parameters is valid for a particular frequency. Any SPICE-based evaluation of the z and h parameters should be capable of addressing the above outlined characteristics of electronic circuits.

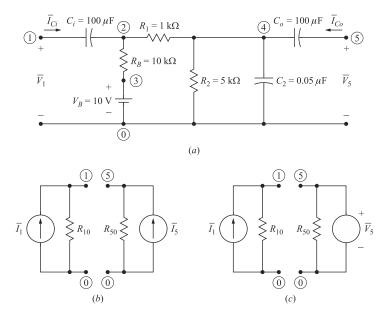

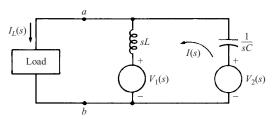

**Example 1.9.** For the frequency-sensitive two-port network of Fig. 1-10(a), use SPICE methods to determine the z parameters suitable for use with sinusoidal excitation over a frequency range from 1 kHz to 10 kHz.

The z parameters as given by (1.10) to (1.13), when evaluated for sinusoidal steady-state conditions, are formed as the ratios of phasor voltages and currents. Consequently, the values of the z parameters are complex numbers that can be represented in polar form as  $z_{ij} = z_{ij} \angle \phi_{ij}$ .

For determination of the z parameters, matching terminals of the two sinusoidal current sources of Fig. 1-10(b) are connected to the network under test of Fig. 1-10(a). The netlist code below models the resulting network with parameter-assigned values for  $\bar{I}_1$  and  $\bar{I}_5$ . Two separate executions of <Ex1\_9.CIR> are required to determine all four z parameters. The .AC statement specifies a sinusoidal steady-state solution of the circuit for 11 values of frequency over the range from 10 kHz to 100 kHz.

Fig. 1-10

```

Ex1_9.CIR - z-parameter evaluation

.PARAM I1value=1mA I5value=0mA

I1 0 1 AC {I1value}

R10 1 0 1Tohm; Large resistor to avoid floating node

Ci 12100uF

2 3 10kohm

0 3 DC 10V

24 1kohm

4 0 5kohm

400.05uF

5 4 100uF

I5  0 5 AC {I5value}

R50 5 0 1Tohm; Large resistor to avoid floating node

.AC LIN 11 10kHz 100kHz

.PROBE

.END

```

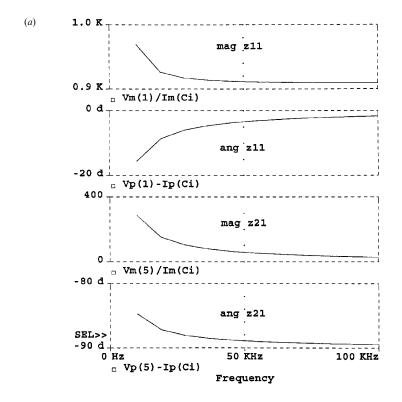

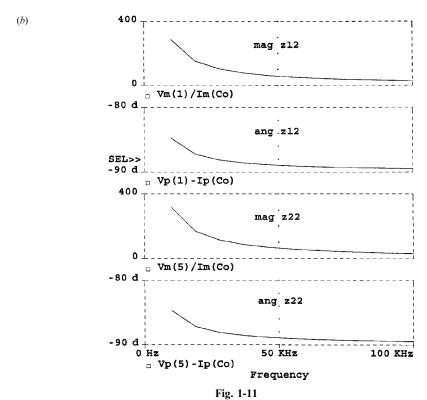

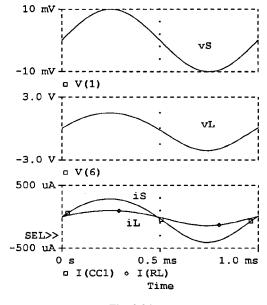

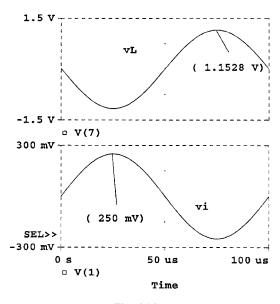

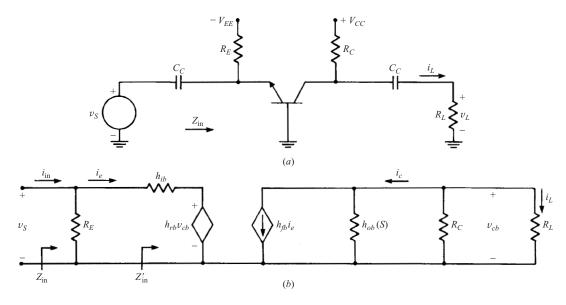

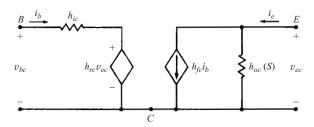

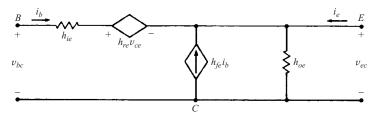

The values of R10 and R50 are sufficiently large  $(1 \times 10^{12} \Omega)$  so that  $\bar{I}_1 = \bar{I}_{Ci}$  and  $\bar{I}_5 = \bar{I}_{Co}$ . If source  $\bar{I}_5$  is deactivated by setting I5value = 0 and I1value is assigned a small value (i.e., 1 mA), then  $z_{11}$  and  $z_{21}$  are determined by (1.10) and (1.12), respectively.  $\langle \text{Ex1\_9.CIR} \rangle$  is executed and the probe feature of PSpice is used to graphically display the magnitudes and phase angles of  $z_{11}$  and  $z_{21}$  in Fig. 1-11(a). Similarly,  $\bar{I}_1$  is deactivated and  $\bar{I}_5$  is assigned a small value (11value = 0, 15value = 1mA) to determine the values of  $z_{12}$  and  $z_{22}$  by (1.11) and (1.13), respectively. Execution of  $\langle \text{Ex1\_9.CIR} \rangle$  and use of the Probe feature of PSpice results in the magnitudes and phase angles of  $z_{12}$  and  $z_{22}$  as shown by Fig. 1-11(b).

**Example 1.10.** Use SPICE methods to determine the h parameters suitable for use with sinusoidal excitation at a frequency of  $10 \, \text{kHz}$  for the frequency-sensitive two-port network of Fig. 1-10(a).

The h parameters of (1.16) to (1.19) for sinusoidal steady-state excitation are ratios of phasor voltages and currents; thus the values are complex numbers expressible in polar form as  $\mathbf{h}_{ij} = h_{ij} \angle \phi_{ij}$ .

Connect the sinusoidal voltage source and current source of Fig. 1-10(c) to the network of Fig. 1-10(a). The netlist code below models the resulting network with parameter-assigned values for  $\bar{I}_1$  and  $\bar{V}_5$ . Two separate executions of <Ex1\_10.CIR> are required to produce the results needed for evaluation of all four h parameters.

Through use of the .PRINT statement, both magnitudes and phase angles of  $\bar{V}_1$ ,  $\bar{V}_5$ ,  $\bar{I}_{Ci}$ , and  $\bar{I}_{Co}$  are written to <Ex1 10.OUT> and can be retrieved by viewing of the file.

```

Ex1_10.CIR - h-parameter evaluation

.PARAM Ilvalue=0mA V5value=1mV

I1 01AC {Ilvalue}

R10 101Tohm; Large resistor to avoid floating node

Ci 12100uF

RB 2310kohm

VB 03DC10V

R1 241kohm

R2 405kohm

C2 400.05uF

C0 54100uF

V5 50AC {V5value}

.AC LIN 110kHz 10kHz

.PRINT AC Vm(1) Vp(1) Im(Ci) Ip(Ci); Mag & phase of inputs

.PRINT AC Vm(5) Vp(5) Im(Co) Ip(Co); Mag & phase of outputs

.END

```

Set V5value = 0 (deactivates  $\vec{V}_5$ ) and I1value = 1mA. Execute  $\langle \text{Ex1\_10.CIR} \rangle$  and retrieve the necessary values of  $\vec{V}_1$ ,  $\vec{I}_{Ci}$ , and  $\vec{I}_{Co}$  to calculate  $\vec{h}_{11}$  and  $\vec{h}_{21}$  by use of (1.16) and (1.18).

$$\begin{aligned} & \mathbf{h}_{11} = \frac{\text{Vm}(1)}{\text{Im}(\text{Ci})} \angle(\text{Vp}(1) - \text{Ip}(\text{Ci})) \cong \frac{0.9091}{0.001} \angle(-0.02^{\circ} + 0^{\circ}) = 909.1 \angle -0.02^{\circ} \\ & \mathbf{h}_{21} = \frac{\text{Im}(\text{Co})}{\text{Im}(\text{Ci})} \angle(\text{Ip}(\text{Co}) - \text{Ip}(\text{Ci})) \cong \frac{9.08 \times 10^{-4}}{1 \times 10^{-3}} \angle(-180^{\circ} + 0^{\circ}) = 0.908 \angle -180^{\circ} \end{aligned}$$

Set V5value = 1mV and I1value = 0 (deactivates  $\bar{I}_1$ ). Execute < Exl\_10.CIR > and retrieve the needed values of  $\bar{V}_1$ ,  $\bar{V}_5$ , and  $\bar{I}_{Co}$  to evaluate  $h_{12}$  and  $h_{22}$  by use of (1.17) and (1.19).

$$\begin{split} & \mathbf{\textit{h}}_{21} = \frac{\mathrm{Vm}(1)}{\mathrm{Vm}(5)} \, \angle \left( \mathrm{Vp}(1) - \mathrm{Vp}(5) \right) \cong \frac{9.08 \times 10^{-4}}{1 \times 10^{-3}} \, \angle \left( 0^{\circ} - 0^{\circ} \right) = 0.908 \angle 0^{\circ} \\ & \mathbf{\textit{h}}_{22} = \frac{\mathrm{Im}(\mathrm{Co})}{\mathrm{Vm}(5)} \, \angle \left( \mathrm{Ip}(\mathrm{Co}) - \mathrm{Vp}(5) \right) \cong \frac{3.15 \times 10^{-6}}{1 \times 10^{-3}} \, \angle \left( 84.7^{\circ} - 0^{\circ} \right) = 3.15 \times 10^{-3} \, \angle \, 84.7^{\circ} \end{split}$$

#### 1.8. INSTANTANEOUS, AVERAGE, AND RMS VALUES

The *instantaneous value* of a quantity is the value of that quantity at a specific time. Often we will be interested in the average value of a time-varying quantity. But obviously, the average value of a sinusoidal function over one period is zero. For sinusoids, then, another concept, that of the *root-mean-square* (or rms) value, is more useful: For any time-varying function f(t) with period T, the *average* value over one period is given by

$$F_0 = \frac{1}{T} \int_{t_0}^{t_0+T} f(t) dt \tag{1.20}$$

and the corresponding rms value is defined as

$$F = \sqrt{\frac{1}{T} \int_{t_0}^{t_0 + T} f^2(t) dt}$$

(1.21)

where, of course,  $F_0$  and F are independent of  $t_0$ . The motive for introducing rms values can be gathered from Example 1.12.

**Example 1.11.** Since the average value of a sinusoidal function of time is zero, the *half-cycle* average value, which is nonzero, is often useful. Find the half-cycle average value of the current through a resistance R connected directly across a periodic (ac) voltage source  $v(t) = V_m \sin \omega t$ .

By Ohm's law,

$$i(t) = \frac{v(t)}{R} = \frac{V_m}{R} \sin \omega t$$

and from (1.20), applied over the half cycle from  $t_0 = 0$  to  $T/2 = \pi$ ,

$$I_0 = \frac{1}{\pi} \int_0^{\pi} \frac{V_m}{R} \sin \omega t \, d(\omega t) = \frac{1}{\pi} \frac{V_m}{R} [-\cos \omega t]_{\omega t = 0}^{\pi} = \frac{2}{\pi} \frac{V_m}{R}$$

(1.22)

**Example 1.12.** Consider a resistance R connected directly across a dc voltage source  $V_{\rm dc}$ . The power absorbed by R is

$$P_{\rm dc} = \frac{V_{\rm dc}^2}{R} \tag{1.23}$$

Now replace  $V_{\rm dc}$  with an ac voltage source,  $v(t) = V_m \sin \omega t$ . The instantaneous power is now given by

$$p(t) = \frac{v^2(t)}{R} = \frac{V_m^2}{R} \sin^2 \omega t \tag{1.24}$$

Hence, the average power over one period is, by (1.20),

$$P_0 = \frac{1}{2\pi} \int_0^{2\pi} \frac{V_m^2}{R} \sin^2 \omega t \, d(\omega t) = \frac{V_m^2}{2R}$$

(1.25)

Comparing (1.23) and (1.25), we see that, insofar as power dissipation is concerned, an ac source of amplitude  $V_m$  is equivalent to a dc source of magnitude

$$\frac{V_m}{\sqrt{2}} = \sqrt{\frac{1}{T}} \int_0^T v^2(t) \, dt \equiv V \tag{1.26}$$

For this reason, the rms value of a sinusoid,  $V = V_m/\sqrt{2}$ , is also called its *effective* value.

From this point on, unless an explicit statement is made to the contrary, all currents and voltages in the frequency domain (phasors) will reflect rms rather than maximum values. Thus, the time-domain voltage  $v(t) = V_m \cos(\omega t + \phi)$  will be indicated in the frequency domain as  $\bar{V} = V | \phi$ , where  $V = V_m / \sqrt{2}$ .

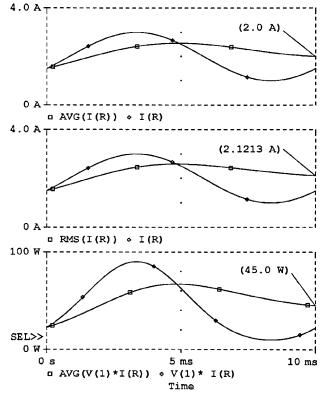

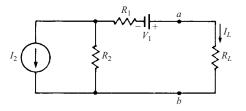

**Example 1.13.** A sinusoidal source, a dc source, and a  $10 \Omega$  resistor are connected as shown by Fig. 1-12. If  $v_s = 10 \sin(\omega t - 30^\circ)$  V and  $V_B = 20$  V, use SPICE methods to determine the average value of  $i(I_0)$ , the rms value of i(I), and the average value of power  $(P_0)$  supplied to R.

Fig. 1-12

The netlist code below describes the circuit. Notice that the two sources have been combined as a  $10\,\mathrm{V}$  sinusoidal source with a 20-V dc bias. The frequency has been arbitrarily chosen as  $100\,\mathrm{Hz}$  as the solution is independent of frequency.

```

Ex1_13.CIR - Avg & rms current, avg power vsVB 1 0 SIN(20V 10V 100Hz 0 0 -30deg)

R 1 0 10ohm

.PROBE

.TRAN 5us 10ms

.END

```

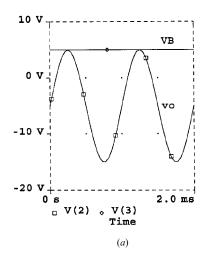

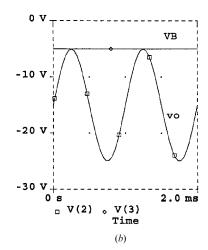

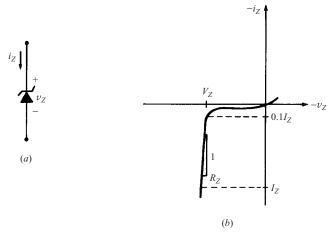

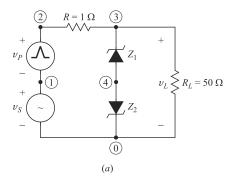

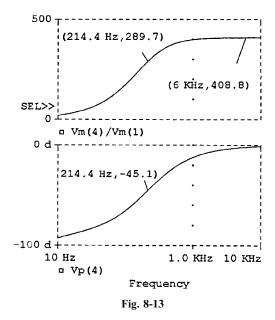

The Probe feature of PSpice is used to display the instantaneous values of i(t) and  $p_R(t)$ . The running average and running RMS features of PSpice have been implemented as appropriate. Both features give the correct full-period values at the end of each period of the source waveform. Figure 1-13 shows the marked values as  $I_0 = 2.0 \,\mathrm{A}$ ,  $I = 2.1213 \,\mathrm{A}$ , and  $P_0 = 45.0 \,\mathrm{W}$ .

Fig. 1-13

#### **Solved Problems**

1.1 Prove that the inductor element of Fig. 1-1(b) is a linear element by showing that (1.2) satisfies the converse of the superposition theorem.

Let  $i_1$  and  $i_2$  be two currents that flow through the inductors. Then by (1.2) the voltages across the inductor for these currents are, respectively,

$$v_1 = L \frac{di_1}{dt}$$

and  $v_2 = L \frac{di_2}{dt}$  (1)

Now suppose  $i = k_1 i_1 + k_2 i_2$ , where  $k_1$  and  $k_2$  are distinct arbitrary constants. Then by (1.2) and (1),

$$v = L \frac{d}{dt}(k_1 i_1 + k_2 i_2) = k_1 L \frac{di_1}{dt} + k_2 L \frac{di_2}{dt} = k_1 v_1 + k_2 v_2$$

(2)

Since (2) holds for any pair of constants  $(k_1, k_2)$ , superposition is satisfied and the element is linear.

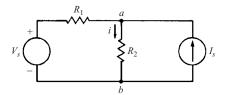

1.2 If  $R_1 = 5 \Omega$ ,  $R_2 = 10 \Omega$ ,  $V_s = 10 V$ , and  $I_s = 3 A$  in the circuit of Fig. 1-14, find the current *i* by using the superposition theorem.

Fig. 1-14

With  $I_s$  deactivated (open-circuited), KVL and Ohm's law give the component of i due to  $V_s$  as

$$i' = \frac{V_s}{R_1 + R_2} = \frac{10}{5 + 10} = 0.667 \,\text{A}$$

With  $V_s$  deactivated (short-circuited), current division determines the component of i due to  $I_s$ :

$$i'' = \frac{R_1}{R_1 + R_2} I_s = \frac{5}{5 + 10} 3 = 1 \text{ A}$$

By superposition, the total current is

$$i = i' + i'' = 0.667 + 1 = 1.667 \text{ A}$$

1.3 In Fig. 1-14, assume all circuit values as in Problem 1.2 except that  $R_2 = 0.25i\,\Omega$ . Determine the current *i* using the method of node voltages.

By (1.1), the voltage-current relationship for  $R_2$  is

$$v_{ab} = R_2 i = (0.25i)(i) = 0.25i^2$$

$i = 2\sqrt{v_{ab}}$  (1)

so that

Applying the method of node voltages at a and using (I), we get

$$\frac{v_{ab} - V_s}{R_1} + 2\sqrt{v_{ab}} - I_s = 0$$

Rearrangement and substitution of given values lead to

$$v_{ab} + 10\sqrt{v_{ab}} - 25 = 0$$

Letting  $x^2 = v_{ab}$  and applying the quadratic formula, we obtain

$$x = \frac{-10 \pm \sqrt{(10)^2 - 4(-25)}}{2} = 2.071$$

or  $-12.07$

The negative root is extraneous, since the resulting value of  $v_{ab}$  would not satisfy KVL; thus,

$$v_{ab} = (2.071)^2 = 4.289 \,\text{V}$$

and  $i = 2 \times 2.071 = 4.142 \,\text{A}$

Notice that, because the resistance  $R_2$  is a function of current, the circuit is not linear and the superposition theorem cannot be applied.

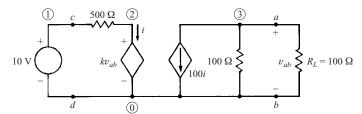

1.4 For the circuit of Fig. 1-15, find  $v_{ab}$  if (a) k = 0 and (b) k = 0.01. Do not use network theorems to simplify the circuit prior to solution.

Fig. 1-15

(a) For k = 0, the current i can be determined immediately with Ohm's law:

$$i = \frac{10}{500} = 0.02 \,\text{A}$$

Since the output of the controlled current source flows through the parallel combination of two  $100-\Omega$  resistors, we have

$$v_{ab} = -(100i)(100||100) = -100 \times 0.02 \frac{(100)(100)}{100 + 100} = -100 \text{ V}$$

(1)

(b) With  $k \neq 0$ , it is necessary to solve two simultaneous equations with unknowns i and  $v_{ab}$ . Around the left loop, KVL yields

$$0.01v_{ab} + 500i = 10 \tag{2}$$

With i unknown, (1) becomes

$$v_{ab} + 5000i = 0 (3)$$

Solving (2) and (3) simultaneously by Cramer's rule leads to

$$v_{ab} = \frac{\begin{vmatrix} 10 & 500 \\ 0 & 5000 \end{vmatrix}}{\begin{vmatrix} 0.01 & 500 \\ 1 & 5000 \end{vmatrix}} = \frac{50,000}{-450} = -111.1 \text{ V}$$

- 1.5 For the circuit of Fig. 1-15, use SPICE methods to solve for  $v_{ab}$  if (a) k = 0.001 and (b) k = 0.05.

- (a) The SPICE netlist code for k = 0.001 follows:

Prb.1\_5.CIR Vs 1 0 DC 10V R1 1 2 5000hm E 2 0 (3,0) 0.001; Last entry is value of k F 0 3 Vs 100 R2 3 0 1000hm RL 3 0 1000hm .DC Vs 10 10 1 .PRINT DC V(3) .END

Execute  $\langle Prb1\_5.CIR \rangle$  and poll the output file to find  $v_{ab} = V(3) = -101 \text{ V}$ .

- (b) Edit < Prb1\_5.CIR > to set k = 0.05, execute the code, and poll the output file to find  $v_{ab} = V(3) = -200 \,\text{V}$ .

- **1.6** For the circuit of Fig. 1-16, find  $i_L$  by the method of node voltages if (a)  $\alpha = 0.9$  and (b)  $\alpha = 0$ .

Fig. 1-16

(a) With  $v_2$  and  $v_{ab}$  as unknowns and summing currents at node c, we obtain

$$\frac{v_2 - v_s}{R_1} + \frac{v_2}{R_2} + \frac{v_2 - v_{ab}}{R_3} + \alpha i = 0 \tag{1}$$

But

$$i = \frac{v_s - v_2}{R_1} \tag{2}$$

Substituting (2) into (1) and rearranging gives

$$\left(\frac{1-\alpha}{R_1} + \frac{1}{R_2} + \frac{1}{R_3}\right)v_2 - \frac{1}{R_3}v_{ab} = \frac{1-\alpha}{R_1}v_s \tag{3}$$

Now, summation of currents at node a gives

$$\frac{v_{ab} - v_2}{R_2} - \alpha i + \frac{v_{ab}}{R_1} = 0 \tag{4}$$

Substituting (2) into (4) and rearranging yields

$$-\left(\frac{1}{R_3} - \frac{\alpha}{R_1}\right)v_2 + \left(\frac{1}{R_3} + \frac{1}{R_I}\right)v_{ab} = \frac{\alpha}{R_1}v_s \tag{5}$$

Substitution of given values into (3) and (5) and application of Cramer's rule finally yield

$$v_{ab} = \frac{\begin{vmatrix} 2.1 & 0.1v_s \\ -0.1 & 0.9v_s \end{vmatrix}}{\begin{vmatrix} 2.1 & -1 \\ -0.1 & 1.1 \end{vmatrix}} = \frac{1.9v_s}{2.21} = 0.8597v_s$$

and by Ohm's law,

$$i_L = \frac{v_{ab}}{R_L} = \frac{0.8597v_s}{10} = 0.08597v_s$$

A

(b) With the given values (including  $\alpha = 0$ ) substituted into (3) and (5), Cramer's rule is used to find

$$v_{ab} = \frac{\begin{vmatrix} 3 & v_s \\ -1 & 0 \end{vmatrix}}{\begin{vmatrix} 3 & -1 \\ -1 & 1.1 \end{vmatrix}} = \frac{v_s}{2.3} = 0.4348v_s$$

Then  $i_L$  is again found with Ohm's law:

$$i_L = \frac{v_{ab}}{R_L} = \frac{0.4348v_s}{10} = 0.04348v_s$$

A

1.7 If  $V_1 = 10 \text{ V}$ ,  $V_2 = 15 \text{ V}$ ,  $R_1 = 4 \Omega$ , and  $R_2 = 6 \Omega$  in the circuit of Fig. 1-17, find the Thévenin equivalent for the network to the left of terminals a, b.

Fig. 1-17

With terminals a, b open-circuited, only loop current I flows. Then, by KVL,

$$V_1 - IR_1 = V_2 + IR_2$$

so that

$$I = \frac{V_1 - V_2}{R_1 + R_2} = \frac{10 - 15}{4 + 6} = -0.5 \text{ A}$$

The Thévenin equivalent voltage is then

$$V_{Th} = V_{ab} = V_1 - IR_1 = 10 - (-0.5)(4) = 12 \text{ V}$$

Deactivating (shorting) the independent voltage sources  $V_1$  and  $V_2$  gives the Thévenin impedance to the left of terminals a, b as

$$Z_{Th} = R_{Th} = R_1 || R_2 = \frac{R_1 R_2}{R_1 + R_2} = \frac{(4)(6)}{4 + 6} = 2.4 \,\Omega$$

$V_{Th}$  and  $Z_{Th}$  are connected as in Fig. 1-4(b) to produce the Thévenin equivalent circuit.

1.8 For the circuit and values of Problem 1.7, find the Norton equivalent for the network to the left of terminals a, b.

With terminals a, b shorted, the component of current  $I_{ab}$  due to  $V_1$  alone is

$$I'_{ab} = \frac{V_1}{R_1} = \frac{10}{4} = 2.5 \,\text{A}$$

Similarly, the component due to  $V_2$  alone is

$$I_{ab}^{"} = \frac{V_2}{R_2} = \frac{15}{6} = 2.5 \,\text{A}$$

Then, by superposition,

$$I_N = I_{ab} = I'_{ab} + I''_{ab} = 2.5 + 2.5 = 5 \text{ A}$$

Now, with  $R_{Th}$  as found in Problem 1.7,

$$Y_N = \frac{1}{R_{Th}} = \frac{1}{2.4} = 0.4167 \,\text{A}$$

$I_N$  and  $Y_N$  are connected as in Fig. 1-4(c) to produce the Norton equivalent circuit.

1.9 For the circuit and values of Problems 1.7 and 1.8, find the Thévenin impedance as the ratio of open-circuit voltage to short-circuit current to illustrate the equivalence of the results.

The open-circuit voltage is  $V_{Th}$  as found in Problem 1.7, and the short-circuit current is  $I_N$  from Problem 1.8. Thus,

$$Z_{Th} = \frac{V_{Th}}{I_N} = \frac{12}{5} = 2.4 \,\Omega$$

which checks with the result of Problem 1.7.

1.10 Thévenin's and Norton's theorems are applicable to other than dc steady-state circuits. For the "frequency-domain" circuit of Fig. 1-18 (where s is frequency), find (a) the Thévenin equivalent and (b) the Norton equivalent of the circuit to the right of terminals a, b.

Fig. 1-18

(a) With terminals a, b open-circuited, only loop current I(s) flows; by KVL and Ohm's law, with all currents and voltages understood to be functions of s, we have

$$I = \frac{V_2 - V_1}{sL + 1/sC}$$

Now KVL gives

$$V_{Th} = V_{ab} = V_1 + sLI = V_1 + \frac{sL(V_2 - V_1)}{sL + 1/sC} = \frac{V_1 + s^2LCV_2}{s^2LC + 1}$$

With the independent sources deactivated, the Thévenin impedance can be determined as

$$Z_{Th} = sL \| \frac{1}{sC} = \frac{sL(1/sC)}{sL + 1/sC} = \frac{sL}{s^2LC + 1}$$

(b) The Norton current can be found as

$$I_{N} = \frac{V_{Th}}{Z_{Th}} = \frac{\frac{V_{1} + s^{2}LCV_{2}}{s^{2}LC + 1}}{\frac{sL}{s^{2}LC + 1}} = \frac{V_{1} + s^{2}LCV_{2}}{sL}$$

and the Norton admittance as

$$Y_N = \frac{1}{Z_{Th}} = \frac{s^2 LC + 1}{sL}$$

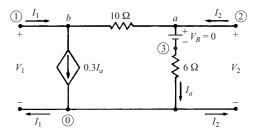

**1.11** Determine the z parameters for the two-port network of Fig. 1-19.

For  $I_2 = 0$ , by Ohm's law,

$$I_a = \frac{V_1}{10+6} = \frac{V_1}{16}$$

Fig. 1-19

Also, at node b, KCL gives

$$I_1 = 0.3I_a + I_a = 1.3I_a = 1.3\frac{V_1}{16}$$

(1)

Thus, by (1.10),

$$z_{11} = \frac{V_1}{I_1} \bigg|_{I_1=0} = \frac{16}{1.3} = 12.308 \,\Omega$$

Further, again by Ohm's law,

$$I_a = \frac{V_2}{6} \tag{2}$$

Substitution of (2) into (1) yields

$$I_1 = 1.3 \, \frac{V_2}{6}$$

so that, by (1.12),

$$z_{21} = \frac{V_2}{I_1} \bigg|_{I_2 = 0} = \frac{6}{1.3} = 4.615 \,\Omega$$

Now with  $I_1 = 0$ , applying KCL at node a gives us

$$I_2 = I_a + 0.3I_a = 1.3I_a \tag{3}$$

The application of KVL then leads to

$$V_1 = V_2 - (10)(0.3I_a) = 6I_a - 3I_a = 3I_a = \frac{3I_2}{1.3}$$

so that, by (1.11),

$$z_{12} = \frac{V_1}{I_2} \Big|_{I_1=0} = \frac{3}{1.3} = 2.308 \,\Omega$$

Now, substitution of (2) in (3) gives

$$I_2 = 1.3I_a = 1.3 \frac{V_2}{6}$$

Hence, from (1.13),

$$z_{22} = \frac{V_2}{I_2} \bigg|_{I_1 = 0} = \frac{6}{1.3} = 4.615 \,\Omega$$

**1.12** Solve Problem 1.11 using a SPICE method similar to that of Example 1.9. The SPICE netlist code is

Prbl\_12.CIR z-parameter evaluation

.PARAM Ilvalue=1mA I2value=0mA

I1 0 1 AC {I1value}

F 10 VB 0.3

R1 1 2 10ohm

VB 2 3 0V; Current sense

R2 3 0 6ohm

I2 0 2 AC {I2value}

.DC I1 0 1mA 1mA I2 1mA 0 1mA; Nested loop

.PRINT DC V(1) I(I1) V(2) I(I2)

.END

A nested loop is used in the .DC statement to eliminate the need for two separate executions. As a consequence, data is generated for I1 = I2 = 1mA and I1 = I2 = 0, which is extraneous to the problem.

Execute < Prb1\_12.CIR > and poll the output file to obtain data to evaluate the z parameters by use of (1.10) to (1.13).

$$\begin{split} z_{11} &= \frac{V_1}{I_1} \bigg|_{I_2 = 0} = \frac{V(1)}{I(I1)} \bigg|_{I(I2) = 0} = \frac{1.231 \times 10^{-2}}{1 \times 10^{-3}} = 12.31 \,\Omega \\ z_{12} &= \frac{V_1}{I_2} \bigg|_{I_1 = 0} = \frac{V(1)}{I(I2)} \bigg|_{I(I1) = 0} = \frac{2.308 \times 10^{-3}}{1 \times 10^{-3}} = 2.308 \,\Omega \\ z_{21} &= \frac{V_2}{I_1} \bigg|_{I_2 = 0} = \frac{V(2)}{I(I1)} \bigg|_{I(I1) = 0} = \frac{4.615 \times 10^{-3}}{1 \times 10^{-3}} = 4.615 \,\Omega \\ z_{22} &= \frac{V_2}{I_2} \bigg|_{I_1 = 0} = \frac{V(2)}{I(I2)} \bigg|_{I(I1) = 0} = \frac{4.615 \times 10^{-3}}{1 \times 10^{-3}} = 4.615 \,\Omega \end{split}$$

**1.13** Determine the h parameters for the two-port network of Fig. 1-19.

For  $V_2 = 0$ ,  $I_a \equiv 0$ ; thus,  $I_1 = V_1/10$  and, by (1.16),

$$h_{11} = \frac{V_1}{I_1} \bigg|_{V_2 = 0} = 10 \,\Omega$$

Further,  $I_2 = -I_1$  and, by (1.18),

$$h_{21} = \frac{I_2}{I_1} \bigg|_{V_2 = 0} = -1$$

Now,  $I_a = V_2/6$ . With  $I_1 = 0$ , KVL yields

$$V_1 = V_2 - 10(0.3I_a) = V_2 - 10(0.3)\frac{V_2}{6} = \frac{1}{2}V_2$$

and, from (1.17),

$$h_{12} = \frac{V_1}{V_2} \bigg|_{I_1 = 0} = 0.5$$

Finally, applying KCL at node a gives

$$I_2 = I_a + 0.3I_a = 1.3 \frac{V_2}{6}$$

so that, by (1.19),

$$h_{22} = \frac{I_2}{V_2} \Big|_{I_1 = 0} = \frac{1.3}{6} = 0.2167 \,\text{S}$$

**1.14** Use (1.8), (1.9), and (1.16) to (1.19) to find the h parameters in terms of the z parameters.

Setting  $V_2 = 0$  in (1.9) gives

$$0 = z_{21}I_1 + z_{22}I_2 \qquad \text{or} \qquad I_2 = -\frac{z_{21}}{z_{22}}I_1 \tag{1}$$

from which we get

$$h_{21} = \frac{I_2}{I_1} \Big|_{V_2 = 0} = -\frac{z_{21}}{z_{22}}$$

Back substitution of (1) into (1.8) and use of (1.16) give

$$h_{11} = \frac{V_1}{I_1} \Big|_{V_2 = 0} = z_{11} - \frac{z_{12} z_{21}}{z_{22}}$$

Now, with  $I_1 = 0$ , (1.8) and (1.9) become

$$V_1 = z_{12}I_2$$

and  $V_2 = z_{22}I_2$

so that, from (1.17),

$$h_{12} = \frac{V_1}{V_2} \bigg|_{L=0} = \frac{z_{12}}{z_{22}}$$

and, from (1.19),

$$h_{22} = \frac{I_2}{V_2} \Big|_{I_1 = 0} = \frac{I_2}{z_{22}I_2} = \frac{1}{z_{22}}$$

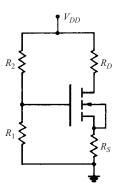

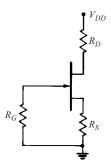

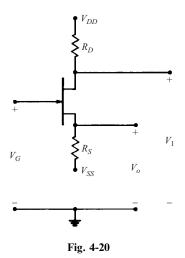

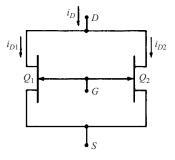

1.15 The h parameters of the two-port network of Fig. 1-20 are  $h_{11} = 100 \Omega$ ,  $h_{12} = 0.0025$ ,  $h_{21} = 20$ , and  $h_{22} = 1 \text{ mS}$ . Find the voltage-gain ratio  $V_2/V_1$ .

Fig. 1-20

By Ohm's law,  $I_2 = -V_2/R_L$ , so that (1.15) may be written

$$-\frac{V_2}{R_I} = I_2 = h_{21}I_1 + h_{22}V_2$$

Solving for  $I_1$  and substitution into (1.14) give

$$V_1 = h_{11}I_1 + h_{12}V_2 = \frac{-(1/R_L + h_{22})}{h_{21}} V_2 h_{22} + h_{12}V_2$$

which can be solved for the voltage gain ratio:

$$\frac{V_2}{V_1} = \frac{1}{h_{12} - (h_{11}/h_{21})(1/R_L + h_{22})} = \frac{1}{0.0025 - (100/20)(1/2000 + 0.001)} = -200$$

**1.16** Determine the Thévenin equivalent voltage and impedance looking right into port 1 of the circuit of Fig. 1-20.

The Thévenin voltage is  $V_1$  of (1.8) with port 1 open-circuited:

$$V_{Th} = V_1|_{I_1=0} = z_{12}I_2 \tag{1}$$

Now, by Ohm's law,

$$V_2 = -R_L I_2 \tag{2}$$

But, with  $I_1 = 0$ , (1.9) reduces to

$$V_2 = z_{22}I_2 (3)$$

Subtracting (2) from (3) leads to

$$(z_{22} + R_L)I_2 = 0 (4)$$

Since, in general,  $z_{22} + R_L \neq 0$ , we conclude from (4) that  $I_2 = 0$  and, from (1),  $V_{Th} = 0$ . Substituting (2) into (1.8) and (1.9) gives

$$V_1 = z_{11}I_1 + z_{12}I_2 = z_{11}I_1 - \frac{z_{12}}{R_L}V_2$$

(5)

and

$$V_2 = z_{21}I_1 + z_{22}I_2 = z_{21}I_1 - \frac{z_{22}}{R_L}V_2$$

(6)

$V_1$  is found by solving for  $V_2$  and substituting the result into (5):

$$V_1 = z_{11}I_1 - \frac{z_{12}z_{21}}{z_{22} + R_L}I_1$$

Then  $Z_{Th}$  is calculated as the driving-point impedance  $V_1/I_1$ :

$$Z_{Th} = \frac{V_{dp}}{I_{dp}} = \frac{V_1}{I_1} = z_{11} - \frac{z_{12}z_{21}}{z_{22} + R_L}$$

1.17 Find the Thévenin equivalent voltage and impedance looking into port 1 of the circuit of Fig. 1-20 if  $R_L$  is replaced with a current-controlled voltage source such that  $V_2 = \beta I_1$ , where  $\beta$  is a constant.

As in Problem 1.16,

$$V_{Th} = V_1|_{I_1=0} = z_{22}I_2$$

But if  $I_1 = 0$ , (1.9) and the defining relationship for the controlled source lead to

$$V_2 = \beta I_1 = 0 = z_{22} I_2$$

from which  $I_2 = 0$  and, hence,  $V_{Th} = 0$ .

Now we let  $V_1 = V_{dp}$ , so that  $I_1 = I_{dp}$ , and we determine  $Z_{Th}$  as the driving-point impedance. From (1.8), (1.9), and the defining relationship for the controlled source, we have

$$V_1 = V_{dp} = z_{11}I_{dp} + z_{12}I_2 (1)$$

$$V_2 = \beta I_{dp} = z_{21}I_{dp} + z_{22}I_2 \tag{2}$$

Solving (2) for  $I_2$  and substituting the result into (1) yields

$$V_{dp} = z_{11}I_{dp} + z_{12} \frac{\beta - z_{21}}{z_{22}} I_{dp}$$

from which Thévenin impedance is found to be

$$Z_{Th} = \frac{V_{dp}}{I_{dp}} = \frac{z_{11}z_{22} + z_{12}(\beta - z_{21})}{z_{22}}$$

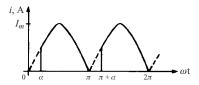

**1.18** The periodic current waveform of Fig. 1-21 is composed of segments of a sinusoid. Find (a) the average value of the current and (b) the rms (effective) value of the current.

Fig. 1-21

(a) Because i(t) = 0 for  $0 \le \omega t < \alpha$ , the average value of the current is, according to (1.20),

$$I_0 = \frac{1}{\pi} \int_{\alpha}^{\pi} I_m \sin \omega t \, d(\omega t) = \frac{I_m}{\pi} \left[ -\cos \omega t \right]_{\omega t = \alpha}^{\pi} = \frac{I_m}{\pi} \left( 1 + \cos \alpha \right)$$

(b) By (1.21) and the identity  $\sin^2 x = \frac{1}{2}(1 - \cos 2x)$ ,

$$I^{2} = \frac{1}{\pi} \int_{\alpha}^{\pi} I_{m}^{2} \sin^{2}(\omega t) d(\omega t) = \frac{I_{m}^{2}}{2\pi} \int_{\alpha}^{\pi} (1 - \cos 2\omega t) d(\omega t)$$

$$= \frac{I_{m}^{2}}{2\pi} \left[ \omega t - \frac{1}{2} \sin 2\omega t \right]_{\omega t = \alpha}^{\pi} = \frac{I_{m}^{2}}{2\pi} \left( \pi - \alpha + \frac{1}{2} \sin 2\alpha \right)$$

so that

$$I = I_m \sqrt{\frac{\pi - \alpha + \frac{1}{2}\sin 2\alpha}{2\pi}}$$

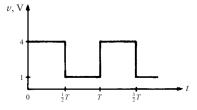

**1.19** Assume that the periodic waveform of Fig. 1-22 is a current (rather than a voltage). Find (a) the average value of the current and (b) the rms value of the current.

Fig. 1-22

(a) The integral in (1.20) is simply the area under the f(t) curve for one period. We can, then, find the average current as

$$I_0 = \frac{1}{T} \left( 4 \times \frac{T}{2} + 1 \times \frac{T}{2} \right) = 2.5 \,\text{A}$$

(b) Similarly, the integral in (1.21) is no more than the area under the  $f^2(t)$  curve. Hence,

$$I = \left[\frac{1}{T}\left(4^2 \frac{T}{2} + 1^2 \frac{T}{2}\right)\right]^{1/2} = 4.25 \text{ A}$$

**1.20** Calculate the average and rms values of the current  $i(t) = 4 + 10 \sin \omega t A$ .

Since i(t) has period  $2\pi$ , (1.20) gives

$$I_0 = \frac{1}{2\pi} \int_0^{2\pi} (4 + 10\sin\omega t) d(\omega t) = \frac{1}{2\pi} [4\omega t - 10\cos\omega t]_{\omega t = 0}^{2\pi} = 4 \text{ A}$$

This result was to be expected, since the average value of a sinusoid over one cycle is zero. Equation (1.21) and the identity  $\sin^2 x = \frac{1}{2}(1 - \cos 2x)$  provide the rms value of i(t):

$$I^{2} = \frac{1}{2\pi} \int_{0}^{2\pi} (4 + 10\sin\omega t)^{2} d(\omega t) = \frac{1}{2\pi} \int_{0}^{2\pi} (16 + 80\sin\omega t + 50 - 50\cos2\omega t) d(\omega t)$$

$$= \frac{1}{2\pi} \left[ 66\omega t - 80\cos\omega t - \frac{50}{2}\sin2\omega t \right]_{\omega t = 0}^{2\pi} = 66$$

so that  $I = \sqrt{66} = 8.125 \,\text{A}$ .

**1.21** Find the rms (or effective) value of a current consisting of the sum of two sinusoidally varying functions with frequencies whose ratio is an integer.

Without loss of generality, we may write

$$i(t) = I_1 \cos \omega t + I_2 \cos k\omega t$$

where k is an integer. Applying (1.21) and recalling that  $\cos^2 x = \frac{1}{2}(1 + \cos 2x)$  and  $\cos x \cos y = \frac{1}{2}[\cos(x+y) + \cos(x-y)]$ , we obtain

$$I^{2} = \frac{1}{2\pi} \int_{0}^{2\pi} (I_{1}\cos\omega t + I_{2}\cos k\omega t)^{2} d(\omega t)$$

$$= \frac{1}{2\pi} \int_{0}^{2\pi} \left\{ \frac{I_{1}^{2}}{2} (1 + \cos 2\omega t) + \frac{I_{2}^{2}}{2} (1 + \cos 2k\omega t) + I_{1}I_{2}[\cos(k+1)\omega t + \cos(k-1)\omega t] \right\} d(\omega t)$$

Performing the indicated integration and evaluating at the limits results in

$$I = \sqrt{\frac{I_1^2}{2} + \frac{I_2^2}{2}}$$

1.22 Find the average value of the power delivered to a one-port network with passive sign convention (that is, the current is directed from the positive to the negative terminal) if  $v(t) = V_m \cos \omega t$  and  $i(t) = I_m \cos(\omega t + \theta)$ .

The instantaneous power flow into the port is given by

$$p(t) = v(t)i(t) = V_m I_m \cos \omega t \cos(\omega t + \theta)$$

=  $\frac{1}{2} V_m I_m [\cos(2\omega t + \theta) + \cos \theta]$

By (1.20),

$$P_0 = \frac{1}{2\pi} \int_0^{2\pi} p(t) \, dt = \frac{V_m}{4\pi} \, I_m \int_0^{2\pi} \left[ \cos(2\omega t + \theta) + \cos \theta \right] d(\omega t)$$

After the integration is performed and its limits evaluated, the result is

$$P_0 = \frac{V_m I_m}{2} \cos \theta = \frac{V_m}{\sqrt{2}} \frac{I_m}{\sqrt{2}} \cos \theta = VI \cos \theta$$

#### **Supplementary Problems**

- **1.23** Prove that the capacitor element of Fig. 1-1(c) is a linear element by showing that it satisfies the converse of the superposition theorem. (*Hint*: See Problem 1.1.)

- 1.24 Use the superposition theorem to find the current i in Fig. 1-14 if  $R_1 = 5 \Omega$ ,  $R_2 = 10 \Omega$ ,  $V_s = 10 \cos 2t V$ , and  $I_s = 3\cos(3t + \pi/4) A$ . Ans.  $i = 0.667 \cos 2t + \cos(3t + \pi/4) A$

- 1.25 In Fig. 1-23, (a) find the Thévenin equivalent voltage and impedance for the network to the left of terminals a, b, and (b) use the Thévenin equivalent circuit to determine the current I<sub>L</sub>.

Ans. (a) V<sub>Th</sub> = V<sub>1</sub> I<sub>2</sub>R<sub>2</sub>, Z<sub>Th</sub> = R<sub>1</sub> + R<sub>2</sub>; (b) I<sub>L</sub> = (V<sub>1</sub> I<sub>2</sub>R<sub>2</sub>)/(R<sub>1</sub> + R<sub>2</sub> + R<sub>L</sub>)

Fig. 1-23

- 1.26 In the circuit of Fig. 1-18,  $V_1 = 10\cos 2t$  V,  $V_2 = 20\cos 2t$  V, L = 1 H, C = 1 F, and the load is a 1- $\Omega$  resistor. (a) Determine the Thévenin equivalent for the network to the right of terminals a, b. (b) Use the Thévenin equivalent to find the load current  $\bar{I}_L$ . (Hint: The results of Problem 1.10 can be used here with s = j2.) Ans. (a)  $\bar{V}_{Th} = 23.33320^{\circ}$  V,  $Z_{Th} = -j0.667\Omega$ ; (b)  $\bar{I}_L = 19.4233.69^{\circ}$  A.

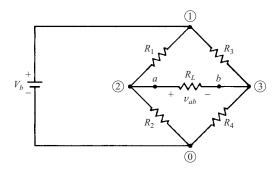

- 1.27 In Fig. 1-24, find the Thévenin equivalent for the bridge circuit as seen through the load resistor  $R_L$ . Ans.  $V_{Th} = V_b(R_2R_3 R_1R_4)/(R_1 + R_2)(R_3 + R_4)$ ,  $Z_{Th} = R_1R_2/(R_1 + R_3) + R_2R_4/(R_2 + R_4)$

Fig. 1-24

- 1.28 Suppose the bridge circuit in Fig. 1-24 is balanced by letting  $R_1 = R_2 = R_3 = R_4 = R$ . Find the elements of the Norton equivalent circuit. Ans.  $I_N = 0$ ,  $Y_N = 1/R$

- 1.29 Use SPICE methods to determine voltage  $v_{ab}$  for the circuit of Fig. 1-24 if  $V_b = 20 \text{ V}$ ,  $R_L = 10 \Omega$ ,  $R_1 = 1 \Omega$ ,  $R_2 = 2 \Omega$ ,  $R_3 = 3 \Omega$ , and  $R_4 = 4 \Omega$ . (Netlist code available at author download site.)

Ans.  $v_{ab} = V(2, 3) = 1.538 \text{ V}$

1.30 For the circuit of Fig. 1-25, (a) determine the Thévenin equivalent of the circuit to the left of terminals a, b, and (b) use the Thévenin equivalent to find the load current  $i_L$ .

Ans. (a)  $V_{Th} = 120 \text{ V}, Z_{Th} = 20 \Omega;$  (b)  $i_L = 4 \text{ A}$

Fig. 1-25

- 1.31 Apply SPICE methods to determine load current  $i_L$  for the circuit of Fig. 1-25 if (a) the element values are as shown and (b) the VCCS has a value of  $0.5v_{ab}$  with all else unchanged. (Netlist code available at author download site.) Ans. (a)  $i_L = 4 \text{ A}$ ; (b)  $i_L = -6 \text{ A}$

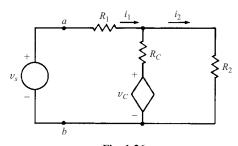

- 1.32 In the circuit of Fig. 1-26, let  $R_1 = R_2 = R_C = 1 \Omega$  and find the Thévenin equivalent for the circuit to the right of terminals a, b (a) if  $v_C = 0.5i_1$  and (b) if  $v_C = 0.5i_2$ .

Ans. (a)  $V_{Th} = 0$ ,  $Z_{Th} = R_{Th} = 1.75 \Omega$ ; (b)  $V_{Th} = 0$ ,  $Z_{Th} = R_{Th} = 1.667 \Omega$

Fig. 1-26

- Find the Thévenin equivalent for the network to the left of terminals a, b in Fig. 1-15 (a) if k = 0, and 1.33 (b) if k = 0.1. Use the Thévenin equivalent to verify the results of Problem 1.4. Ans. (a)  $V_{Th} = -200 \text{ V}, Z_{Th} = R_{Th} = 100 \Omega;$  (b)  $V_{Th} = -250 \text{ V}, Z_{Th} = R_{Th} = 125 \Omega$

- Find the Thévenin equivalent for the circuit to the left of terminals a, b in Fig. 1-16, and use it to verify the 1.34 Ans.  $V_{Th} = \frac{1}{2}(1+\alpha)v_s$ ,  $Z_{Th} = R_{Th} = \frac{1}{2}(3-\alpha)\Omega$ results of Problem 1.6.

- 1.35 An alternative solution for Problem 1.3 involves finding a Thévenin equivalent circuit which, when connected across the nonlinear  $R_2 = 0.25i$ , allows a quadratic equation in current i to be written via KVL. Find the elements of the Thévenin circuit and the resulting current. Ans.  $V_{Th} = 25 \text{ V}, Z_{Th} = R_{Th} = 5 \Omega, i = 4.142 \text{ A}$

- 1.36 Use (1.10) to (1.15) to find expressions for the z parameters in terms of the h parameters. Ans.  $z_{11} = h_{11} - h_{12}h_{21}/h_{22}$ ,  $z_{12} = h_{12}/h_{22}$ ,  $z_{21} = -h_{21}/h_{22}$ ,  $z_{22} = 1/h_{22}$

- 1.37 For the two-port network of Fig. 1-20, (a) find the voltage-gain ratio  $V_2/V_1$  in terms of the z parameters, and then (b) evaluate the ratio, using the h-parameter values given in Problem 1.15 and the results of Problem 1.36. Ans. (a)  $z_{21}R_L/(z_{11}R_L+z_{11}z_{22}-z_{12}z_{21})$ ; (b) -200

- 1.38 Find the current-gain ratio  $I_2/I_1$  for the two-port network of Fig. 1-20 in terms of the *h* parameters. Ans.  $h_{21}/(1 + h_{22}R_L)$

- 1.39 Find the current-gain ratio  $I_2/I_1$  for the two-port network of Fig. 1-20 in terms of the z parameters. Ans.  $-z_{21}/(z_{22} + R_L)$

- 1.40 Determine the Thévenin equivalent voltage and impedance, in terms of the z parameters, looking right into port 1 of the two-port network of Fig. 1-20 if  $R_L$  is replaced with an independent dc voltage source  $V_d$ , connected such that  $V_2 = V_d$ . Ans.  $V_{Th} = z_{12}V_d/z_{22}$ ,  $Z_{Th} = (z_{11}z_{22} z_{12}z_{21})/z_{22}$

- 1.41 Find the Thévenin equivalent voltage and impedance, in terms of the h parameters, looking right into port 1 of the network of Fig. 1-20 if  $R_L$  is replaced with a voltage-controlled current source such that  $I_2 = -\alpha V_1$ , where  $\alpha > 0$  and the h parameters are understood to be positive.

Ans.  $V_{Th} = 0$ ,  $Z_{Th} = (h_{11}h_{22} h_{12}h_{21})/(h_{22} + \alpha h_{12})$

- 1.42 Determine the driving-point impedance (the input impedance with all independent sources deactivated) of the two-port network of Fig. 1-20. Ans.  $(z_{11}R_L + z_{11}z_{22} z_{12}z_{21})/(z_{22} + R_L)$

- 1.43 Evaluate the z parameters of the network of Fig. 1-16. Ans.  $z_{11} = 2 \Omega$ ,  $z_{12} = 1 \Omega$ ,  $z_{21} = \alpha + 1 \Omega$ ,  $z_{22} = 2 \Omega$

- **1.44** Find the current  $i_1$  in Fig. 1-3 if  $\alpha = 2$ ,  $R_1 = R_2 = R_3 = 1 \Omega$ ,  $V_b = 10 \text{ V}$ , and  $v_s = 10 \sin \omega t \text{ V}$ . Ans. -2 A

- 1.45 For a one-port network with passive sign convention (see Problem 1.22),  $v = V_m \cos \omega t V$  and  $i = I_1 + I_2 \cos(\omega t + \theta) A$ . Find (a) the instantaneous power flowing to the network and (b) the average power to the network. Ans. (a)  $V_m I_1 \cos \omega t + \frac{1}{2} V_m I_2 [\cos(2\omega t + \theta) + \cos \theta]$ ; (b)  $\frac{1}{2} V_m I_2 \cos \theta$

# **Semiconductor Diodes**

### 2.1. INTRODUCTION

Diodes are among the oldest and most widely used of electronic devices. A *diode* may be defined as a near-unidirectional conductor whose state of conductivity is determined by the polarity of its terminal voltage. The subject of this chapter is the *semiconductor diode*, formed by the metallurgical junction of *p*-type and *n*-type materials. (A *p*-type material is a group-IV element *doped* with a small quantity of a group-V material; *n*-type material is a group-IV base element doped with a group-III material.)

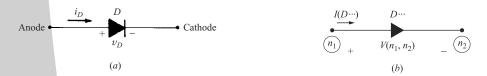

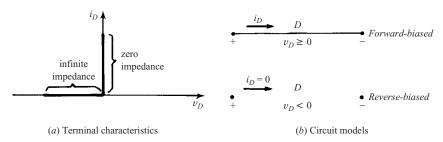

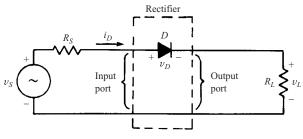

### 2.2. THE IDEAL DIODE

The symbol for the *common*, or *rectifier*, *diode* is shown in Fig. 2-1(a). The device has two terminals, labeled *anode* (p-type) and *cathode* (n-type), which makes understandable the choice of *diode* as its name. When the terminal voltage is nonnegative  $(v_D \ge 0)$ , the diode is said to be *forward-biased* or "on"; the positive current that flows  $(i_D \ge 0)$  is called *forward current*. When  $v_D < 0$ , the diode is said to be *reverse-biased* or "off," and the corresponding small negative current is referred to as *reverse current*.

Fig. 2-1

The ideal diode is a perfect two-state device that exhibits zero impedance when forward-biased and infinite impedance when reverse-biased (Fig. 2-2). Note that since either current or voltage is zero at any instant, no power is dissipated by an ideal diode. In many circuit applications, diode forward voltage drops and reverse currents are small compared to other circuit variables; then, sufficiently accurate results are obtained if the actual diode is modeled as ideal.

The ideal diode analysis procedure is as follows:

- Step 1: Assume forward bias, and replace the ideal diode with a short circuit.

- Step 2: Evaluate the diode current  $i_D$ , using any linear circuit-analysis technique.

- Step 3: If  $i_D \ge 0$ , the diode is actually forward-biased, the analysis is valid, and step 4 is to be omitted.

Fig. 2-2 Ideal diode

Step 4: If  $i_D < 0$ , the analysis so far is invalid. Replace the diode with an open circuit, forcing  $i_D = 0$ , and solve for the desired circuit quantities using any method of circuit analysis. Voltage  $v_D$  must be found to have a negative value.

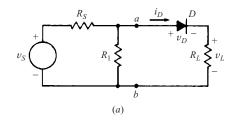

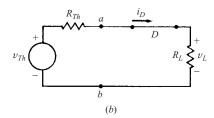

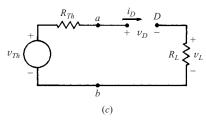

**Example 2.1.** Find voltage  $v_L$  in the circuit of Fig. 2-3(a), where D is an ideal diode.

The analysis is simplified if a Thévenin equivalent is found for the circuit to the left of terminals a, b; the result is

$$v_{Th} = \frac{R_1}{R_1 + R_S} v_s$$

and  $Z_{Th} = R_{Th} = R_1 \| R_S = \frac{R_1 R_S}{R_1 + R_S}$

Fig. 2-3

Step 1: After replacing the network to the left of terminals a, b with the Thévenin equivalent, assume forward bias and replace diode D with a short circuit, as in Fig. 2-3(b).

Step 2: By Ohm's law,

$$i_D = \frac{v_{Th}}{R_{Th} + R_L}$$

Step 3: If  $v_S \ge 0$ , then  $i_D \ge 0$  and

$$v_L = i_D R_L = \frac{R_L}{R_L + R_{Th}} \, v_{Th}$$

Step 4: If  $v_S < 0$ , then  $i_D < 0$  and the result of step 3 is invalid. Diode D must be replaced by an open circuit as illustrated in Fig. 2-3(c), and the analysis performed again. Since now  $i_D = 0$ ,  $v_L = i_D R_L = 0$ . Since  $v_D = v_S < 0$ , the reverse bias of the diode is verified.

(See Problem 2.4 for an extension of this procedure to a multidiode circuit.)

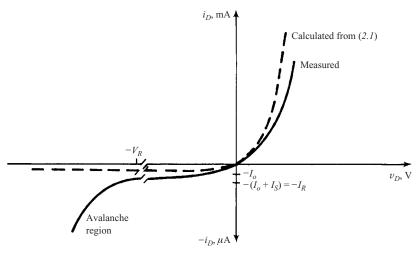

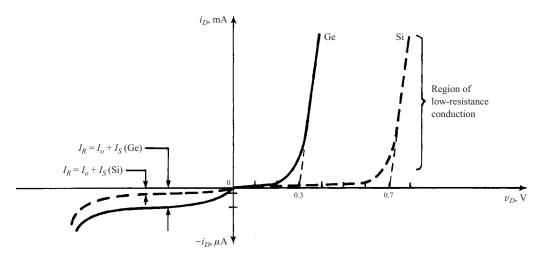

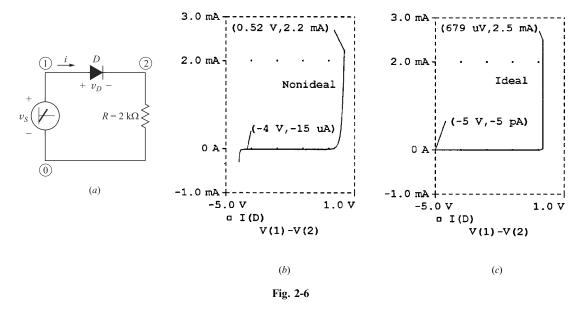

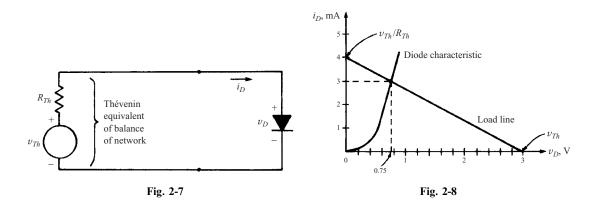

### 2.3. DIODE TERMINAL CHARACTERISTICS

Use of the Fermi-Dirac probability function to predict charge neutralization gives the *static* (non-time-varying) equation for diode junction current:

$$i_D = I_o(e^{v_D/\eta V_T} - 1)$$

A (2.1)

where  $V_T \equiv kT/q$ , V

$v_D \equiv$  diode terminal voltage, V

$I_o \equiv$  temperature-dependent saturation current, A

$T \equiv$  absolute temperature of *p-n* junction, K

$k \equiv \text{Boltzmann's constant } (1.38 \times 10^{-23} \text{ J/K})$

$q \equiv \text{electron charge } (1.6 \times 10^{-19} \,\text{C})$

$\eta \equiv$  empirical constant, 1 for Ge and 2 for Si

### **Example 2.2.** Find the value of $V_T$ in (2.1) at $20^{\circ}$ C.

Recalling that absolute zero is  $-273^{\circ}$ C, we write

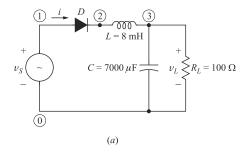

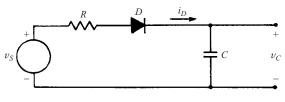

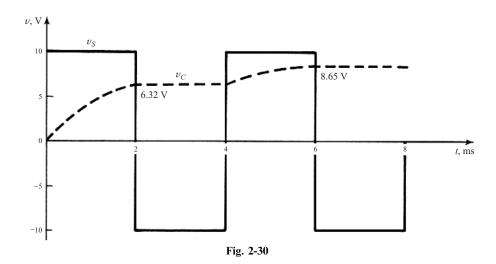

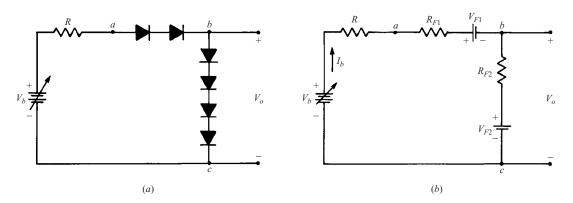

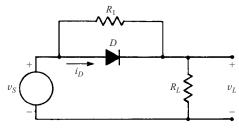

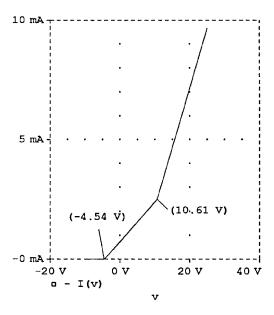

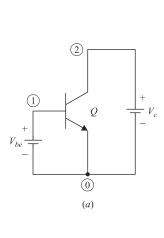

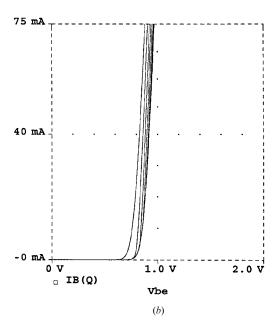

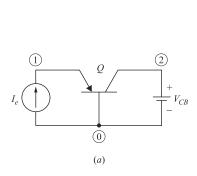

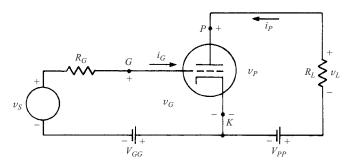

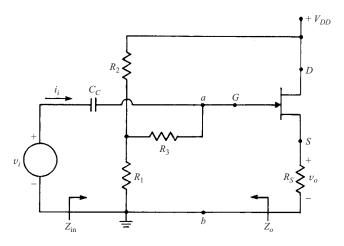

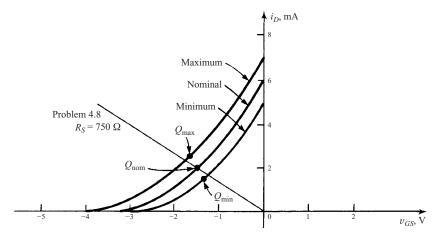

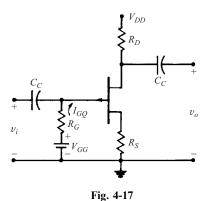

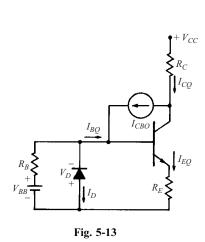

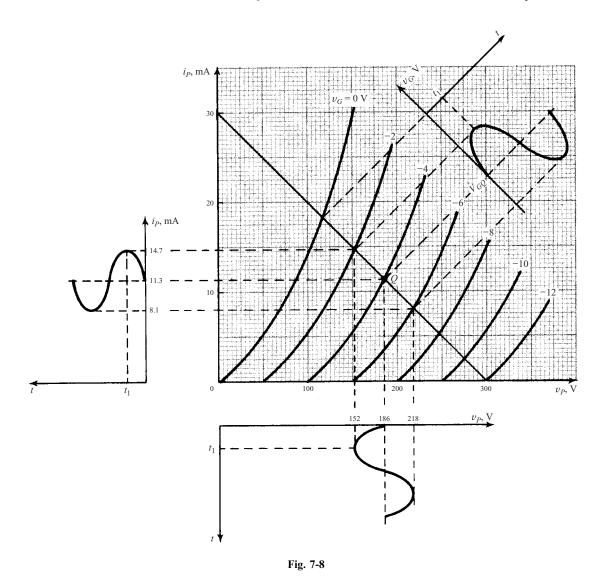

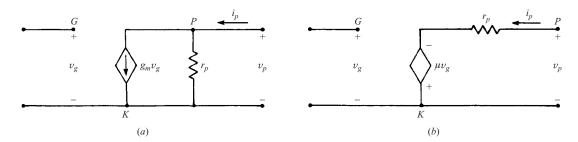

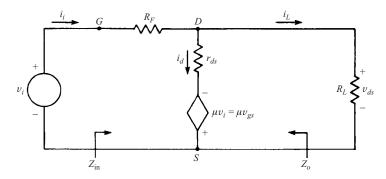

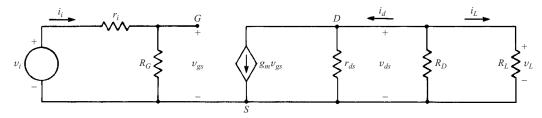

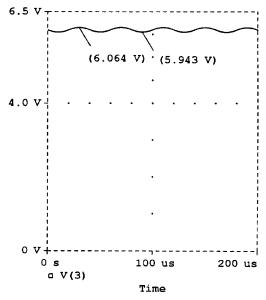

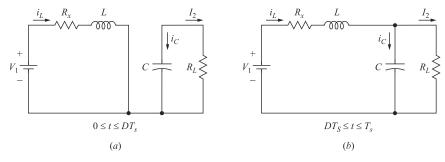

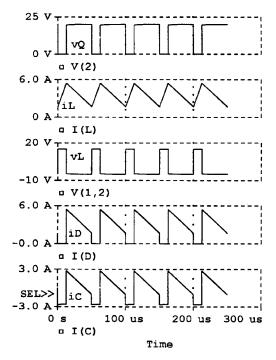

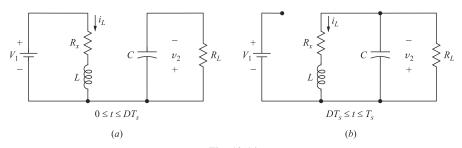

$$V_T = \frac{kT}{q} = \frac{(1.38 \times 10^{-23})(273 + 20)}{1.6 \times 10^{-19}} = 25.27 \,\text{mV}$$