# Fundamentals of Power Electronics Second Edition

# Fundamentals of Power Electronics

SECOND EDITION

# Fundamentals of Power Electronics

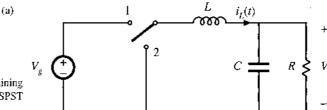

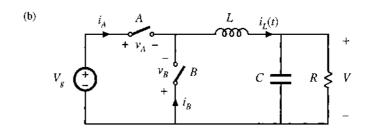

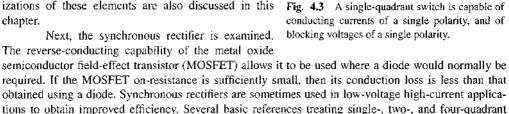

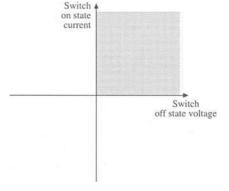

SECOND EDITION

Robert W. Erickson Dragan Maksimović University of Colorado Boulder, Colorado

#### Distributors for North, Central and South America:

Kluwer Academic Publishers 101 Philip Drive Assinippi Park Norwell, Massachusetts 02061 USA Telephone (781) 871-6600 Fax (781) 871-6528 E-Mail <kluwer@wkap.com>

#### Distributors for all other countries:

Kluwer Academic Publishers Group Distribution Centre Post Office Box 322 3300 AH Dordrecht, THE NETHERLANDS Telephone 31 78 6576 000 Fax 31 78 6576 254 E-Mail services@wkap.nl>

Electronic Services <a href="http://www.wkap.nl">http://www.wkap.nl</a>

#### Library of Congress Cataloging-in-Publication

Erickson, Robert W. (Robert Warren), 1956-

Fundamentals of power electronics / Robert W. Erickson, Dragan Maksimovic.--2nd ed. p. cm.

Includes bibliographical references and index.

ISBN 978-1-4757-0559-1

ISBN 978-0-306-48048-5 (eBook)

DOI 10.1007/978-0-306-48048-5

1. Power electronics. 1. Maksimovic, Dragan, 1961- II. Title.

TK7881.15 .E75 2000 621.381--dc21

00-052569

Copyright © 2001 by Kluwer Academic Publishers. Sixth Printing 2004.

Cover art Copyright \* 1999 by Lucent Technologies Inc. All rights reserved. Used with permission.

Softcover reprint of the hardcover 2nd edition 2001 978-0-7923-7270-7

All rights reserved. No part of this publication may be reproduced, stored in a retrieval system or transmitted in any form or by any means, mechanical, photo-copying, recording, or otherwise, without the prior written permission of the publisher, Kluwer Academic Publishers, 101 Philip Drive, Assinippi Park, Norwell, Massachusetts 02061

Printed on acid-free paper.

Dedicated to Linda, William, and Richard Lidija, Filip, Nikola, and Stevan

## Contents

| Pre | erace |                                                                              | XIX |

|-----|-------|------------------------------------------------------------------------------|-----|

| 1   | Intro | oduction                                                                     | 1   |

|     | 1.1   | Introduction to Power Processing                                             | 1   |

|     | 1.2   | Several Applications of Power Electronics                                    | 7   |

|     | 1.3   | Elements of Power Electronics                                                | 9   |

|     | Refe  | erences                                                                      |     |

| I   | Con   | verters in Equilibrium                                                       | 11  |

| 2   | Prin  | ciples of Steady State Converter Analysis                                    | 13  |

|     | 2.1   | Introduction                                                                 | 13  |

|     | 2.2   | Inductor Volt-Second Balance, Capacitor Charge Balance, and the Small-Ripple |     |

|     |       | Approximation                                                                | 15  |

|     | 2.3   | Boost Converter Example                                                      | 22  |

|     | 2.4   | Ćuk Converter Example                                                        | 27  |

|     | 2.5   | Estimating the Output Voltage Ripple in Converters Containing Two-Pole       |     |

|     |       | Low-Pass Filters                                                             | 31  |

|     | 2.6   | Summary of Key Points                                                        | 34  |

|     | Refe  | rences                                                                       | 34  |

|     | Prob  | lems                                                                         | 35  |

| 3   | Stea  | dy-State Equivalent Circuit Modeling, Losses, and Efficiency                 | 39  |

|     | 3.1   | The DC Transformer Model                                                     | 39  |

|     | 3.2   | Inclusion of Inductor Copper Loss                                            | 42  |

|     | 2.2   | Construction of Equipolant Circuit Model                                     | 4.5 |

|   |                                   | 3.3.1           | Inductor Voltage Equation                                                                           | 46                |  |

|---|-----------------------------------|-----------------|-----------------------------------------------------------------------------------------------------|-------------------|--|

|   |                                   | 3.3.2           | Capacitor Current Equation                                                                          | 46                |  |

|   |                                   | 3.3.3           | Complete Circuit Model                                                                              | 47                |  |

|   |                                   | 3.3.4           | Efficiency                                                                                          | 48                |  |

|   | 3.4                               | How to          | o Obtain the Input Port of the Model                                                                | 50                |  |

|   | 3.5                               |                 | ole: Inclusion of Semiconductor Conduction Losses in the Boost                                      |                   |  |

|   |                                   | Conve           | rter Model                                                                                          | 52                |  |

|   | 3.6                               | Summ            | ary of Key Points                                                                                   | 56                |  |

|   | Refe                              | rences          | •                                                                                                   | 56                |  |

|   | Prob                              | lems            |                                                                                                     | 57                |  |

| 4 | C4                                | ch Reali:       |                                                                                                     |                   |  |

| 4 | SWII                              | ca <b>K</b> ean | zation                                                                                              | 63                |  |

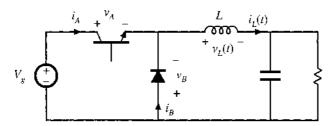

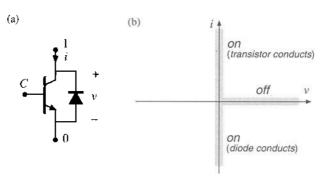

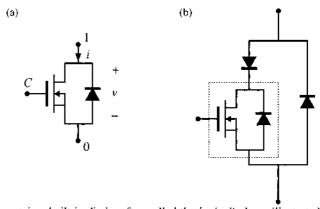

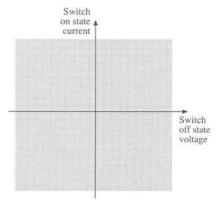

|   | 4.1                               | Switch          | Applications                                                                                        | 65                |  |

|   |                                   | 4.1.1           | Single-Quadrant Switches                                                                            | 65                |  |

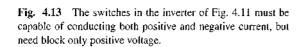

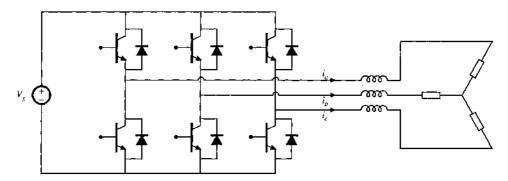

|   |                                   | 4.1.2           | Current-Bidirectional Two-Quadrant Switches                                                         | 67                |  |

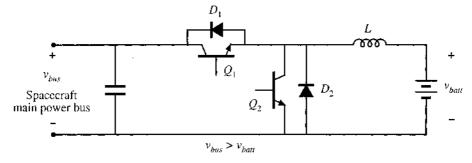

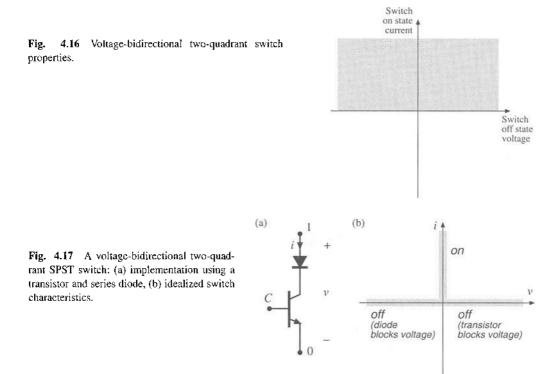

|   |                                   | 4.1.3           | Voltage-Bidirectional Two-Quadrant Switches                                                         | 71                |  |

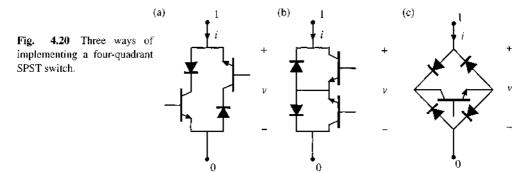

|   |                                   | 4.1.4           | Four-Quadrant Switches                                                                              | 72                |  |

|   |                                   | 4.1.5           | Synchronous Rectifiers                                                                              | 73                |  |

|   | 4.2                               | A Brie          | f Survey of Power Semiconductor Devices                                                             | 74                |  |

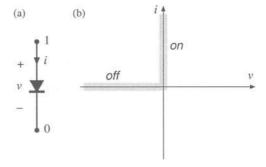

|   |                                   | 4.2.1           | Power Diodes                                                                                        | 75                |  |

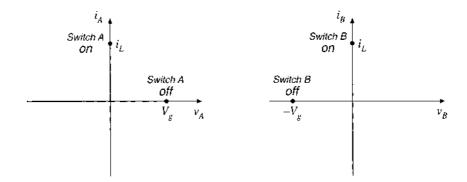

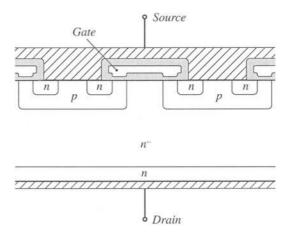

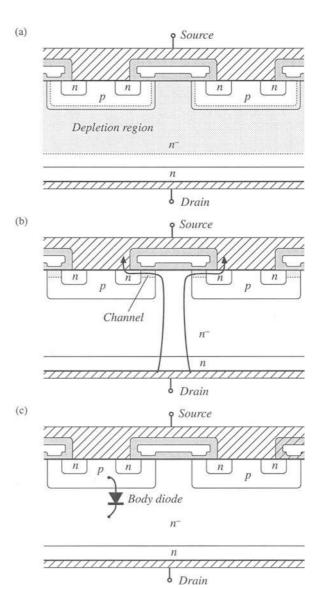

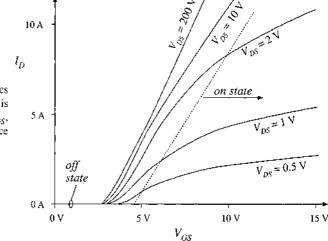

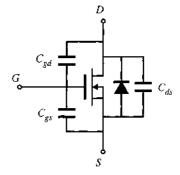

|   |                                   | 4.2.2           | Metal-Oxide-Semiconductor Field-Effect Transistor (MOSFET)                                          | 78                |  |

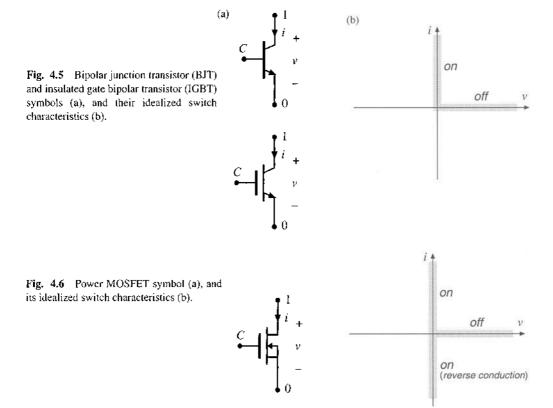

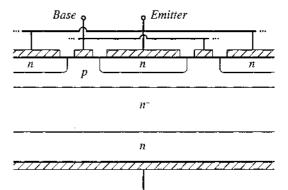

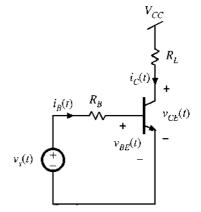

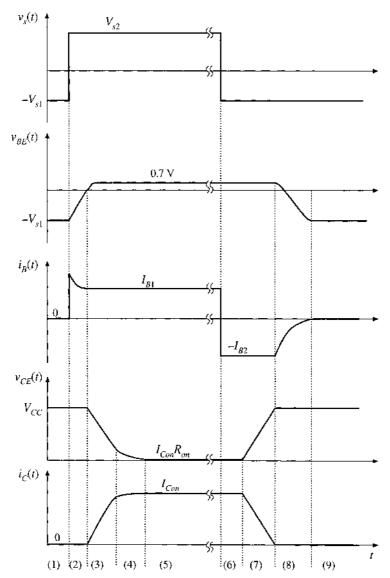

|   |                                   | 4.2.3           | Bipolar Junction Transistor (BJT)                                                                   | 81                |  |

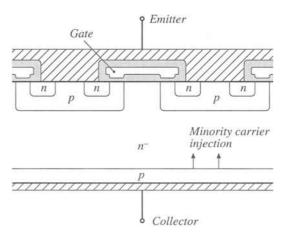

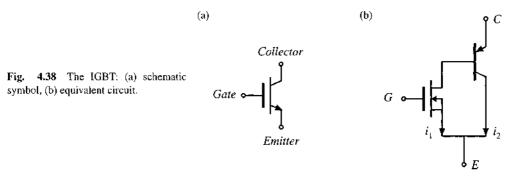

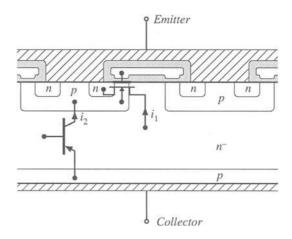

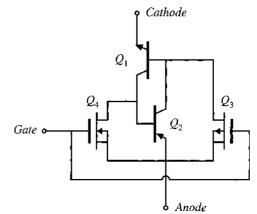

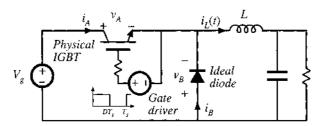

|   |                                   | 4.2.4           | Insulated Gate Bipolar Transistor (IGBT)                                                            | 86                |  |

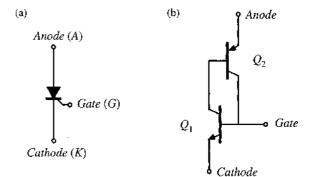

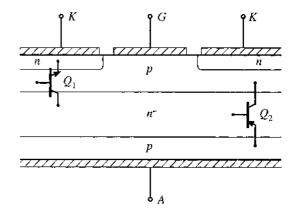

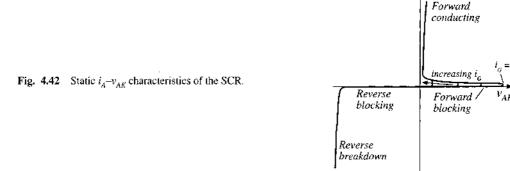

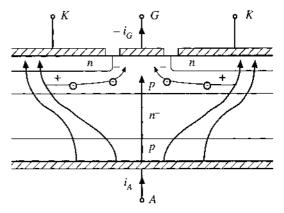

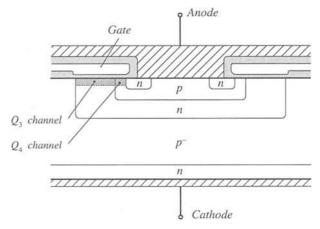

|   |                                   | 4.2.5           | Thyristors (SCR, GTO, MCT)                                                                          | 88                |  |

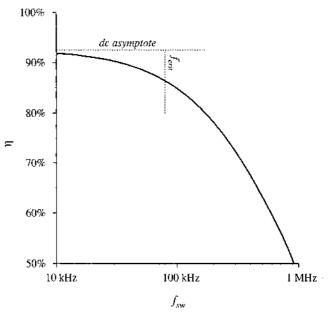

|   | 4,3                               |                 | ning Loss                                                                                           | 92                |  |

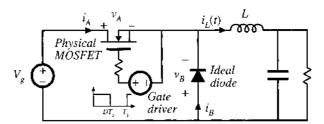

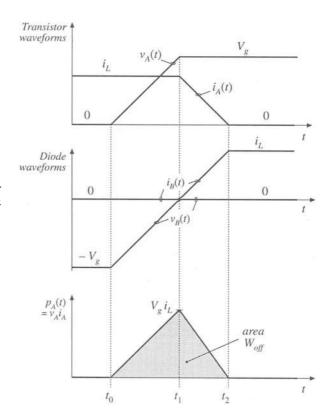

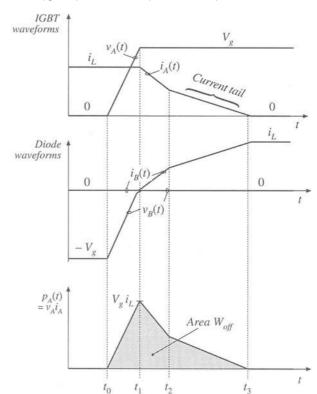

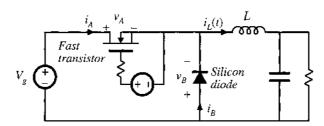

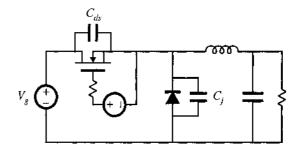

|   |                                   | 4.3.1           | Transistor Switching with Clamped Inductive Load                                                    | 93                |  |

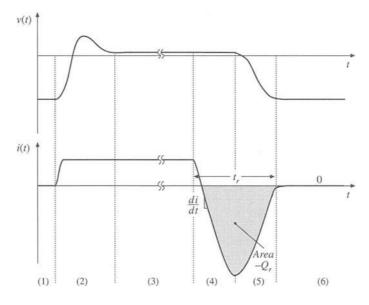

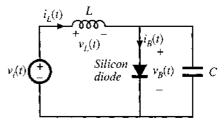

|   |                                   | 4.3.2           | Diode Recovered Charge                                                                              | 96                |  |

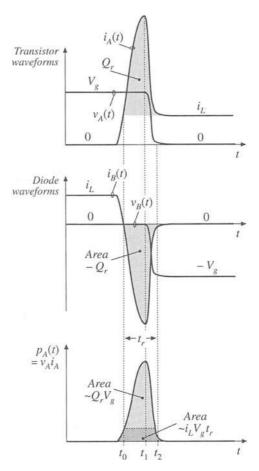

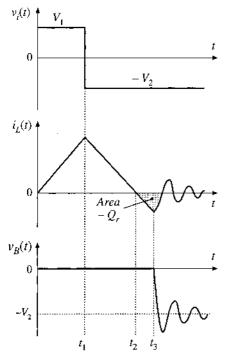

|   |                                   | 4.3.3<br>4.3.4  | Device Capacitances, and Leakage, Package, and Stray Inductances Efficiency vs. Switching Frequency | .98<br>100        |  |

|   | 4.4                               |                 | ary of Key Points                                                                                   | 101               |  |

|   |                                   | rences          | ally of Rey Folias                                                                                  | 101               |  |

|   |                                   | lems            |                                                                                                     |                   |  |

|   |                                   |                 |                                                                                                     | 103<br><b>107</b> |  |

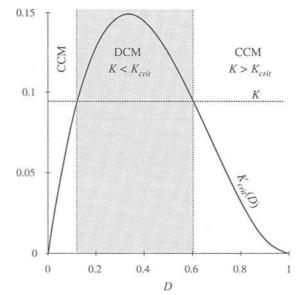

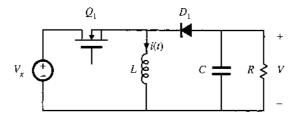

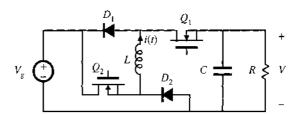

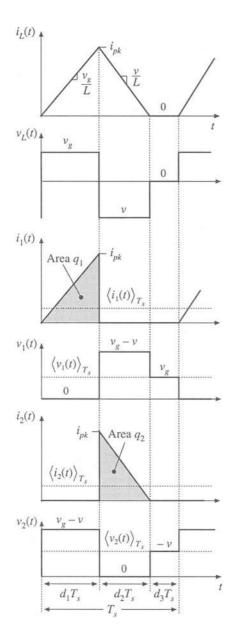

| 5 | The Discontinuous Conduction Mode |                 |                                                                                                     |                   |  |

|   | 5.1                               | Origin          | of the Discontinuous Conduction Mode, and Mode Boundary                                             | 108               |  |

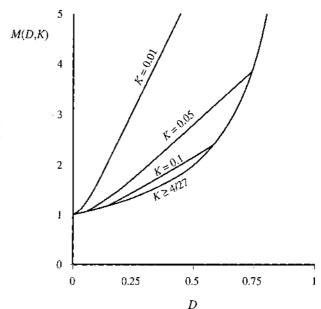

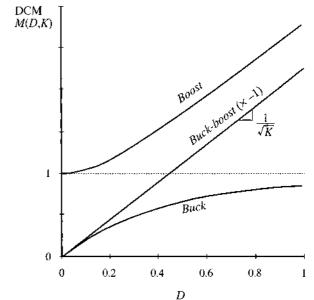

|   | 5.2                               | -               | sis of the Conversion Ratio $M(D,K)$                                                                | 112               |  |

|   | 5.3                               | -               | Converter Example                                                                                   | 117               |  |

|   | 5.4                               |                 | ary of Results and Key Points                                                                       | 124               |  |

|   |                                   | lems            | any of Results and Rey Folias                                                                       | 126               |  |

|   |                                   |                 |                                                                                                     |                   |  |

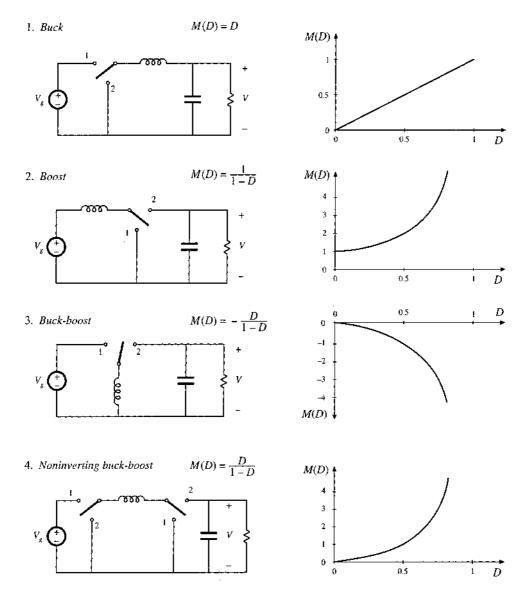

| 6 | Conv                              | erter Ci        | rcuits                                                                                              | 131               |  |

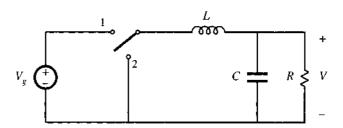

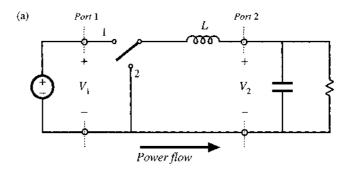

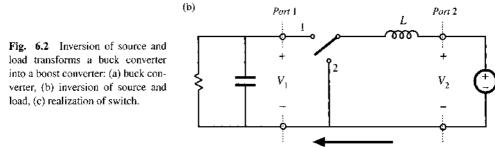

|   | 6.1                               | Circuit         | Manipulations                                                                                       | 132               |  |

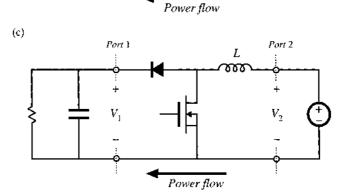

|   |                                   | 6.1.1           | Inversion of Source and Load                                                                        | 132               |  |

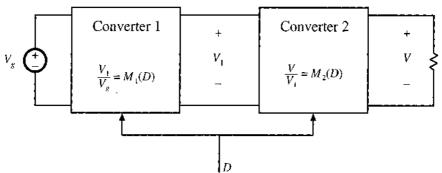

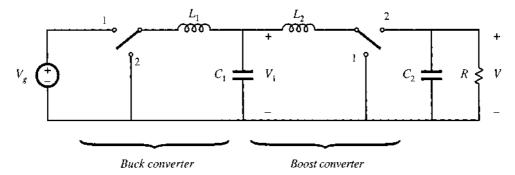

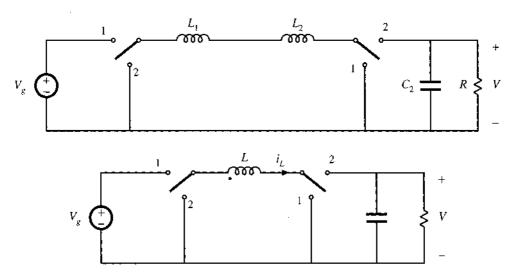

|   |                                   | 6.1.2           | Cascade Connection of Converters                                                                    | 134               |  |

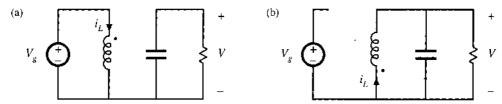

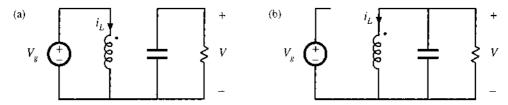

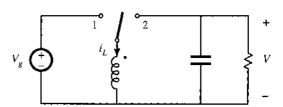

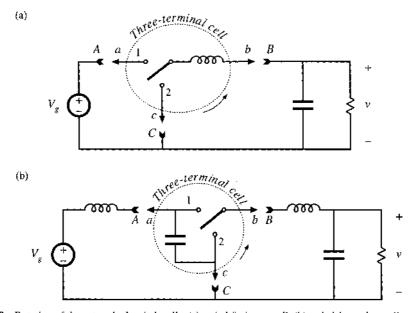

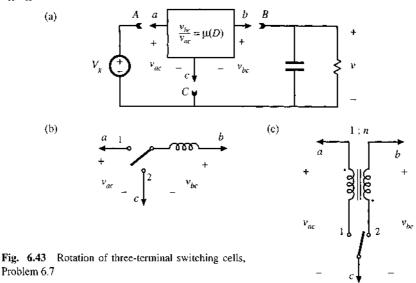

|   |                                   | 6.1.3           | Rotation of Three-Terminal Cell                                                                     | 137               |  |

| Contents | ix |

|----------|----|

|          |    |

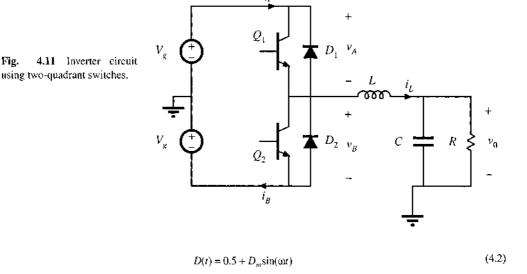

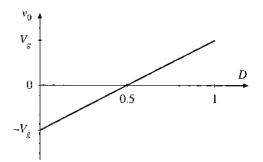

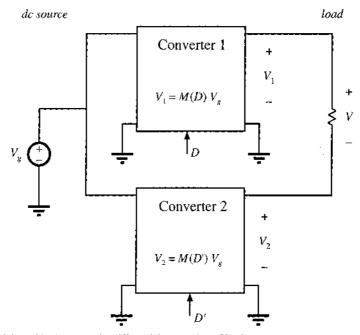

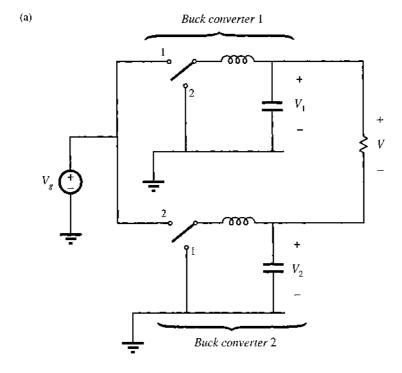

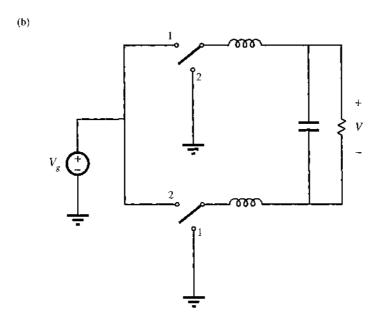

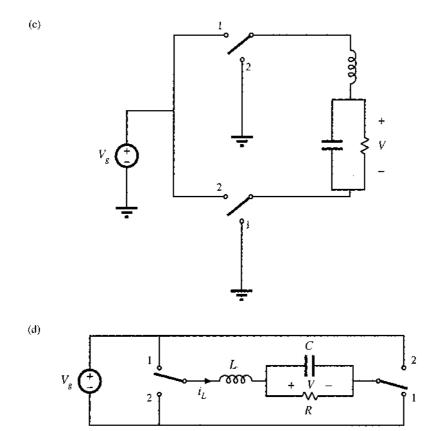

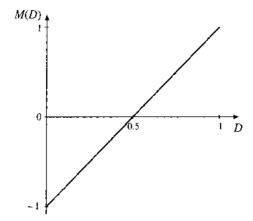

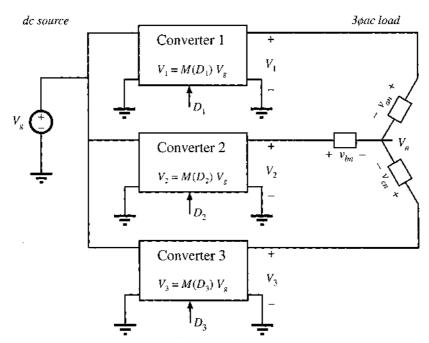

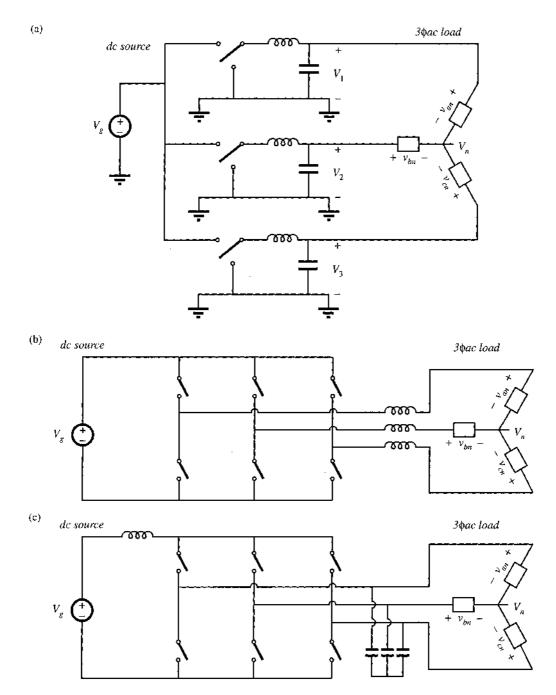

|    |      | 6.1.4          | Differential Connection of the Load                                         | 138        |

|----|------|----------------|-----------------------------------------------------------------------------|------------|

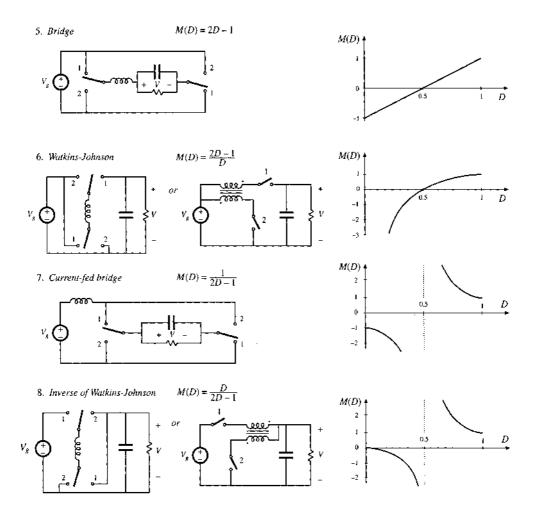

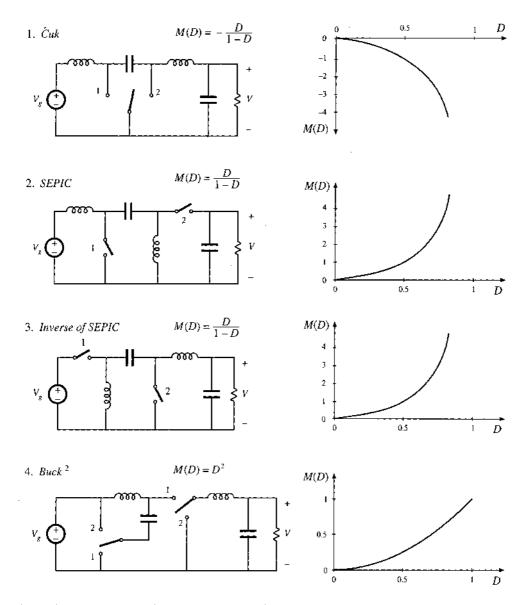

|    | 6.2  | A Shor         | rt List of Converters                                                       | 143        |

|    | 6.3  | Transfe        | ormer Isolation                                                             | 146        |

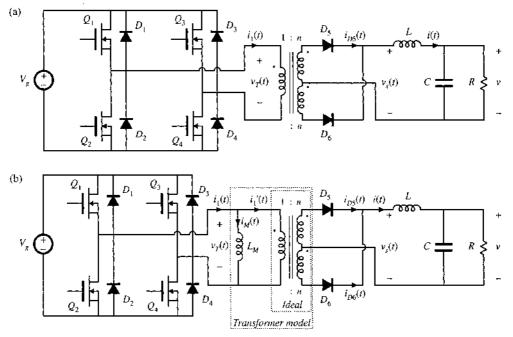

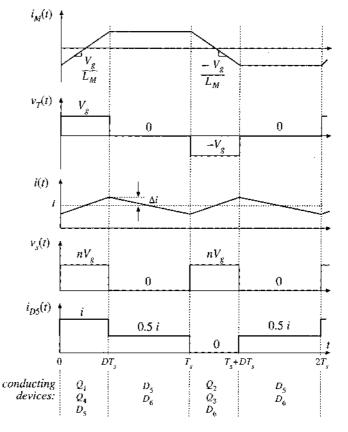

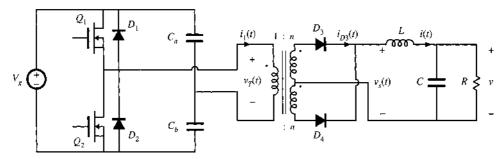

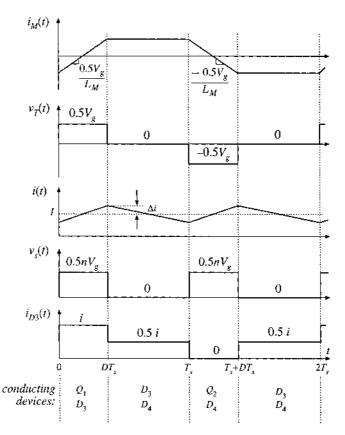

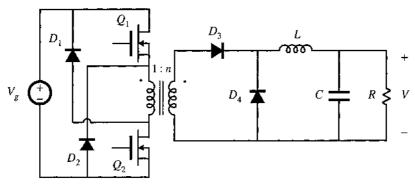

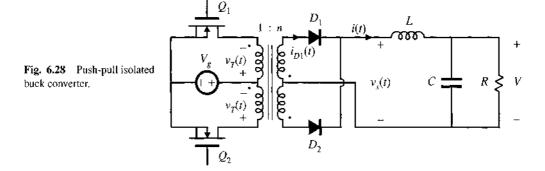

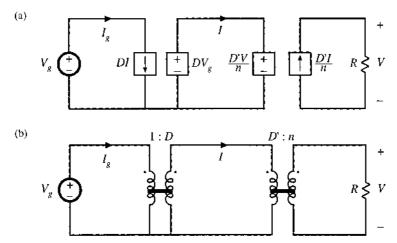

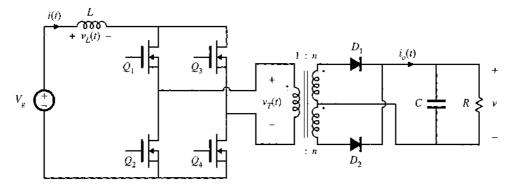

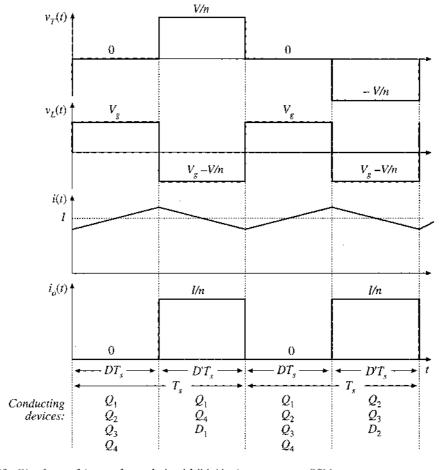

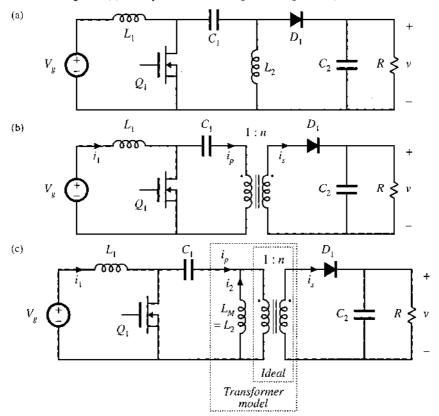

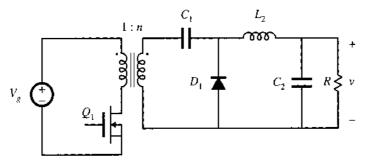

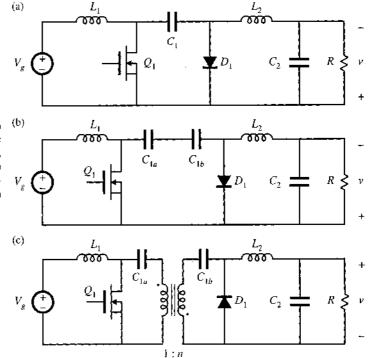

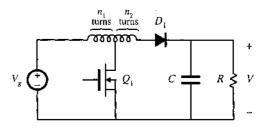

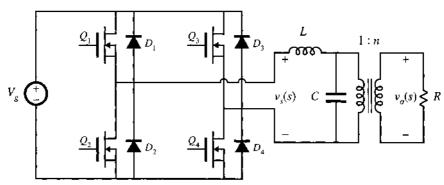

|    |      | 6.3.1          | Full-Bridge and Half-Bridge Isolated Buck Converters                        | 149        |

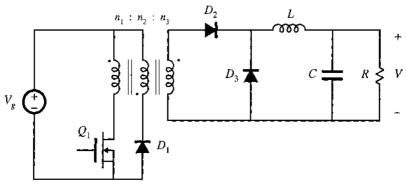

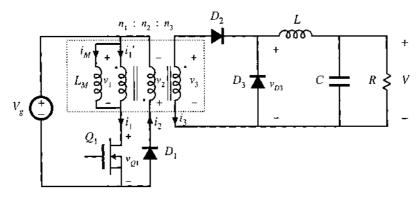

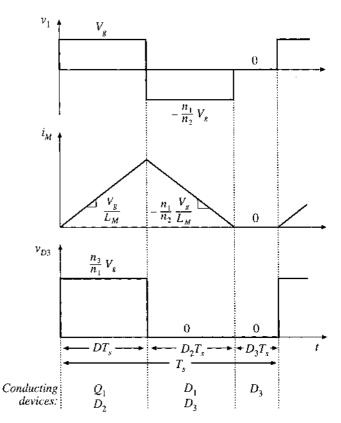

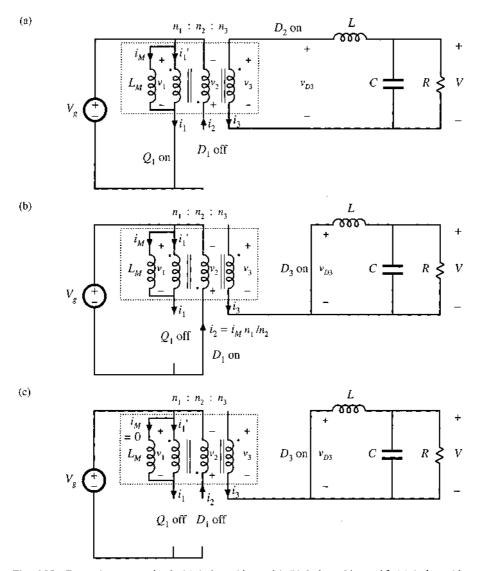

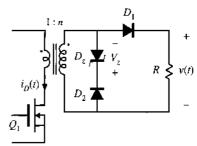

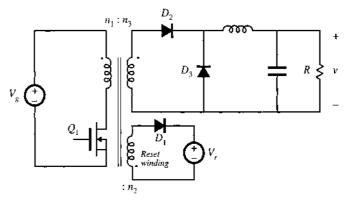

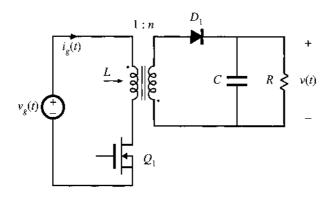

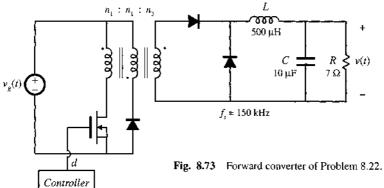

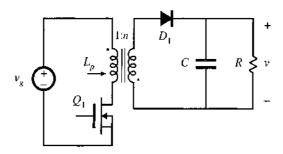

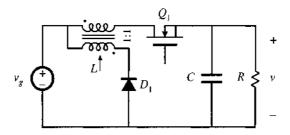

|    |      | 6.3.2          | Forward Converter                                                           | 154        |

|    |      | 6.3.3          | Push-Pull Isolated Buck Converter                                           | 159        |

|    |      | 6.3.4          | Flyback Converter                                                           | 161        |

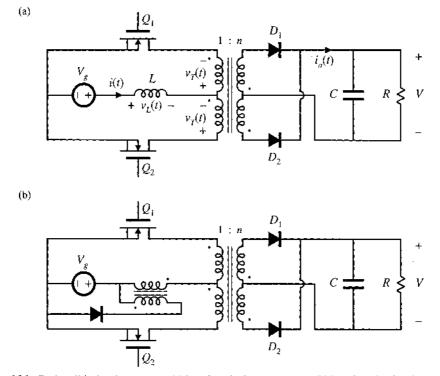

|    |      | 6.3.5          | Boost-Derived Isolated Converters                                           | 165        |

|    |      | 6.3.6          | Isolated Versions of the SEPIC and the Ćuk Converter                        | 168        |

|    | 6.4  | Conver         | rter Evaluation and Design                                                  | 171        |

|    |      | 6.4.1          | Switch Stress and Utilization                                               | 171        |

|    |      | 6.4,2          | Design Using Computer Spreadsheet                                           | 174        |

|    | 6.5  | Summa          | ary of Key Points                                                           | 177        |

|    | Refe | erences        |                                                                             | 177        |

|    | Prob | olems          |                                                                             | 179        |

| II | Con  | verter i       | Dynamics and Control                                                        | 185        |

| 7  | AC I | Equivaler      | nt Circuit Modeling                                                         | 187        |

|    | 7.1  | Introdu        | action                                                                      | 187        |

|    | 7.2  | The Ba         | sic AC Modeling Approach                                                    | 192        |

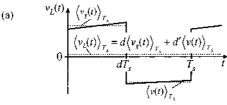

|    |      | 7.2.1          | Averaging the Inductor Waveforms                                            | 193        |

|    |      | 7.2.2          | Discussion of the Averaging Approximation                                   | 194        |

|    |      | 7.2.3          | Averaging the Capacitor Waveforms                                           | 196        |

|    |      | 7.2.4          | The Average Input Current                                                   | 197        |

|    |      | 7.2.5          | Perturbation and Linearization                                              | 197        |

|    |      | 7.2.6          | Construction of the Small-Signal Equivalent Circuit Model                   | 201        |

|    |      | 7,2.7          | Discussion of the Perturbation and Linearization Step                       | 202        |

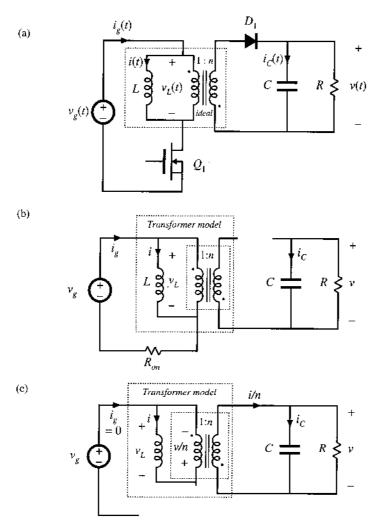

|    |      | 7.2.8<br>7.2.9 | Results for Several Basic Converters  Example: A Nonideal Flyback Converter | 204<br>204 |

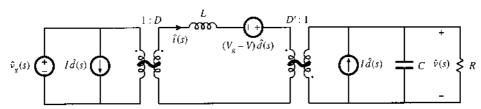

|    | 7.3  |                | Space Averaging                                                             | 213        |

|    | 1.5  | 7.3.1          |                                                                             |            |

|    |      | 7.3.1          | The State Equations of a Network The Basic State-Space Averaged Model       | 213<br>216 |

|    |      | 7.3.3          | Discussion of the State-Space Averaging Result                              | 217        |

|    |      | 7.3.4          | Example: State-Space Averaging of a Nonideal Buck-Boost Converter           | 221        |

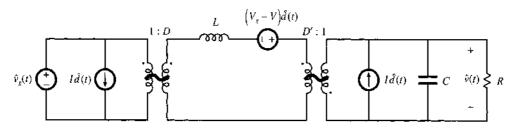

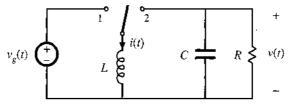

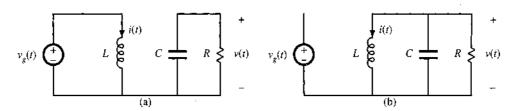

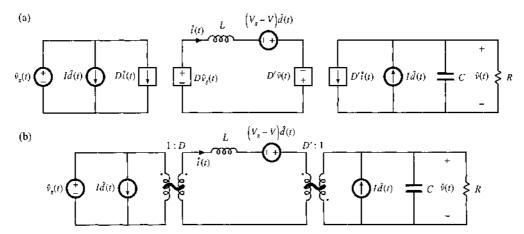

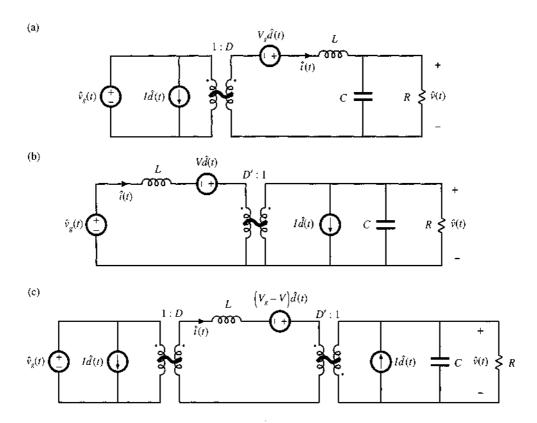

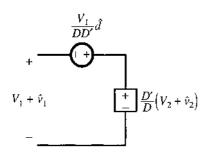

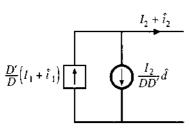

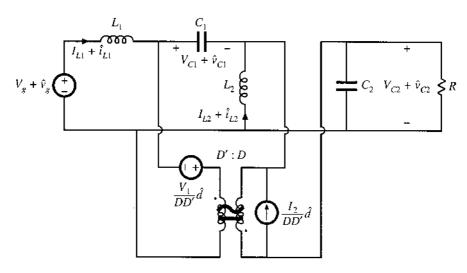

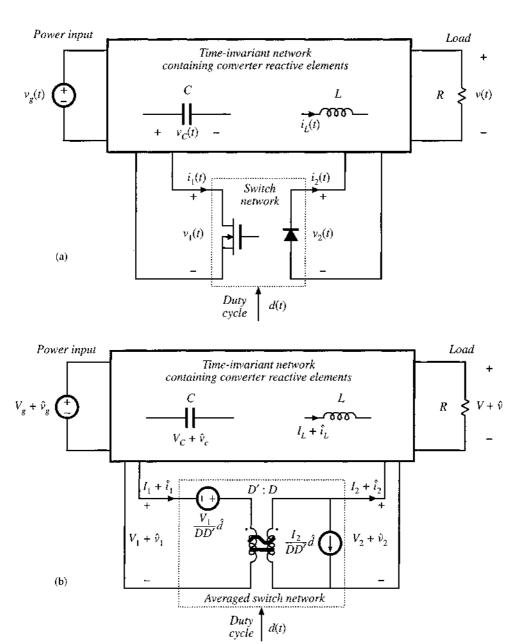

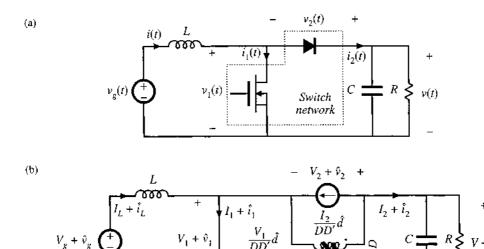

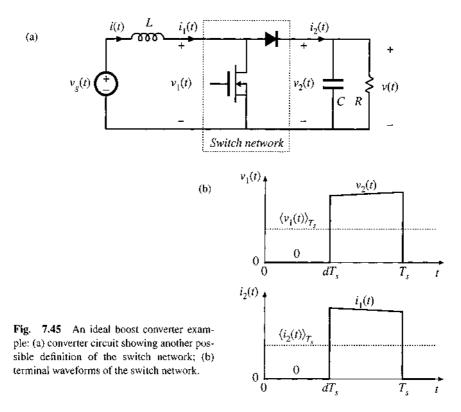

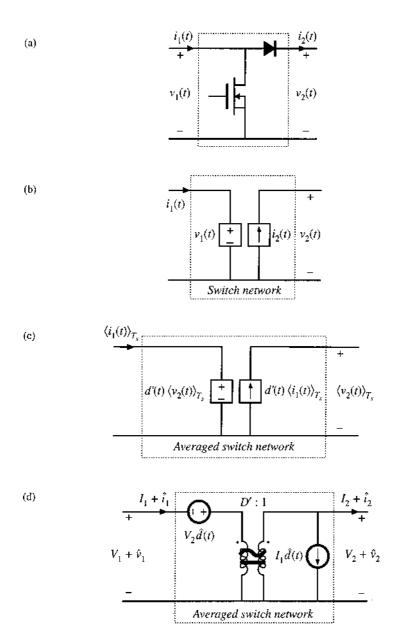

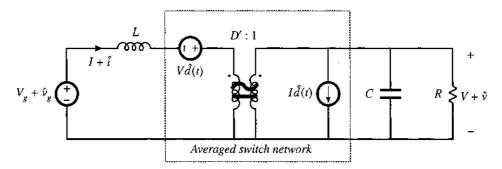

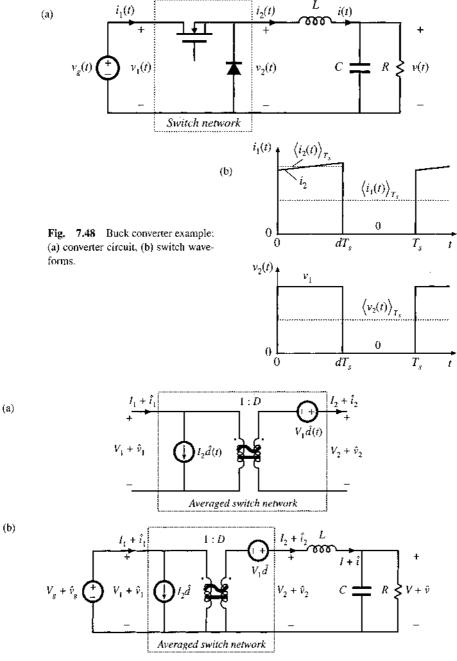

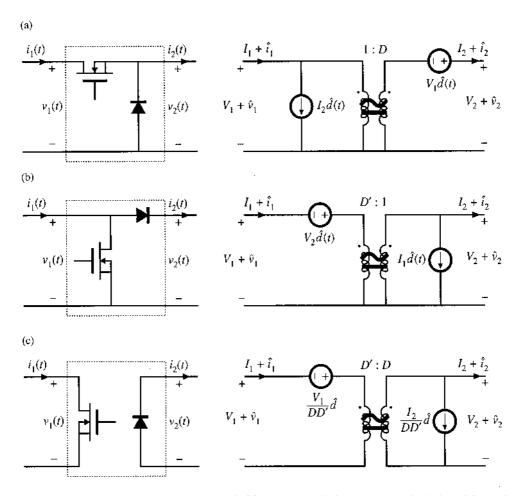

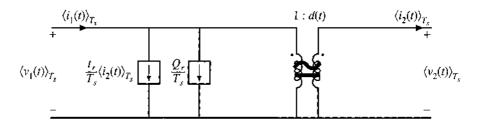

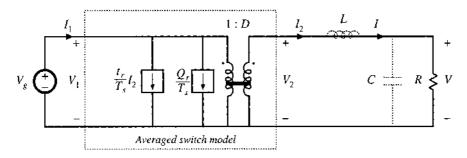

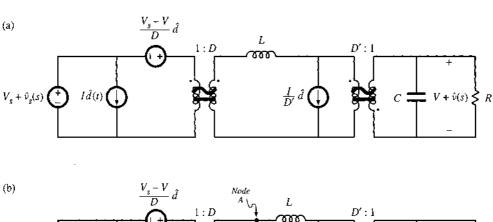

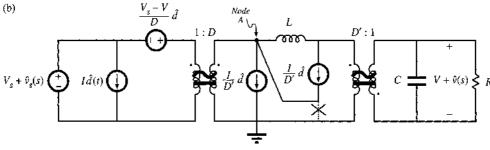

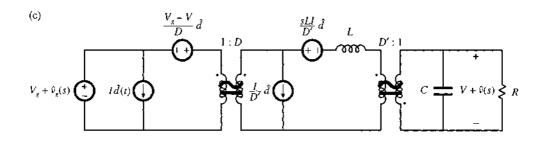

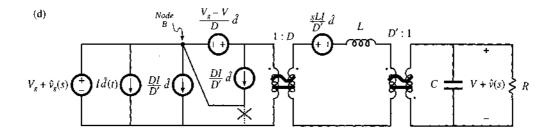

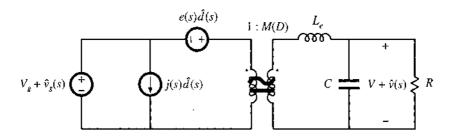

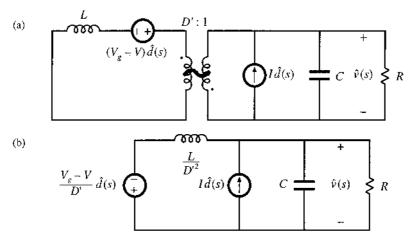

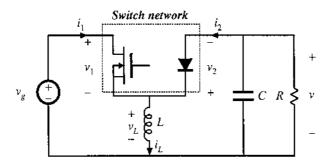

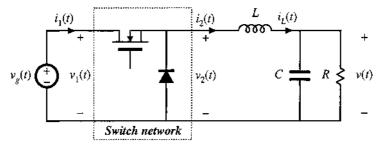

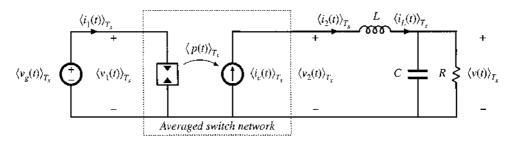

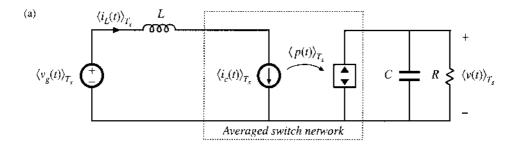

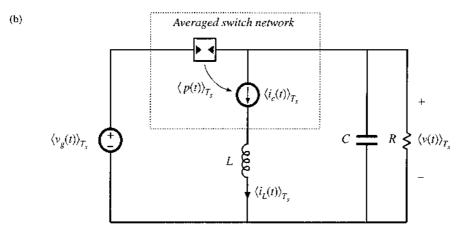

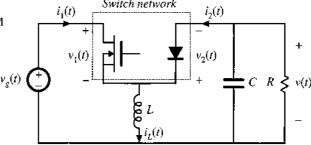

|    | 7.4  | Circuit        | Averaging and Averaged Switch Modeling                                      | 226        |

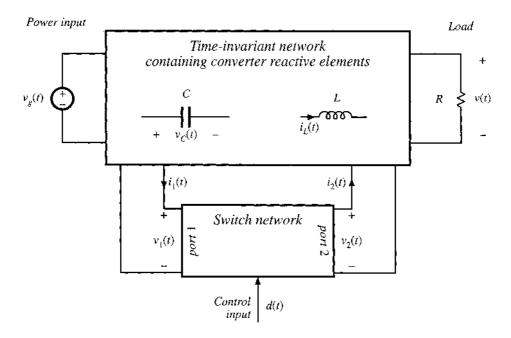

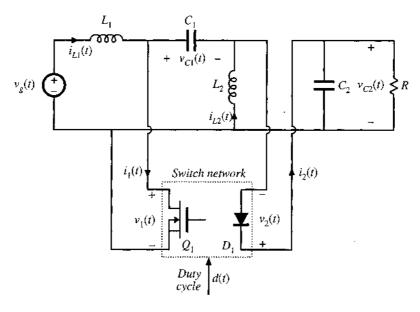

|    |      | 7.4.1          | Obtaining a Time-Invariant Circuit                                          | 228        |

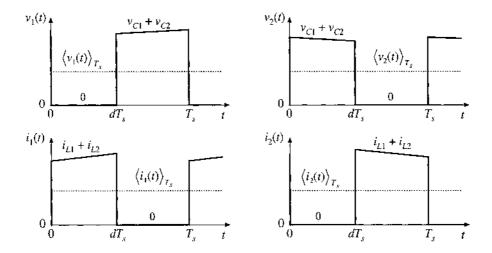

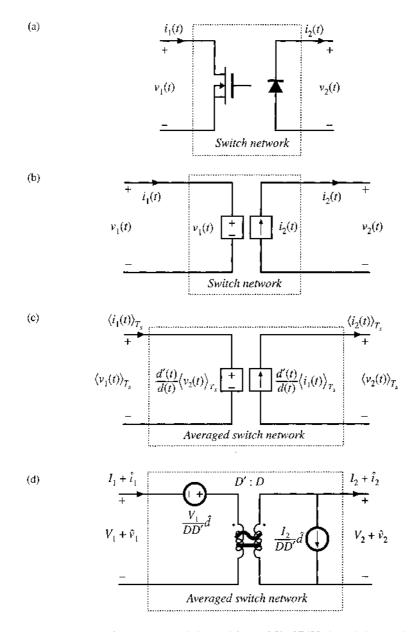

|    |      | 7.4.2          | Circuit Averaging                                                           | 229        |

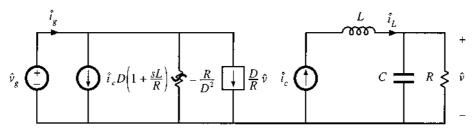

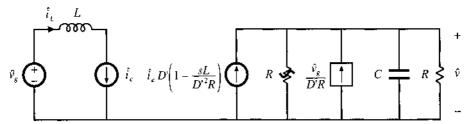

|    |      | 7.4.3          | Perturbation and Linearization                                              | 232        |

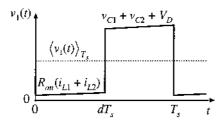

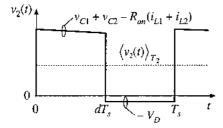

|    |      | 7.4.4          | Switch Networks                                                             | 235        |

|    |      | 7.4.5          | Example: Averaged Switch Modeling of Conduction Losses                      | 242        |

|    |      | 7.4.6          | Example: Averaged Switch Modeling of Switching Losses                       | 244        |

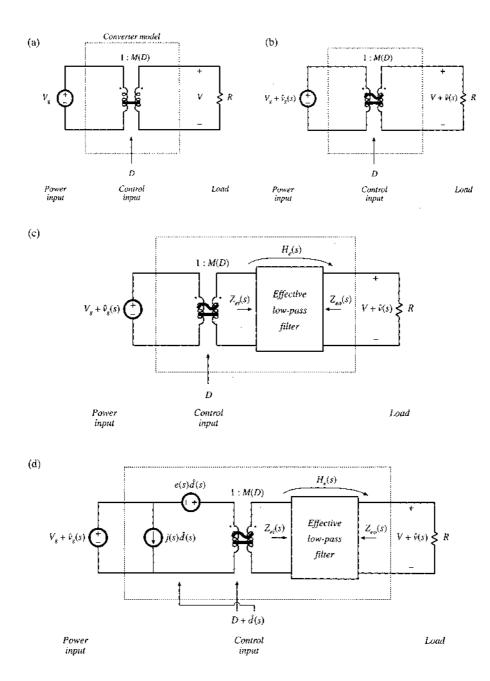

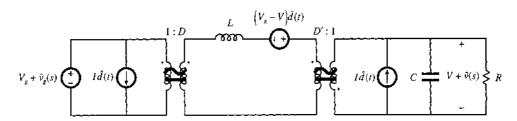

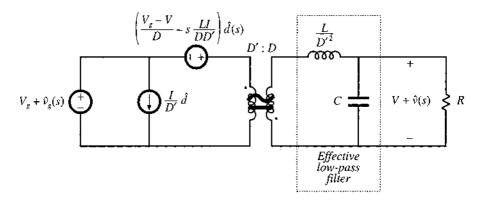

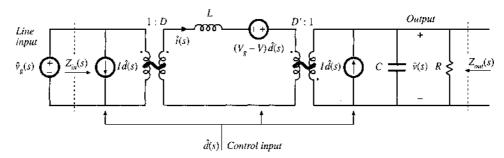

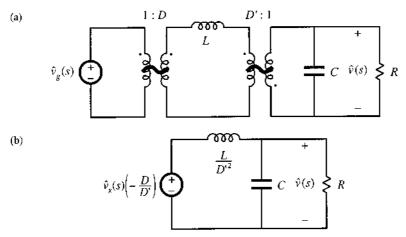

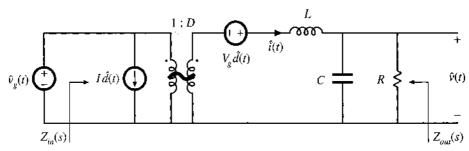

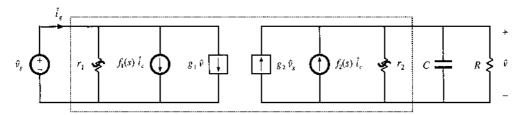

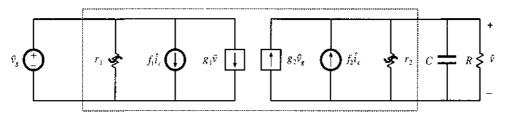

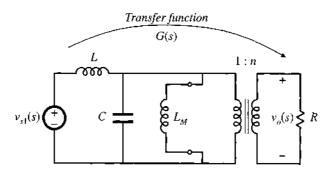

|    | 7.5  |                | anonical Circuit Model                                                      | 247        |

|    |      | 7.5.1          | Development of the Canonical Circuit Model                                  | 248        |

|   |      | 7.5.2                                                                | Example: Manipulation of the Buck-Boost Converter Model           |     |

|---|------|----------------------------------------------------------------------|-------------------------------------------------------------------|-----|

|   |      |                                                                      | into Canonical Form                                               | 250 |

|   |      | 7.5.3                                                                | Canonical Circuit Parameter Values for Some Common Converters     | 252 |

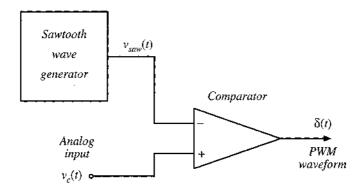

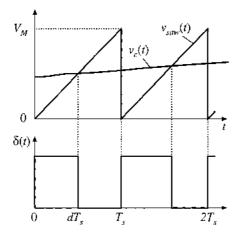

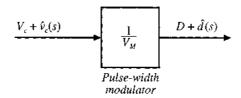

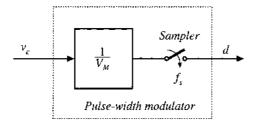

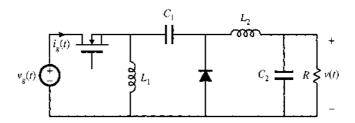

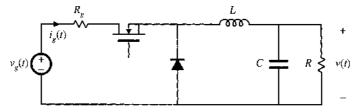

|   | 7.6  | Model                                                                | ing the Pulse-Width Modulator                                     | 253 |

|   | 7.7  | Summ                                                                 | ary of Key Points                                                 | 256 |

|   | Refe | rences                                                               |                                                                   | 257 |

|   | Prob | lems                                                                 |                                                                   | 258 |

| 8 | Conv | erter Tr                                                             | ansfer Functions                                                  | 265 |

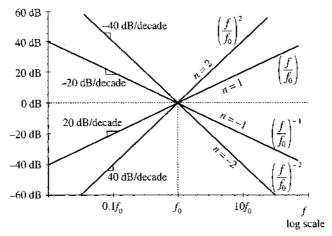

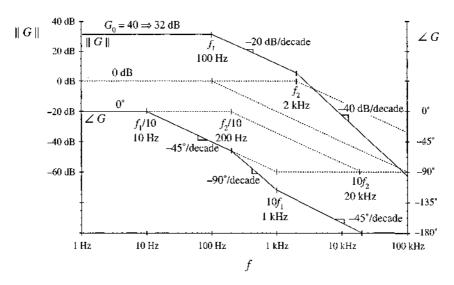

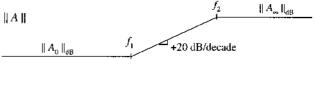

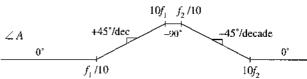

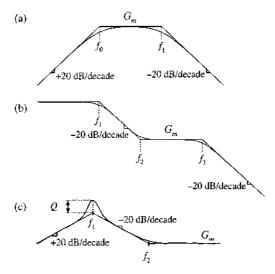

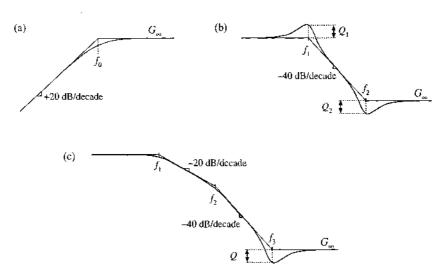

|   | 8.1  | Review                                                               | v of Bode Plots                                                   | 267 |

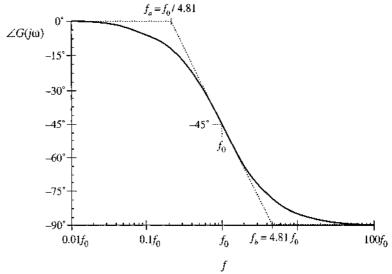

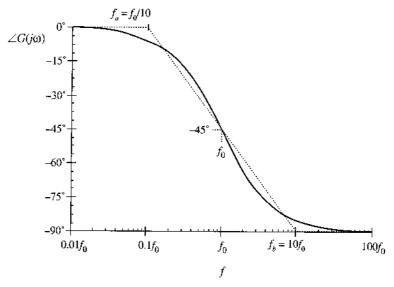

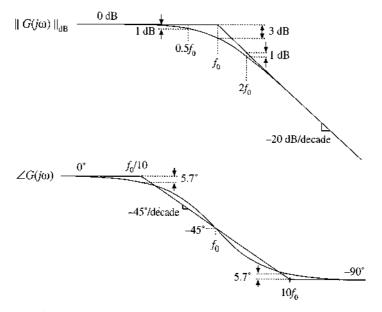

|   |      | 8.1.1                                                                | Single Pole Response                                              | 269 |

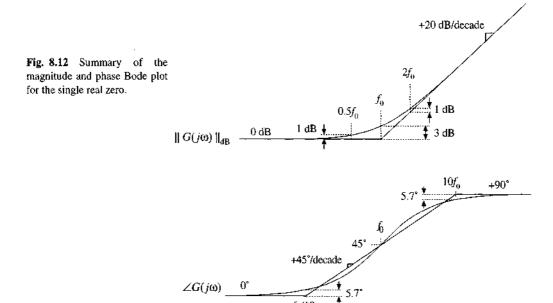

|   |      | 8.1.2                                                                | Single Zero Response                                              | 275 |

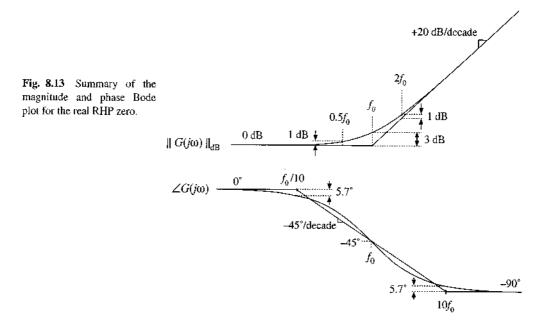

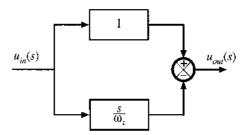

|   |      | 8.1.3                                                                | Right Half-Plane Zero                                             | 276 |

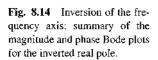

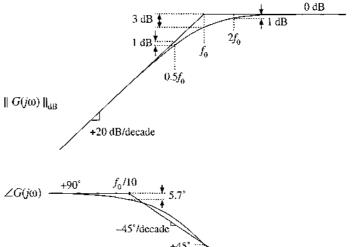

|   |      | 8.1.4                                                                | Frequency Inversion                                               | 277 |

|   |      | 8.1.5                                                                | Combinations                                                      | 278 |

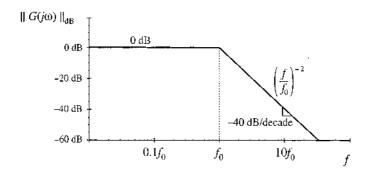

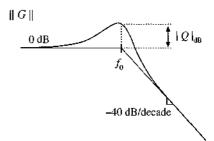

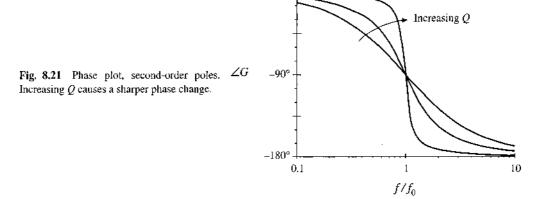

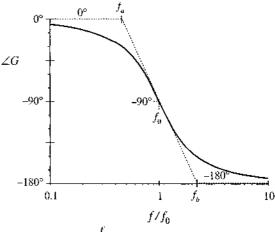

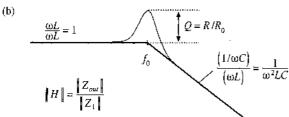

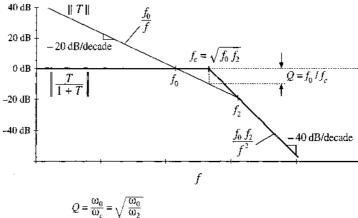

|   |      | 8.1.6                                                                | Quadratic Pole Response: Resonance                                | 282 |

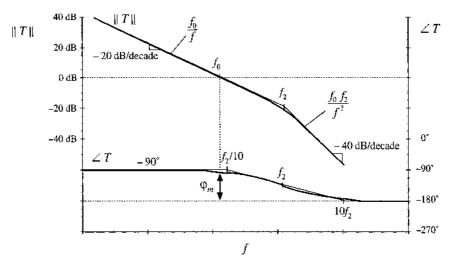

|   |      | 8.1.7                                                                | The Low-Q Approximation                                           | 287 |

|   |      | 8.1.8                                                                | Approximate Roots of an Arbitrary-Degree Polynomial               | 289 |

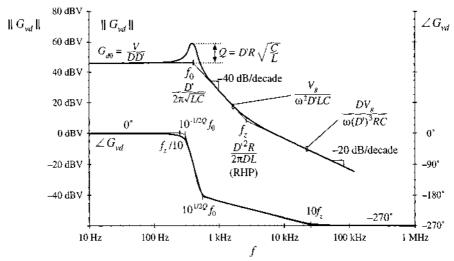

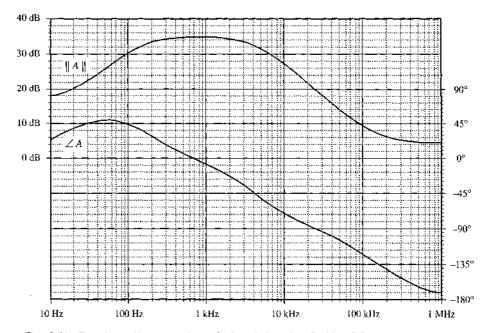

|   | 8.2  | Analys                                                               | sis of Converter Transfer Functions                               | 293 |

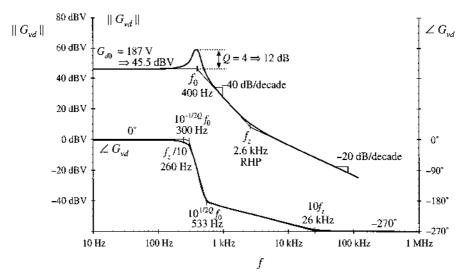

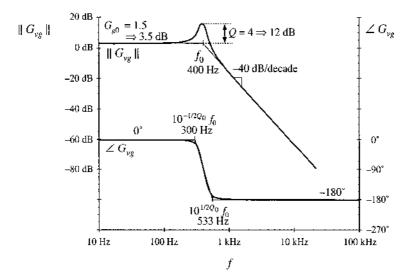

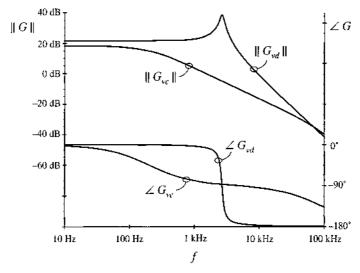

|   |      | 8.2.1                                                                | Example: Transfer Functions of the Buck-Boost Converter           | 294 |

|   |      | 8.2.2                                                                | Transfer Functions of Some Basic CCM Converters                   | 300 |

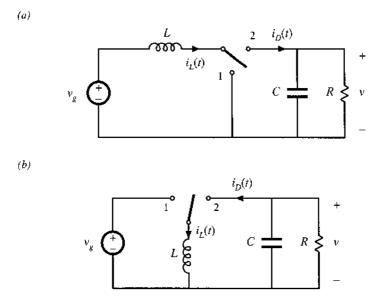

|   |      | 8.2.3                                                                | Physical Origins of the RHP Zero in Converters                    | 300 |

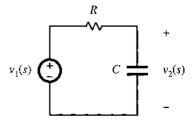

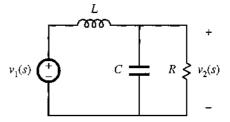

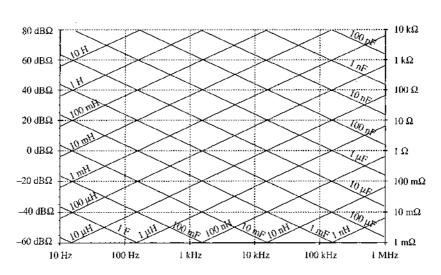

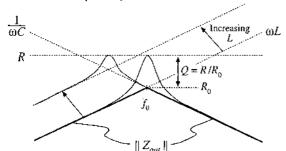

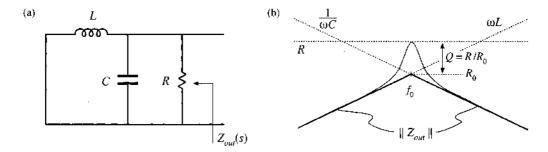

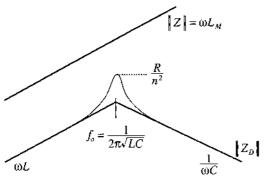

|   | 8.3  | Graphi                                                               | ical Construction of Impedances and Transfer Functions            | 302 |

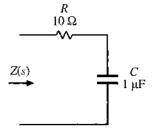

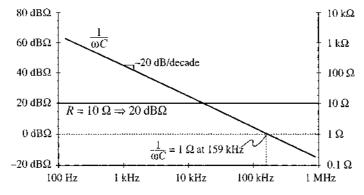

|   |      | 8.3.1                                                                | Series Impedances: Addition of Asymptotes                         | 303 |

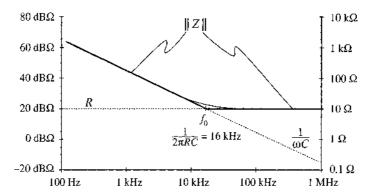

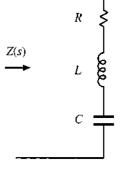

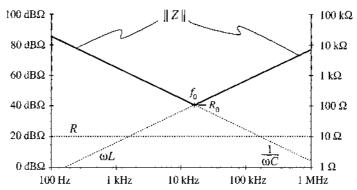

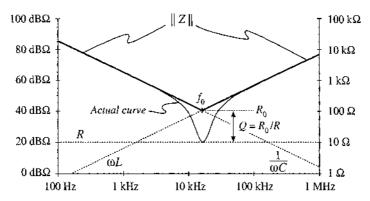

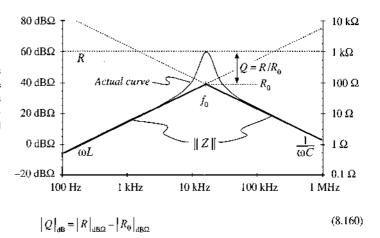

|   |      | 8.3.2                                                                | Series Resonant Circuit Example                                   | 305 |

|   |      | 8.3.3                                                                | Parallel Impedances: Inverse Addition of Asymptotes               | 308 |

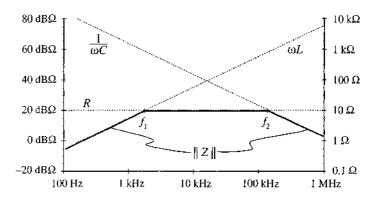

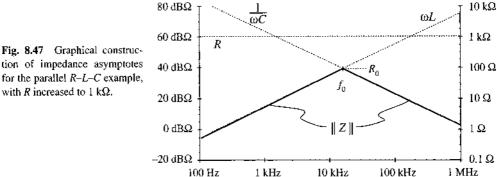

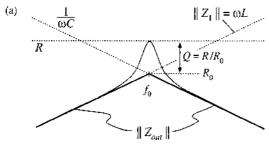

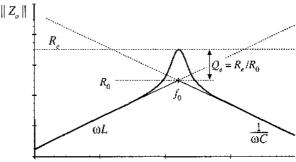

|   |      | 8.3.4                                                                | Parallel Resonant Circuit Example                                 | 309 |

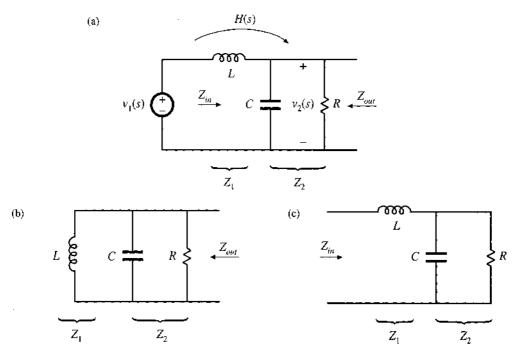

|   |      | 8.3.5                                                                | Voltage Divider Transfer Functions: Division of Asymptotes        | 311 |

|   | 8.4  | •                                                                    | cal Construction of Converter Transfer Functions                  | 313 |

|   | 8.5  | Measu                                                                | rement of AC Transfer Functions and Impedances                    | 317 |

|   | 8.6  | Summa                                                                | ary of Key Points                                                 | 321 |

|   | Refe | rences                                                               |                                                                   | 322 |

|   | Prob | lems                                                                 |                                                                   | 322 |

| 9 | Cont | roller De                                                            | esign                                                             | 331 |

|   | 9.1  | Introdu                                                              | action                                                            | 331 |

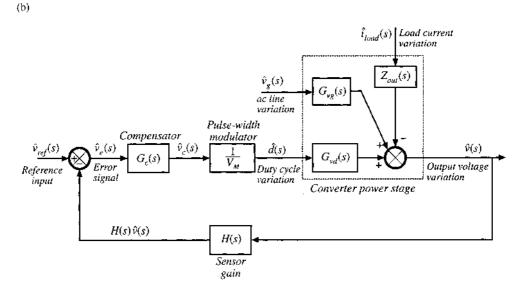

|   | 9.2  | Effect                                                               | of Negative Feedback on the Network Transfer Functions            | 334 |

|   |      |                                                                      | Feedback Reduces the Transfer Functions                           |     |

|   |      |                                                                      | from Disturbances to the Output                                   | 335 |

|   |      | 9.2.2                                                                | Feedback Causes the Transfer Function from the Reference Input    |     |

|   |      |                                                                      | to the Output to be Insensitive to Variations in the Gains in the |     |

|   |      |                                                                      | Forward Path of the Loop                                          | 337 |

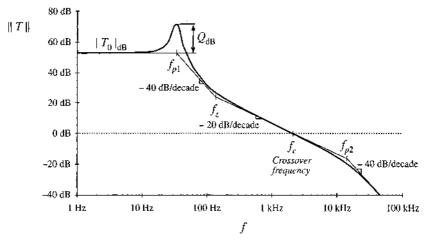

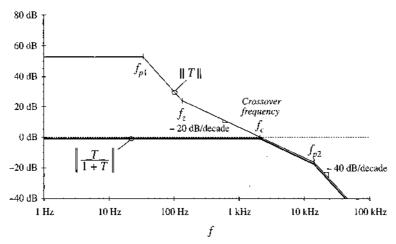

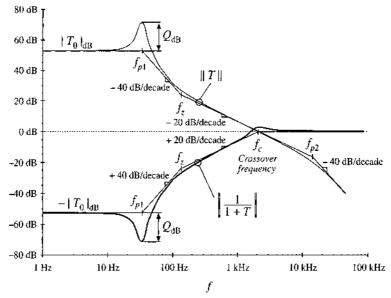

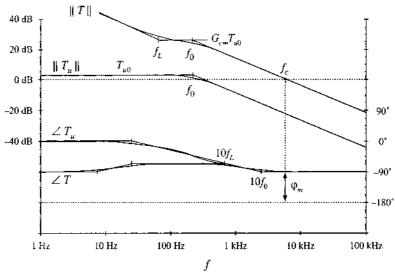

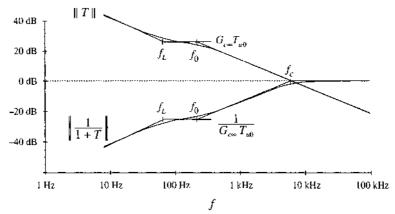

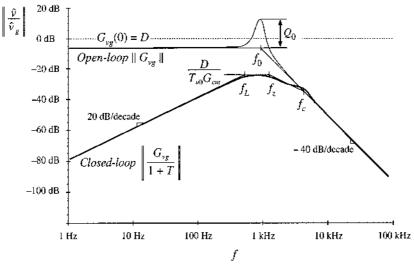

|   | 9.3  | 9.3 Construction of the Important Quantities $1/(1+T)$ and $T/(1+T)$ |                                                                   |     |

|   |      | and the                                                              | e Closed-Loop Transfer Functions                                  | 337 |

|   | 9.4  | Stabilit                                                             | ty                                                                | 340 |

| Contents | xí |

|----------|----|

|          |    |

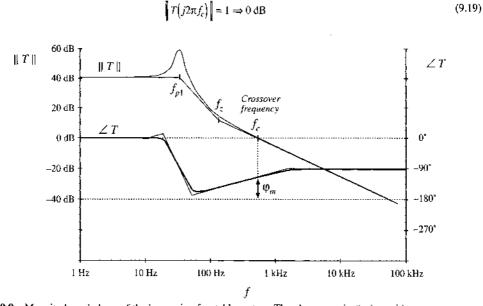

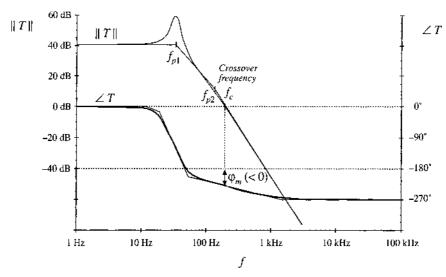

|    |      | 9.4.1             | The Phase Margin Test                                           | 341 |

|----|------|-------------------|-----------------------------------------------------------------|-----|

|    |      | 9.4.2             | The Relationship Between Phase Margin                           |     |

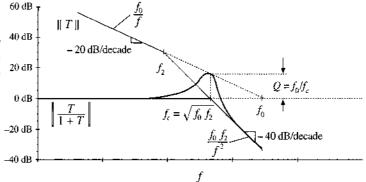

|    |      |                   | and Closed-Loop Damping Factor                                  | 342 |

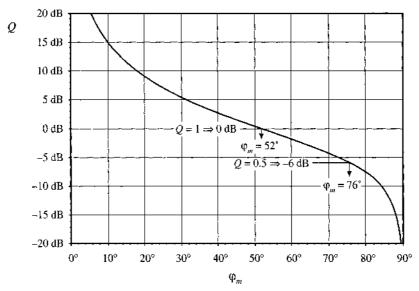

|    |      | 9.4.3             | Transient Response vs. Damping Factor                           | 346 |

|    | 9.5  | Regula            | tor Design                                                      | 347 |

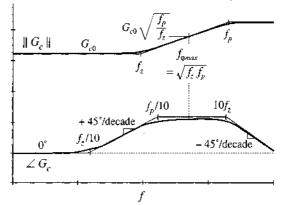

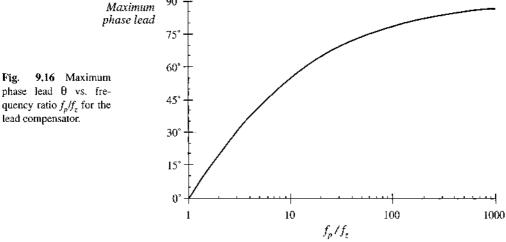

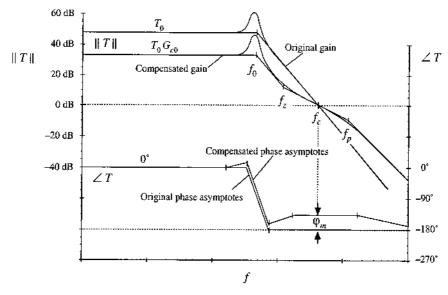

|    |      | 9.5.1             | Lead (PD) Compensator                                           | 348 |

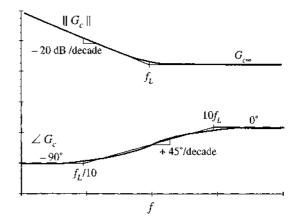

|    |      | 9.5.2             | Lag (PI) Compensator                                            | 351 |

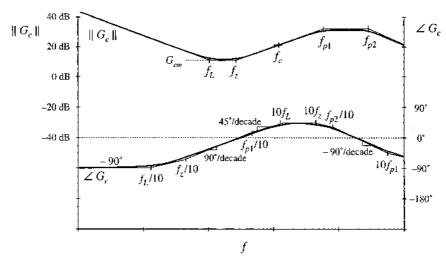

|    |      | 9.5.3             | Combined (PID) Compensator                                      | 353 |

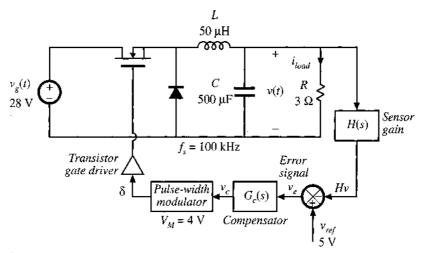

|    |      | 9.5.4             | Design Example                                                  | 354 |

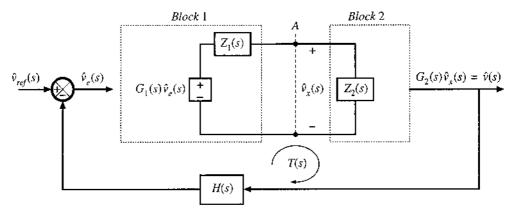

|    | 9.6  | Measur            | rement of Loop Gains                                            | 362 |

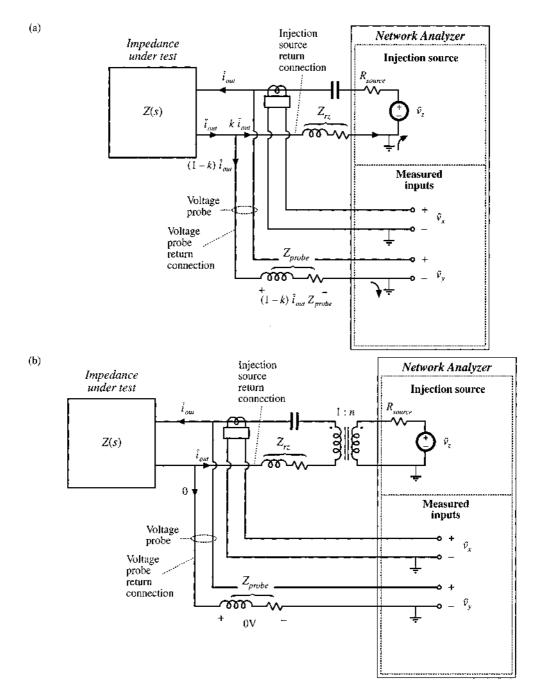

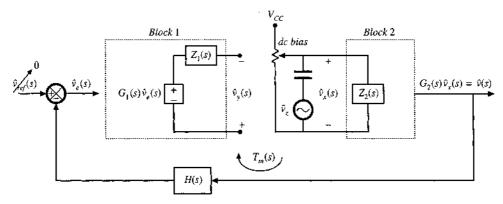

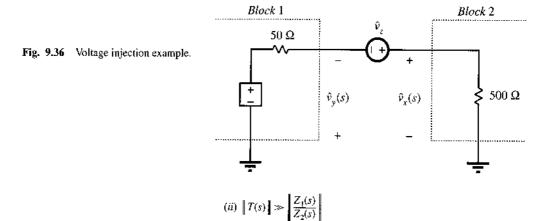

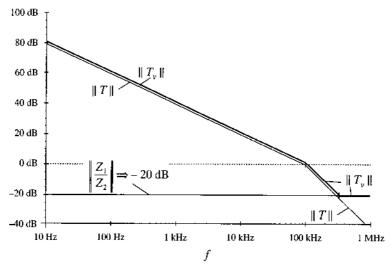

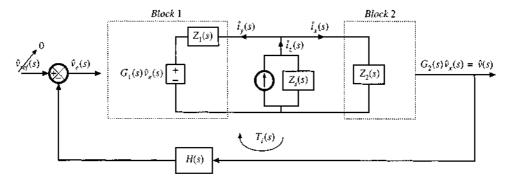

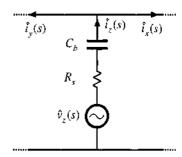

|    |      | 9.6.1             | Voltage Injection                                               | 364 |

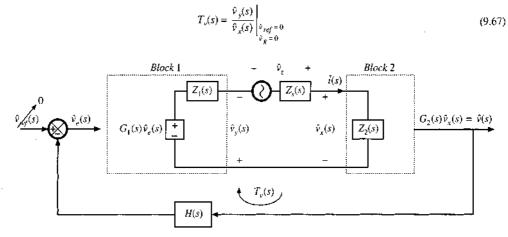

|    |      | 9.6.2             | Current Injection                                               | 367 |

|    |      | 9.6.3             | Measurement of Unstable Systems                                 | 368 |

|    | 9.7  | Summa             | ary of Key Points                                               | 369 |

|    | Refe | rences            |                                                                 | 369 |

|    | Prob | lems              |                                                                 | 369 |

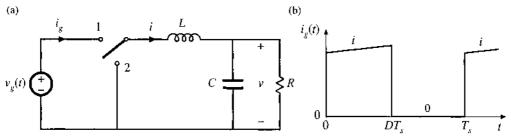

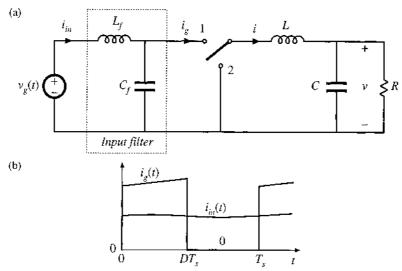

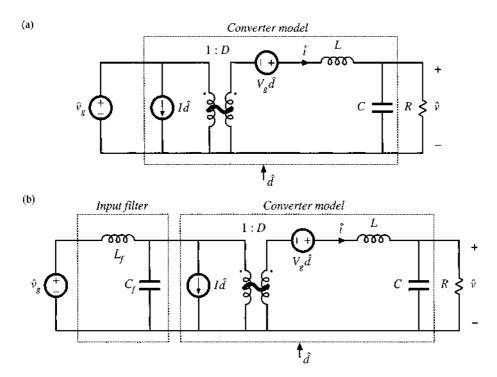

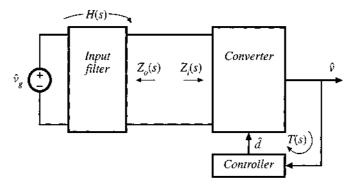

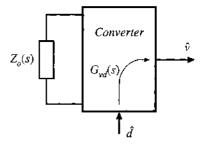

| 10 | Inpu | t Filter <b>D</b> | Design                                                          | 377 |

|    | 10.1 | Introdu           | ction                                                           | 377 |

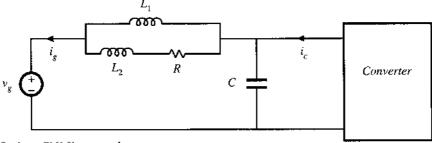

|    |      | 10.1.1            | Conducted EMI                                                   | 377 |

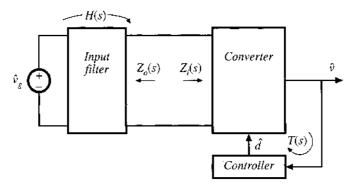

|    |      | 10.1.2            | The Input Filter Design Problem                                 | 379 |

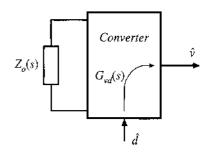

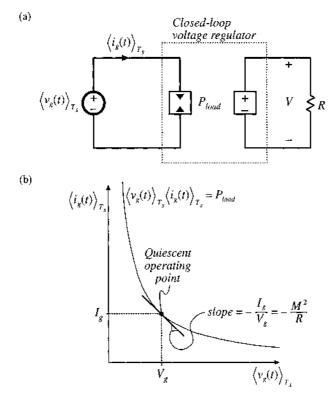

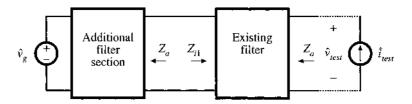

|    | 10.2 | Effect of         | of an Input Filter on Converter Transfer Functions              | 381 |

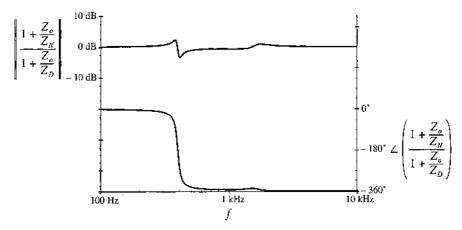

|    |      | 10.2.1            | Discussion                                                      | 382 |

|    |      | 10.2.2            | Impedance Inequalities                                          | 384 |

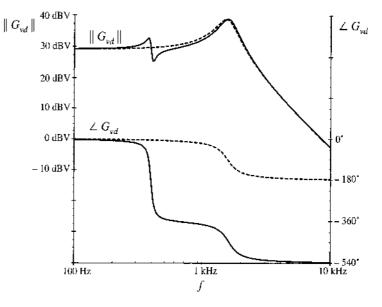

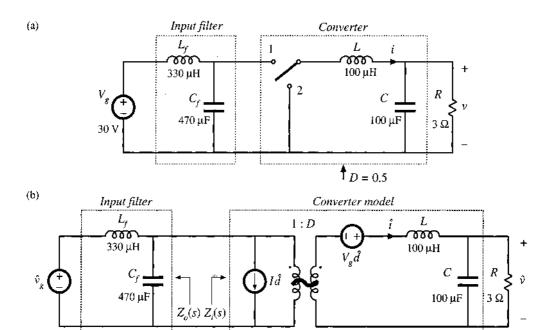

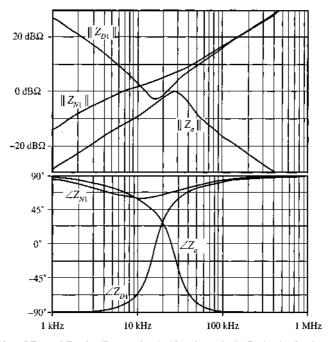

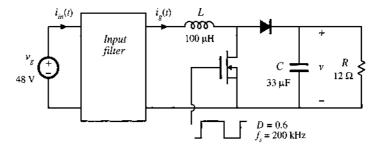

|    | 10.3 | Buck C            | Converter Example                                               | 385 |

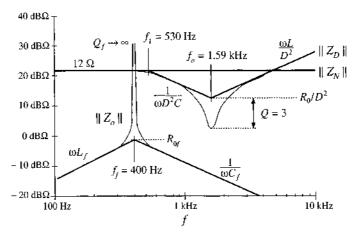

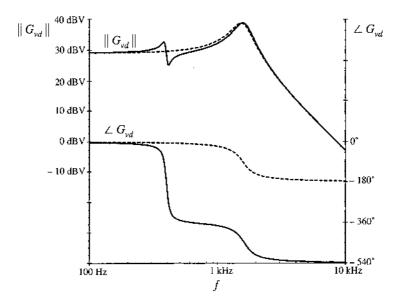

|    |      | 10.3.1            | Effect of Undamped Input Filter                                 | 385 |

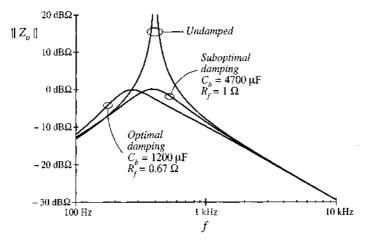

|    |      | 10.3.2            | Damping the Input Filter                                        | 391 |

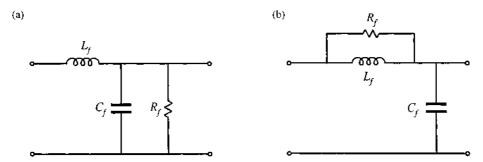

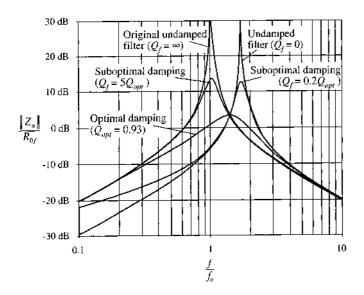

|    | 10.4 | Design            | of a Damped Input Filter                                        | 392 |

|    |      | 10.4.1            | $R_f$ - $C_h$ Parallel Damping                                  | 395 |

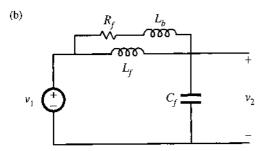

|    |      | 10.4.2            | $R_f$ - $L_b$ Parallel Damping                                  | 396 |

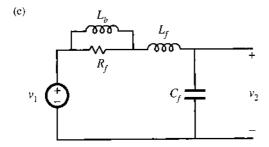

|    |      | 10.4.3            | $R_f$ - $L_b$ Series Damping                                    | 398 |

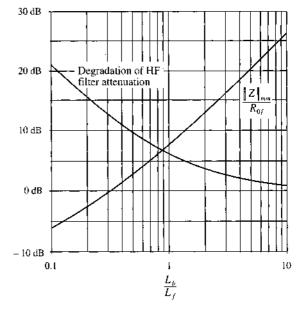

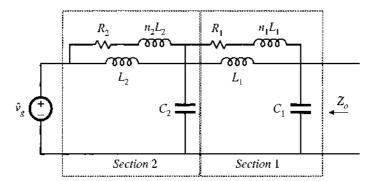

|    |      | 10.4.4            | Cascading Filter Sections                                       | 398 |

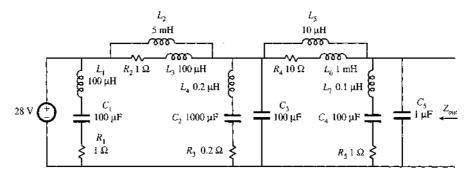

|    |      | 10.4.5            | Example: Two Stage Input Filter                                 | 400 |

|    | 10.5 | Summa             | ary of Key Points                                               | 403 |

|    | Refe | rences            | •                                                               | 405 |

|    | Prob | lems              |                                                                 | 406 |

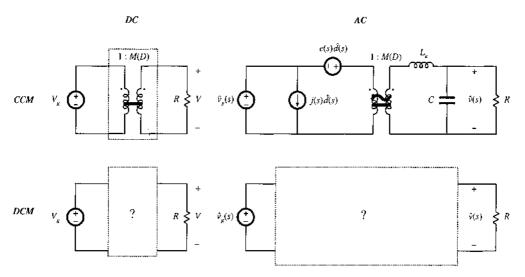

| 11 | AC a | nd DC E           | quivalent Circuit Modeling of the Discontinuous Conduction Mode | 409 |

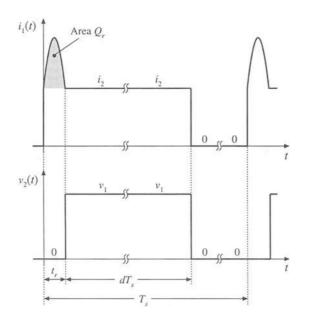

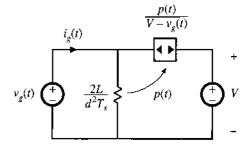

|    | 11.1 | DCM A             | weraged Switch Model                                            | 410 |

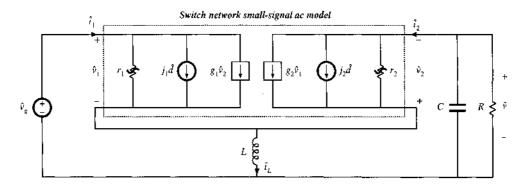

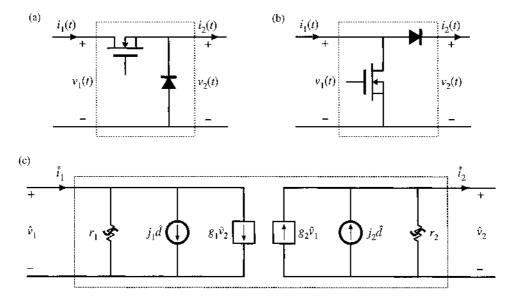

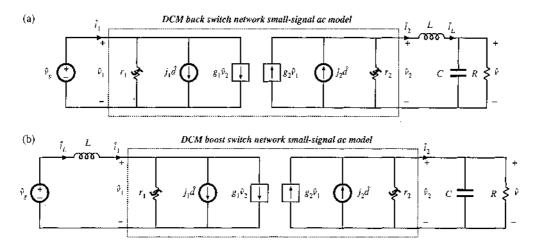

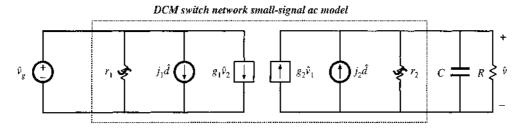

|    | 11.2 | Small-S           | Signal AC Modeling of the DCM Switch Network                    | 420 |

|    |      | 11.2.1            | Example: Control-to-Output Frequency Response                   |     |

|    |      |                   | of a DCM Boost Converter                                        | 428 |

|    |      | 11.2.2            | Example: Control-to-Output Frequency Responses                  |     |

|    |      |                   | of a CCM/DCM SEPIC                                              | 429 |

|    | 11.3  | High-F           | requency Dynamics of Converters in DCM                          | 431        |

|----|-------|------------------|-----------------------------------------------------------------|------------|

|    | 11.4  | Summa            | ry of Key Points                                                | 434        |

|    | Refe  | rences           |                                                                 | 434        |

|    | Prob  | lems             |                                                                 | 435        |

| 12 | Curr  | ent Prog         | rammed Control                                                  | 439        |

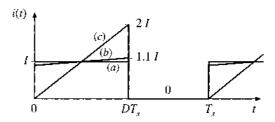

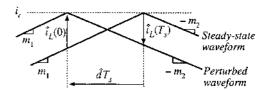

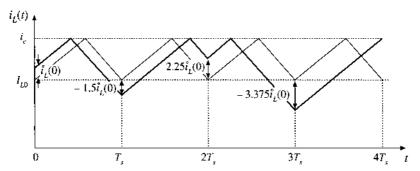

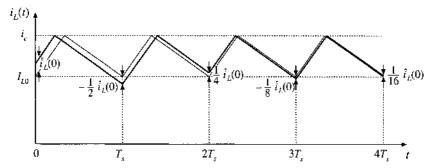

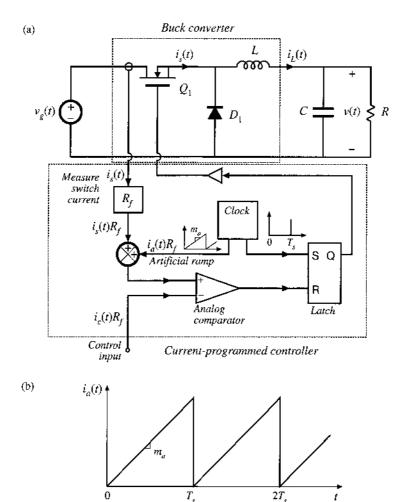

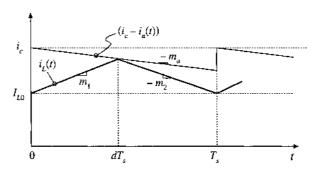

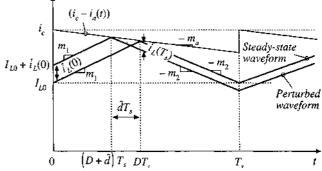

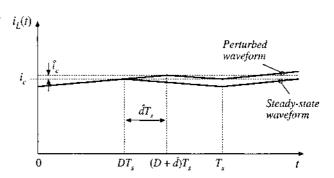

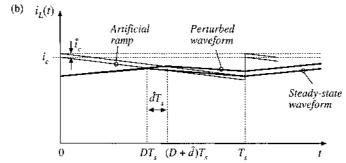

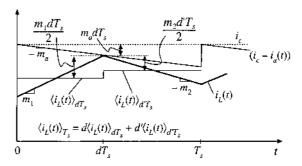

|    | 12.1  | Oscillat         | tion for $D > 0.5$                                              | 441        |

|    | 12.2  | A Simp           | ole First-Order Model                                           | 449        |

|    |       | 12.2.1           | Simple Model via Algebraic Approach: Buck-Boost Example         | 450        |

|    |       | 12.2.2           | Averaged Switch Modeling                                        | 454        |

|    | 12.3  | А Моге           | Accurate Model                                                  | 459        |

|    |       | 12.3.1           | Current-Programmed Controller Model                             | 459        |

|    |       | 12.3.2           | Solution of the CPM Transfer Functions                          | 462        |

|    |       |                  | Discussion                                                      | 465        |

|    |       |                  | Current-Programmed Transfer Functions of the CCM Buck Converter | 466        |

|    |       |                  | Results for Basic Converters                                    | 469        |

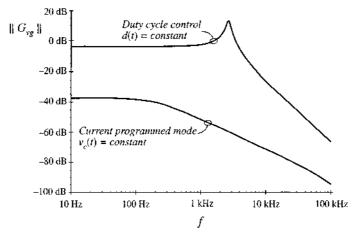

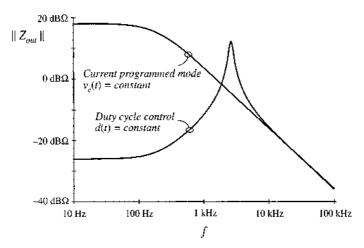

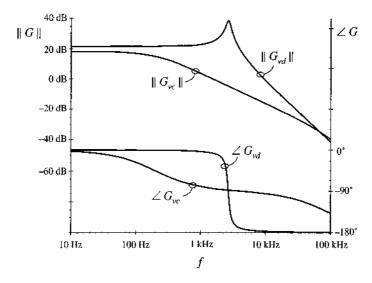

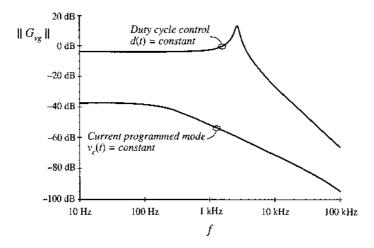

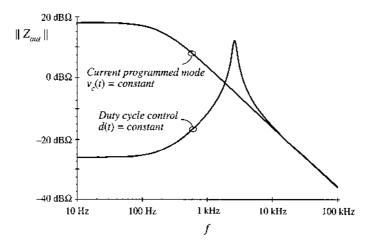

|    |       | 12.3.6           | Quantitative Effects of Current-Programmed Control              | 451        |

|    |       |                  | on the Converter Transfer Functions                             | 471        |

|    | 12.4  |                  | tinuous Conduction Mode                                         | 473        |

|    | 12.5  | Summa            | ry of Key Points                                                | 480        |

|    | Refe  | rences           |                                                                 | 481        |

|    | Probl | lems             |                                                                 | 482        |

| Ш  | Mag   | netics           |                                                                 | 489        |

| 13 | Basic | Magnet           | ics Theory                                                      | 491        |

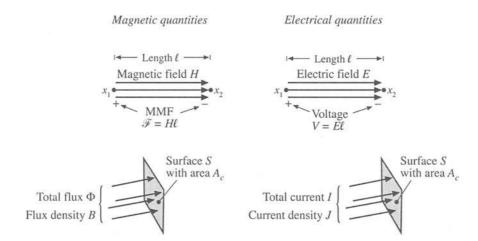

|    | 13.1  | Review           | of Basic Magnetics                                              | 491        |

|    |       | 13.1.1           | Basic Relationships                                             | 491        |

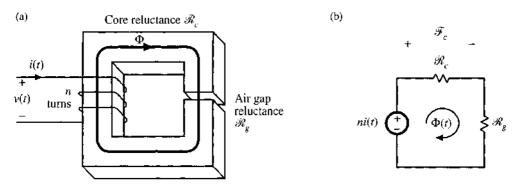

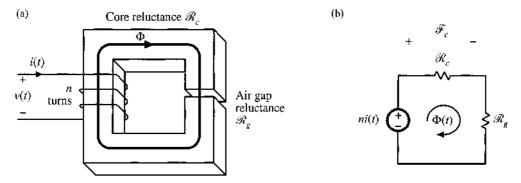

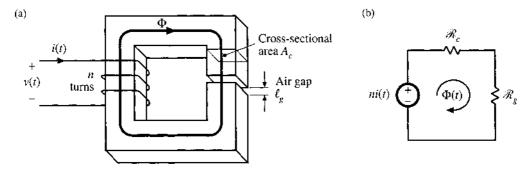

|    |       | 13.1.2           | Magnetic Circuits                                               | 498        |

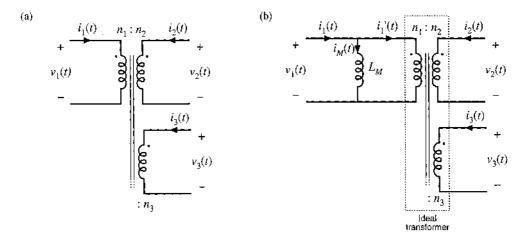

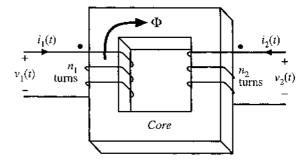

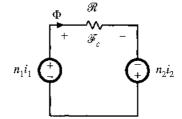

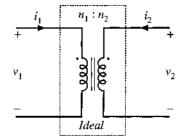

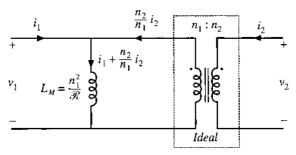

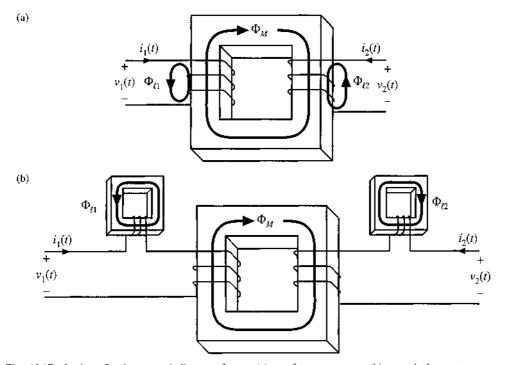

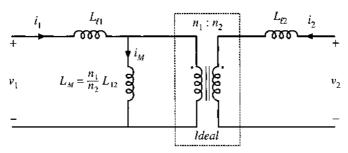

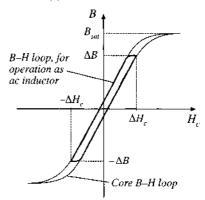

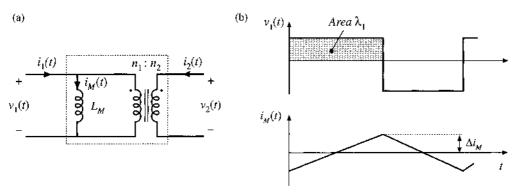

|    | 13.2  | Transfe          | ormer Modeling                                                  | 501        |

|    |       |                  | The Ideal Transformer                                           | 502        |

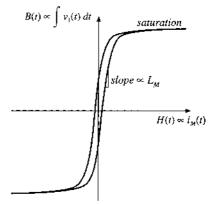

|    |       |                  | The Magnetizing Inductance                                      | 502        |

|    |       |                  | Leakage Inductances                                             | 504        |

|    | 13.3  | Loss M           | echanisms in Magnetic Devices                                   | 506        |

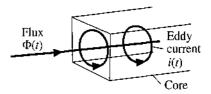

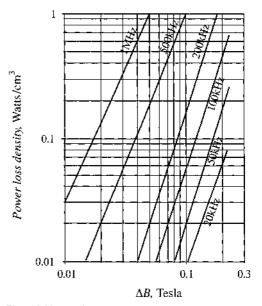

|    |       | 13.3.1           | Core Loss                                                       | 506        |

|    |       | 13.3.2           | Low-Frequency Copper Loss                                       | 508        |

|    | 13.4  | Eddy C           | urrents in Winding Conductors                                   | 508        |

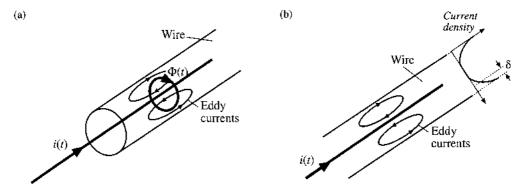

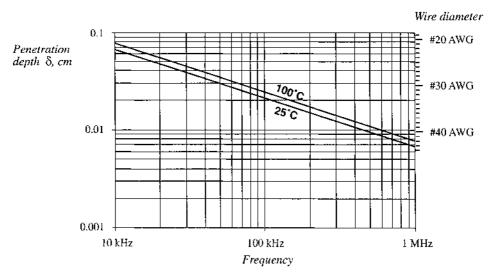

|    |       | 13.4.1           | Introduction to the Skin and Proximity Effects                  | 508        |

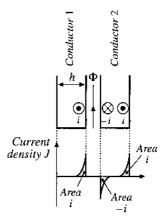

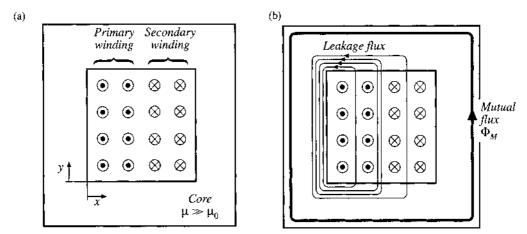

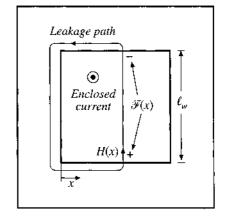

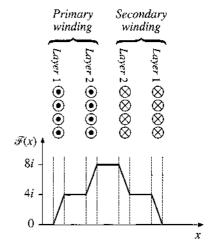

|    |       | 13.4.2           | Leakage Flux in Windings                                        | 512        |

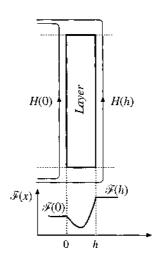

|    |       | 13.4.3           | Foil Windings and Layers                                        | 514        |

|    |       | 13,4,4           | Power Loss in a Layer                                           | 515        |

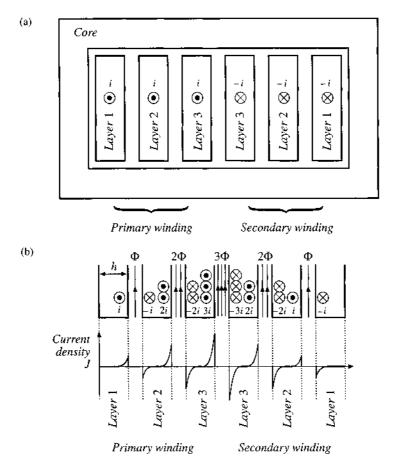

|    |       | 13.4.5<br>13.4.6 | Example: Power Loss in a Transformer Winding                    | 518<br>520 |

|    |       | 13.4.0           | Interleaving the Windings PWM Waveform Harmonics                | 520<br>522 |

|    |       | 1,3,4.7          | 1 44 191 AAVACTOLIII LIGIIHOIRES                                | 344        |

| Contents xiii | Contents | xiii |

|---------------|----------|------|

|---------------|----------|------|

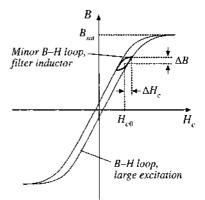

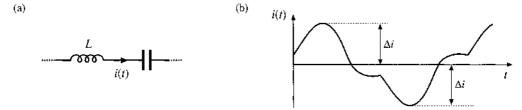

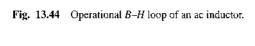

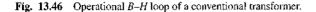

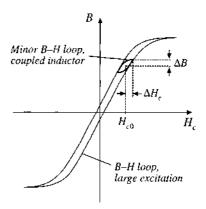

|    | 13.5  |            | Types of Magnetic Devices, Their B-H Loops,           |            |  |

|----|-------|------------|-------------------------------------------------------|------------|--|

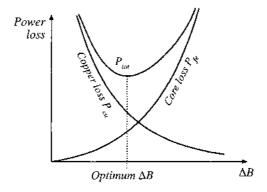

|    |       |            | ore vs. Copper Loss                                   | 525        |  |

|    |       |            | Filter Inductor                                       | 525        |  |

|    |       |            | AC Inductor<br>Transformer                            | 527<br>528 |  |

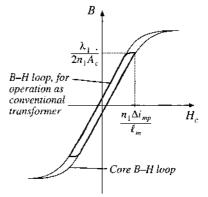

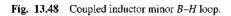

|    |       |            | Coupled Inductor                                      | 526<br>529 |  |

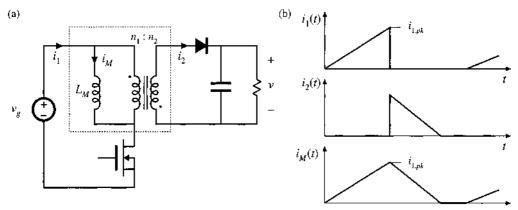

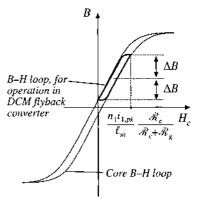

|    |       |            | Flyback Transformer                                   | 530        |  |

|    | 13.6  |            | ary of Key Points                                     | 531        |  |

|    |       | rences     | ary of recy rounds                                    | 532        |  |

|    | Prob  |            |                                                       | 533        |  |

| 14 | Indu  | ctor Desi  | ign                                                   | 539        |  |

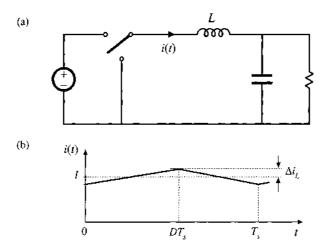

|    | 14.1  | Filter I   | nductor Design Constraints                            | 539        |  |

|    |       | 14.1.1     | Maximum Flux Density                                  | 541        |  |

|    |       |            | Inductance                                            | 542        |  |

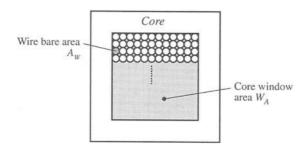

|    |       | 14.1.3     | Winding Area                                          | 542        |  |

|    |       |            | Winding Resistance                                    | 543        |  |

|    |       | 14.1.5     | The Core Geometrical Constant $K_g$                   | 543        |  |

|    | 14.2  | _          | -by-Step Procedure                                    | 544        |  |

|    | 14.3  | Multipl    | le-Winding Magnetics Design via the $K_g$ Method      | 545        |  |

|    |       |            | Window Area Allocation                                | 545        |  |

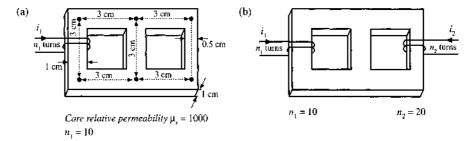

|    |       |            | Coupled Inductor Design Constraints                   | 550        |  |

|    |       |            | Design Procedure                                      | 552        |  |

|    | 14.4  | Examp      |                                                       | 554        |  |

|    |       | 14.4.1     | Coupled Inductor for a Two-Output Forward Converter   | 554        |  |

|    | 14.5  |            | CCM Flyback Transformer                               | 557        |  |

|    | 14.5  |            | ary of Key Points                                     | 562<br>562 |  |

|    |       | References |                                                       |            |  |

|    | Prob! |            |                                                       | 563        |  |

| 15 |       | sformer    | _                                                     | 565        |  |

|    | 15.1  |            | ormer Design: Basic Constraints                       | 565        |  |

|    |       | 15.1.1     |                                                       | 566        |  |

|    |       |            | Flux Density Copper Loss                              | 566        |  |

|    |       | 15.1.4     |                                                       | 567<br>568 |  |

|    |       |            | Optimum Flux Density                                  | 569        |  |

|    | 15.2  |            | -by-Step Transformer Design Procedure                 | 570        |  |

|    | 15.3  | Examp      |                                                       | 573        |  |

|    |       | 15.3.1     |                                                       | 573        |  |

|    |       | 15.3.2     | Example 2: Multiple-Output Full-Bridge Buck Converter | 576        |  |

|    | 15.4  |            | luctor Design                                         | 580        |  |

|    |       | 15.4.1     | Outline of Derivation                                 | 580        |  |

|    |       | 15.4.2     | Step-by-Step AC Inductor Design Procedure             | 582        |  |

|    | 15.5                         | Summary                                      |                                                  | 583         |  |

|----|------------------------------|----------------------------------------------|--------------------------------------------------|-------------|--|

|    | Refe                         | ences                                        |                                                  | 583         |  |

|    | Prob                         | ems                                          |                                                  | 584         |  |

| IV | Mod                          | ern Rectifiers and                           | Power System Harmonics                           | 587         |  |

| 16 | Powe                         | and Harmonics in No                          | onsinusoidal Systems                             | 589         |  |

|    | 16.1                         | Average Power                                |                                                  | 590         |  |

|    | 16.2                         | Root-Mean-Square (R                          | MS) Value of a Waveform                          | 593         |  |

|    | 16.3                         | Power Factor                                 |                                                  | 594         |  |

|    |                              | 16.3.1 Linear Resist                         | ve Load, Nonsinusoidal Voltage                   | <b>59</b> 4 |  |

|    |                              | 16.3.2 Nonlinear Dy                          | namic Load, Sinusoidal Voltage                   | 595         |  |

|    | 16.4                         | Power Phasors in Sinu                        | soidal Systems                                   | 598         |  |

|    | 16.5                         | Harmonic Currents in                         | Three-Phase Systems                              | 599         |  |

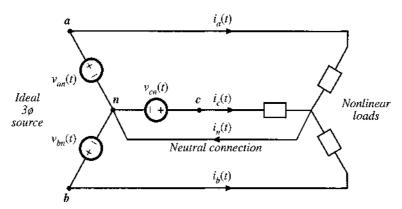

|    |                              | 16.5.1 Harmonic Cu                           | rrents in Three-Phase Four-Wire Networks         | 599         |  |

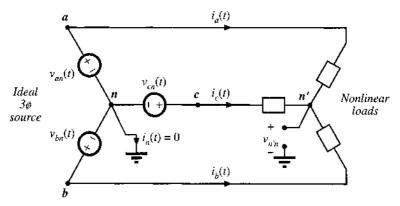

|    |                              | 16.5.2 Harmonic Cu                           | rrents in Three-Phase Three-Wire Networks        | 601         |  |

|    |                              | 16.5.3 Harmonic Cu                           | rrent Flow in Power Factor Correction Capacitors | 602         |  |

|    | 16.6                         | AC Line Current Harn                         | nonic Standards                                  | 603         |  |

|    |                              |                                              | Electrotechnical Commission Standard 1000        | 603         |  |

|    |                              | 16.6.2 IEEE/ANSI S                           | tandard 519                                      | 604         |  |

|    |                              | ography                                      |                                                  | 605         |  |

|    | Prob                         | ems                                          |                                                  | 605         |  |

| 17 | Line-Commutated Rectificrs   |                                              |                                                  |             |  |

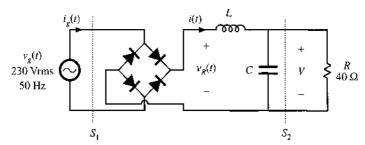

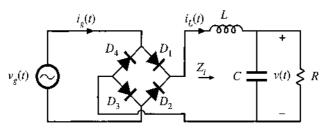

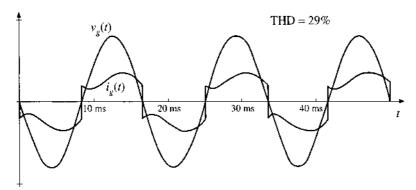

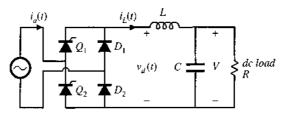

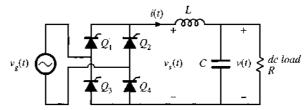

|    | 17.1                         | The Single-Phase Full-                       | Wave Rectifier                                   | 609         |  |

|    |                              |                                              | onduction Mode                                   | 610         |  |

|    |                              |                                              | s Conduction Mode                                | 611         |  |

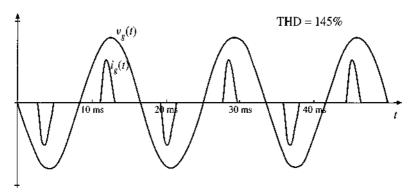

|    |                              | 17.1.3 Behavior who                          |                                                  | 612<br>613  |  |

|    | 17.2                         | =                                            | THD when C is Small                              | 615         |  |

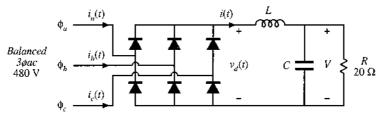

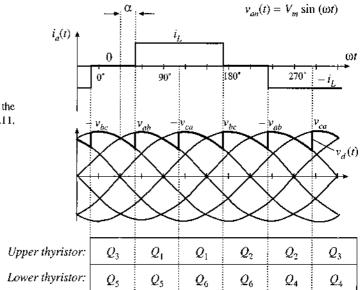

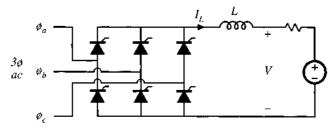

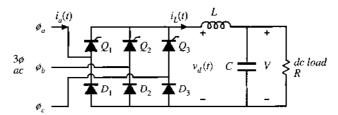

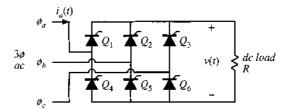

|    | 17.2                         | The Three-Phase Bridg<br>17.2.1 Continuous C | onduction Mode                                   | 615         |  |

|    |                              |                                              | s Conduction Mode                                | 616         |  |

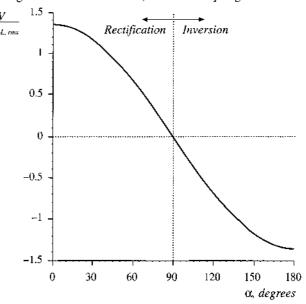

|    | 17.3                         | Phase Control                                |                                                  | 617         |  |

|    |                              | 17.3.1 Inverter Mode                         |                                                  | 619         |  |

|    |                              |                                              | d Power Factor                                   | 619         |  |

|    |                              | 17.3.3 Commutation                           |                                                  | 620         |  |

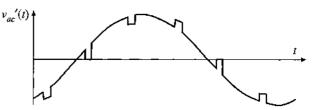

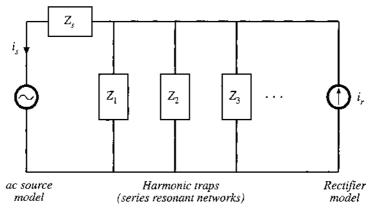

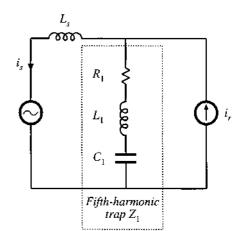

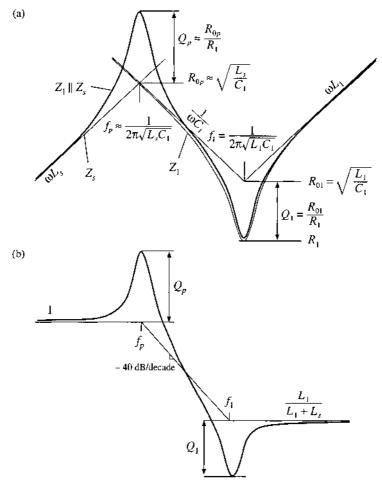

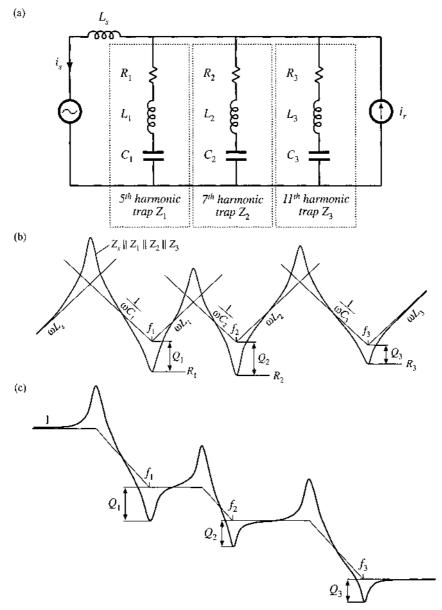

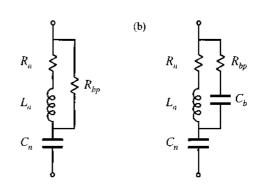

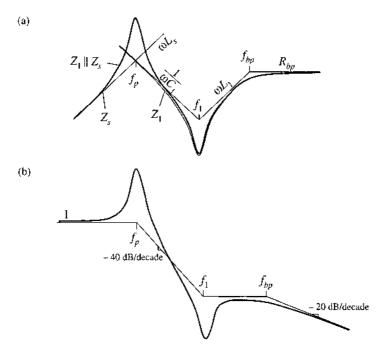

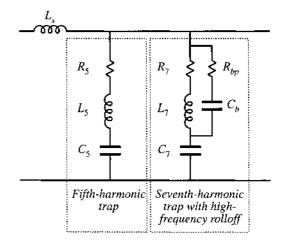

|    | 17.4                         | 17.4 Harmonic Trap Filters                   |                                                  | 622         |  |

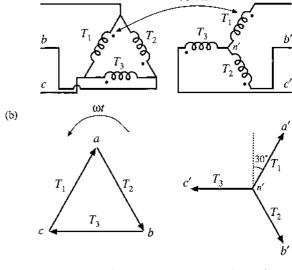

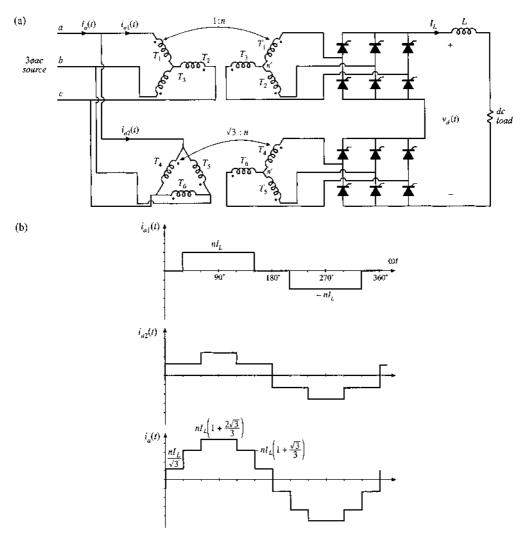

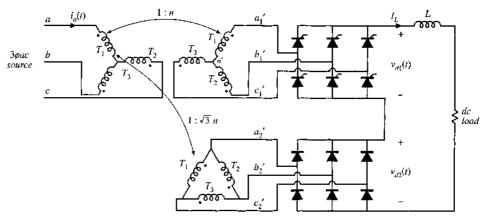

|    | 17.5 Transformer Connections |                                              | 628                                              |             |  |

|    | 17.6                         | Summary                                      |                                                  | 630         |  |

|    | Refe                         | ences                                        |                                                  | 631         |  |

|    | Prob                         | ems                                          |                                                  | 632         |  |

| 18 | Pulse                        | Width Modulated Red                          | tifiers                                          | 637         |  |

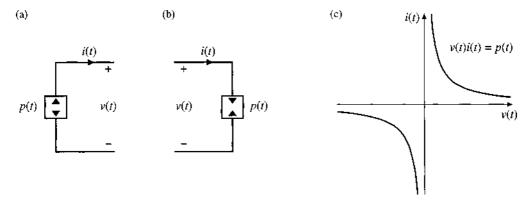

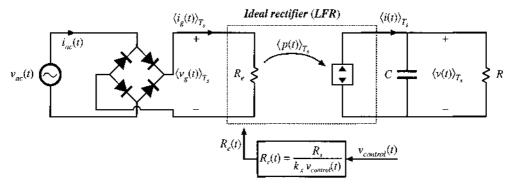

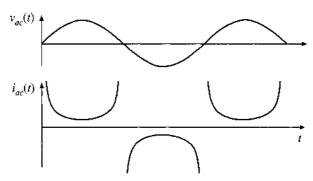

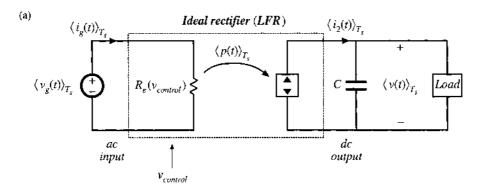

|    | 18.1                         | Properties of the Ideal                      | Rectifier                                        | 638         |  |

| Contents | * 1 |

|----------|-----|

|          |     |

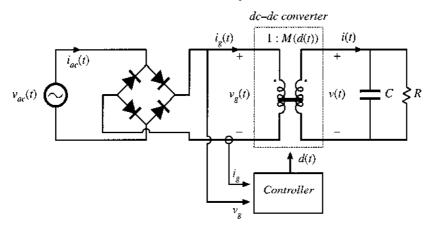

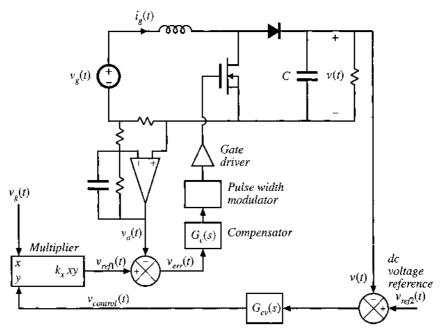

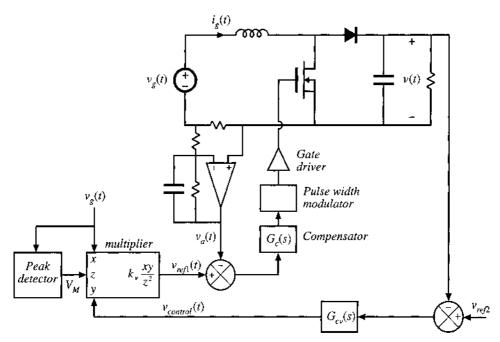

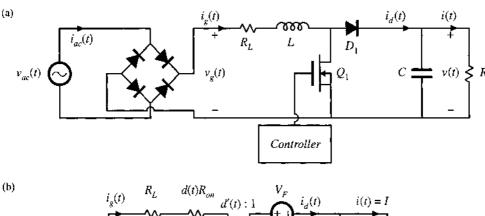

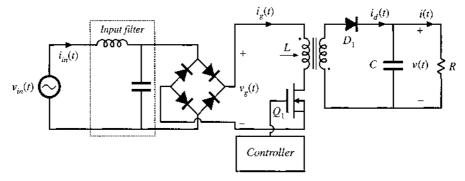

|              | 18.2                | Realiza                                                            | tion of a Near-Ideal Rectifier                                      | 640 |  |

|--------------|---------------------|--------------------------------------------------------------------|---------------------------------------------------------------------|-----|--|

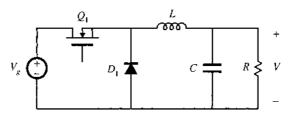

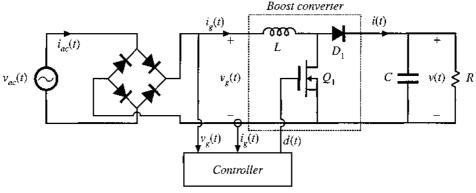

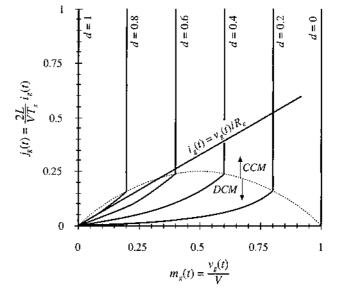

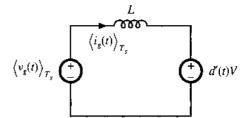

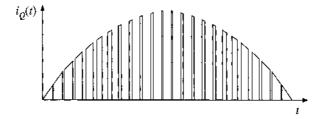

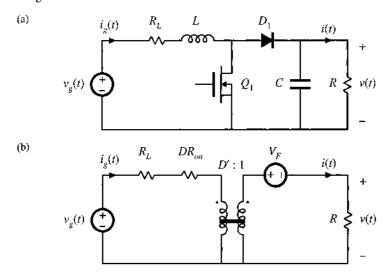

|              |                     | 18.2.1                                                             | CCM Boost Converter                                                 | 642 |  |

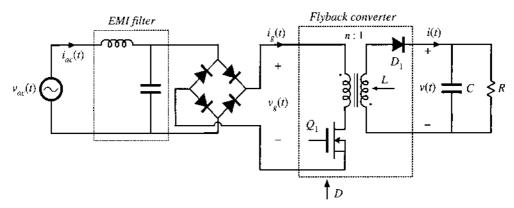

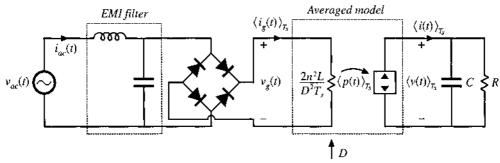

|              |                     | 18.2.2                                                             | DCM Flyback Converter                                               | 646 |  |

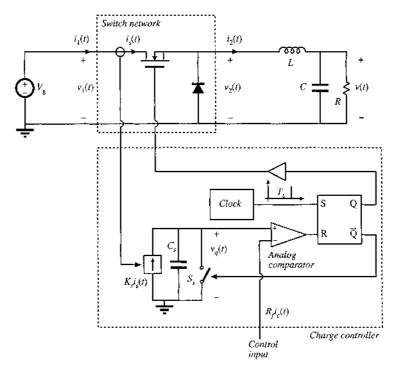

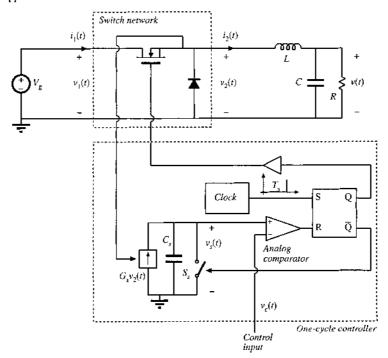

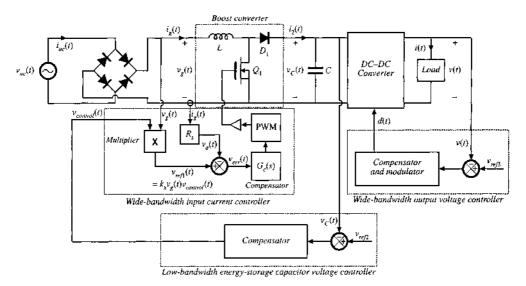

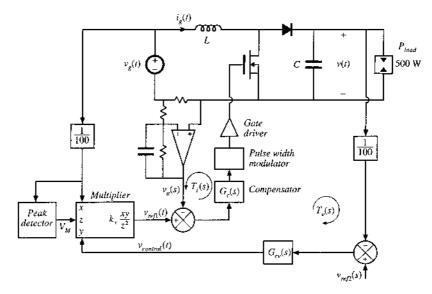

|              | 18.3                | Control                                                            | 648                                                                 |     |  |

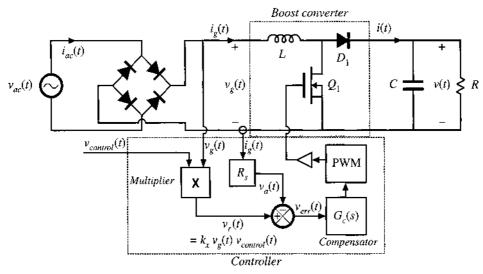

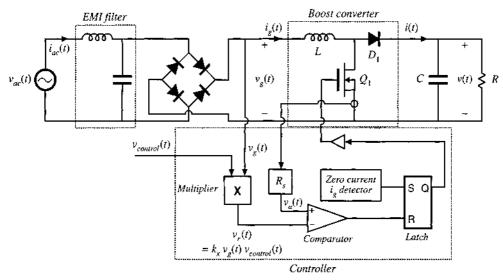

|              |                     | 18.3.1                                                             | Average Current Control                                             | 648 |  |

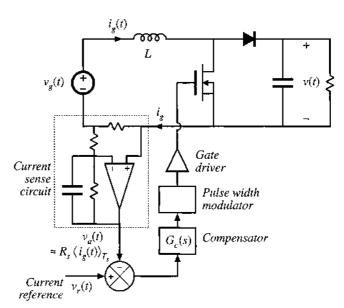

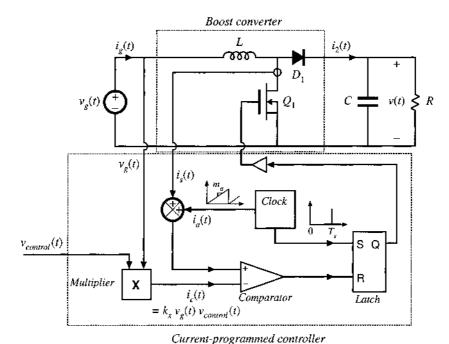

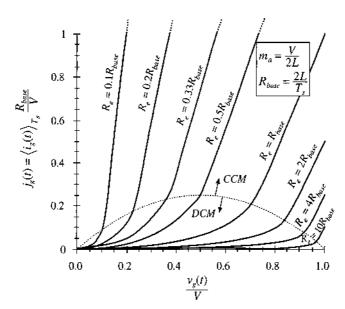

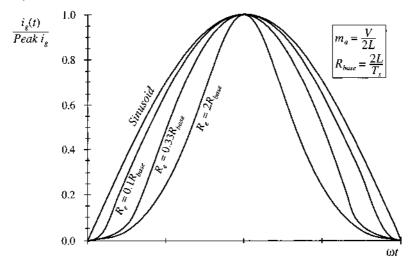

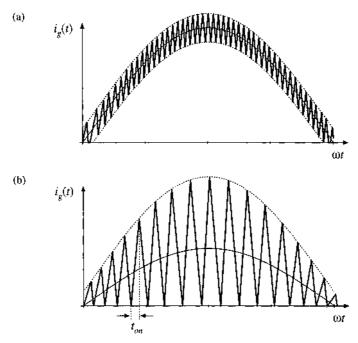

|              |                     | 18.3.2                                                             | Current Programmed Control                                          | 654 |  |

|              |                     | 18.3.3                                                             | •                                                                   | 657 |  |

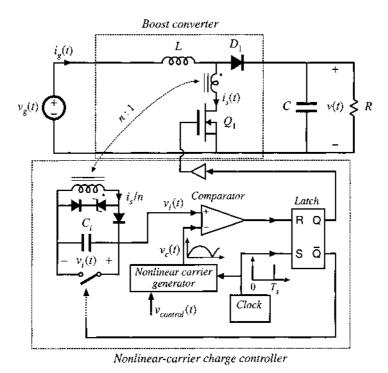

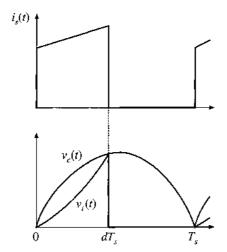

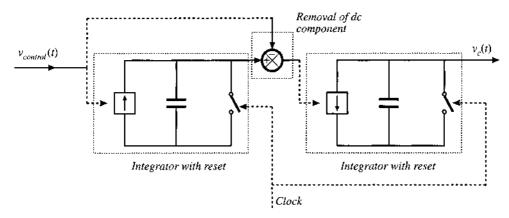

|              |                     | 18.3.4                                                             | Nonlinear Carrier Control                                           | 659 |  |

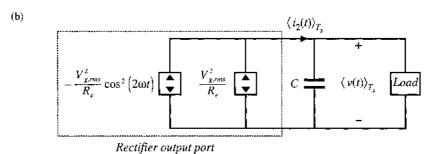

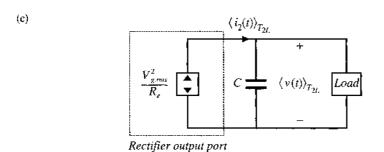

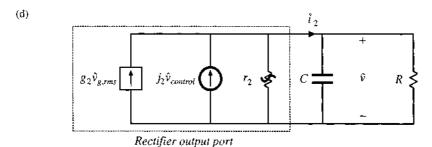

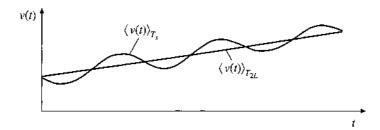

|              | 18.4                | 18.4 Single-Phase Converter Systems Incorporating Ideal Rectifiers |                                                                     |     |  |

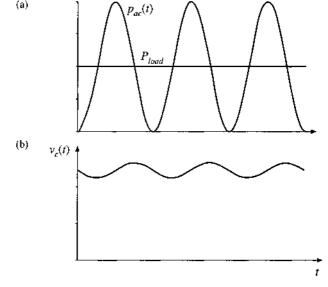

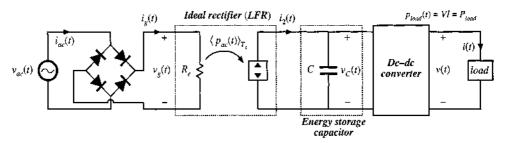

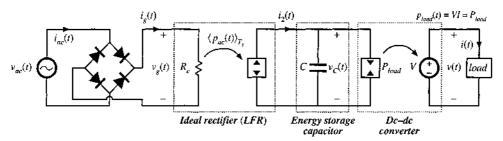

|              |                     | 18.4,1                                                             | 6, 6                                                                | 663 |  |

|              |                     | 18.4.2                                                             | Modeling the Outer Low-Bandwidth Control System                     | 668 |  |

|              | 18.5                | RMS Values of Rectifier Waveforms                                  |                                                                     | 673 |  |

|              |                     | 18.5.1                                                             | Boost Rectifier Example                                             | 674 |  |

|              |                     | 18.5.2                                                             | Comparison of Single-Phase Rectifier Topologies                     | 676 |  |

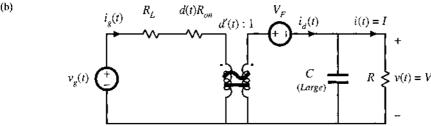

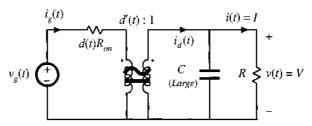

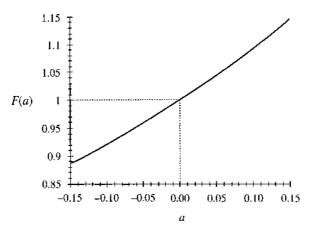

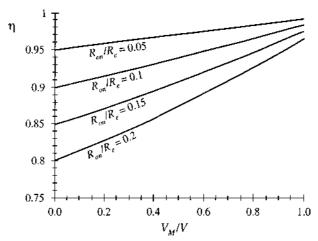

|              | 18.6                | Modeling Losses and Efficiency in CCM High-Quality Rectifiers      |                                                                     | 678 |  |

|              |                     | 18.6.1                                                             | Expression for Controller Duty Cycle $d(t)$                         | 679 |  |

|              |                     | 18.6.2                                                             | Expression for the DC Load Current                                  | 681 |  |

|              |                     | 18.6.3                                                             | · ·                                                                 | 683 |  |

|              |                     | 18.6.4                                                             | Design Example                                                      | 684 |  |

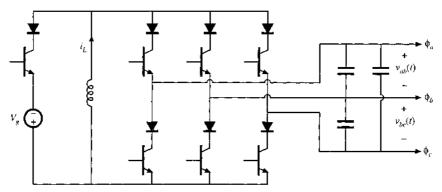

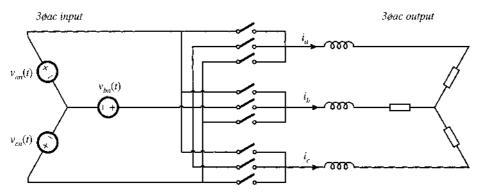

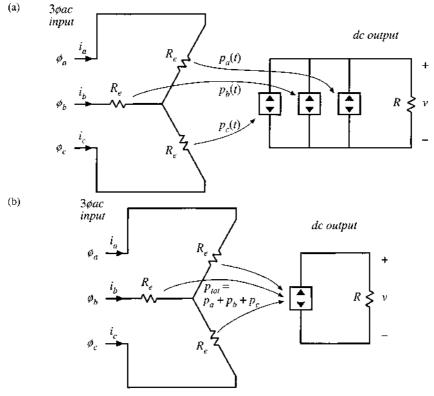

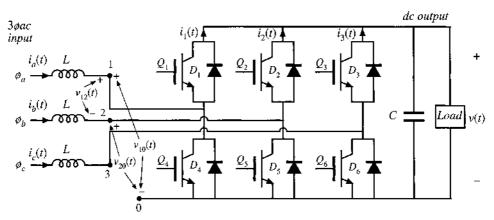

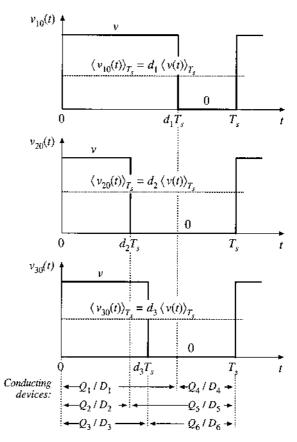

|              | 18.7                | Ideal T                                                            | hree-Phase Rectifiers                                               | 685 |  |

|              | 18.8                | Summa                                                              | ary of Key Points                                                   | 691 |  |

|              | Refe                | rences                                                             |                                                                     | 692 |  |

|              | Prob                | lems                                                               |                                                                     | 696 |  |

| $\mathbf{V}$ | Reso                | onant C                                                            | Converters                                                          | 703 |  |

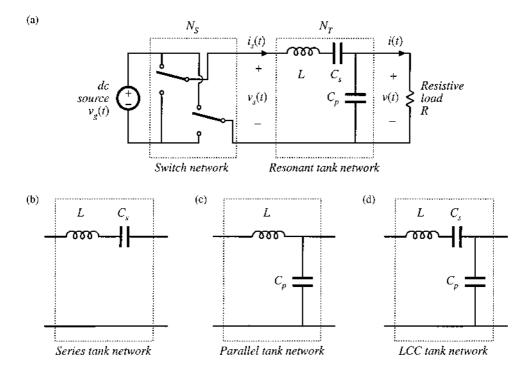

| 19           | Resonant Conversion |                                                                    |                                                                     |     |  |

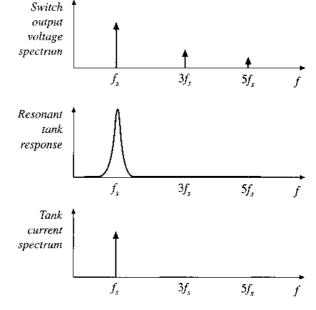

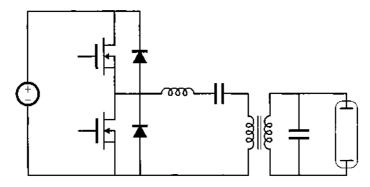

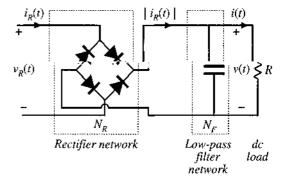

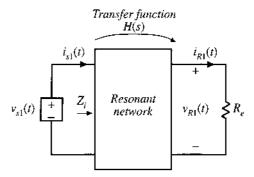

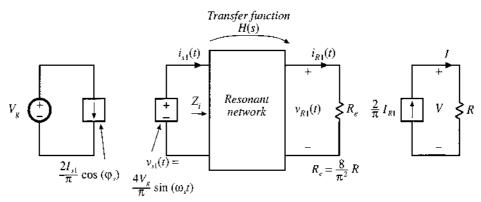

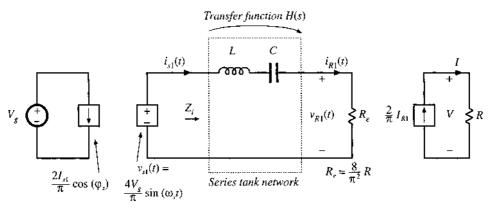

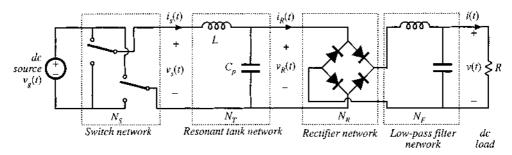

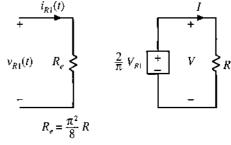

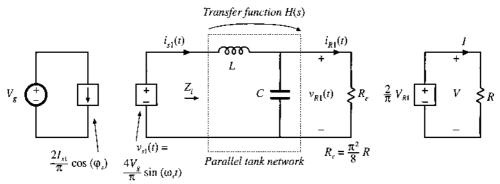

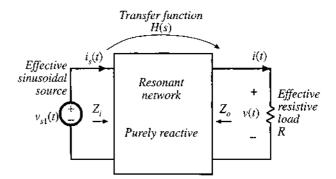

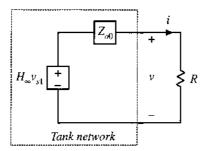

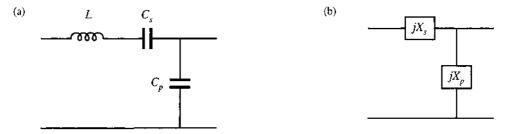

|              | 19.1                | Sinusoi                                                            | idal Analysis of Resonant Converters                                | 709 |  |

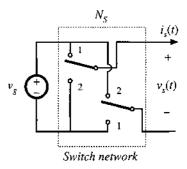

|              |                     | 19.1.1                                                             | Controlled Switch Network Model                                     | 710 |  |

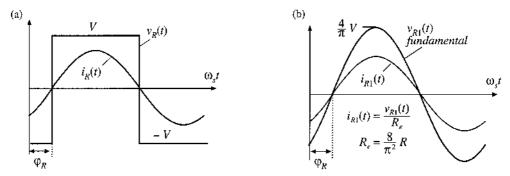

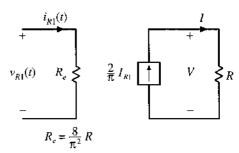

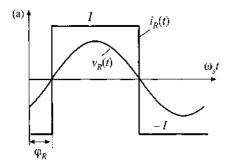

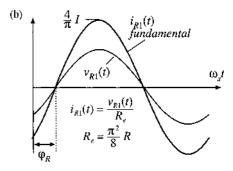

|              |                     | 19.1.2                                                             | Modeling the Rectifier and Capacitive Filter Networks               | 711 |  |

|              |                     | 19.1.3                                                             | Resonant Tank Network                                               | 713 |  |

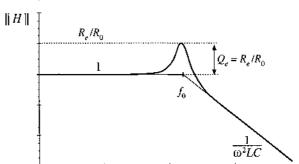

|              |                     | 19.1.4                                                             | Solution of Converter Voltage Conversion Ratio $M = V/V_{_{\rm K}}$ | 714 |  |

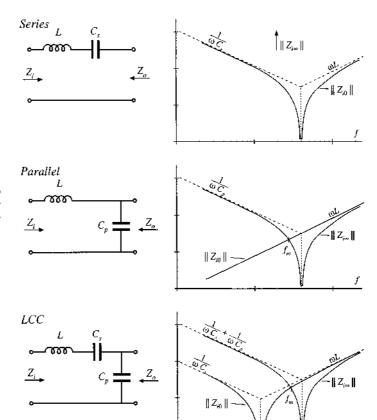

|              | 19.2                | Examp                                                              | les                                                                 | 715 |  |

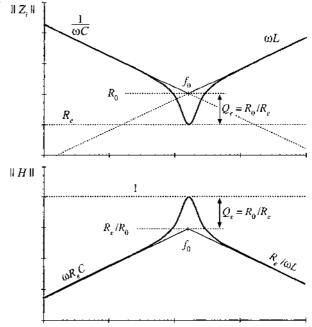

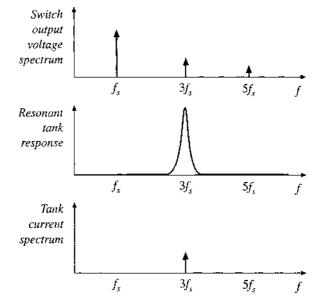

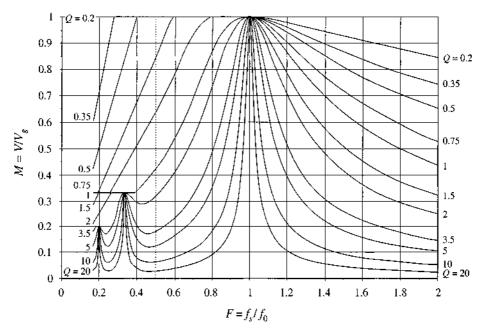

|              |                     | 19.2.1                                                             | Series Resonant DC-DC Converter Example                             | 715 |  |

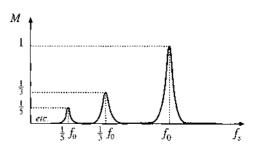

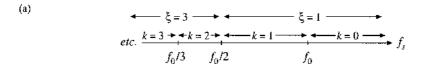

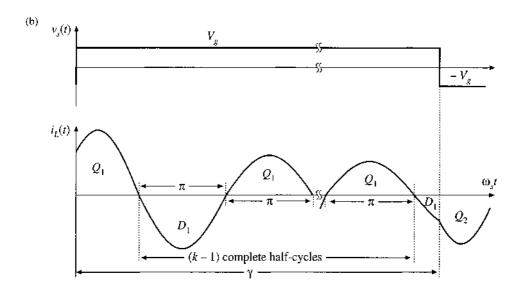

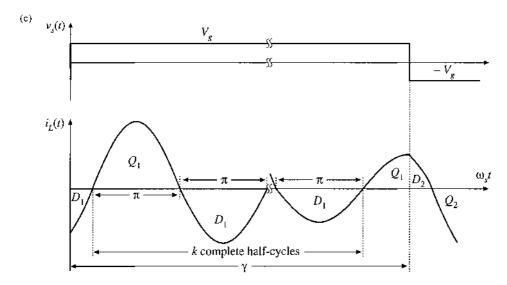

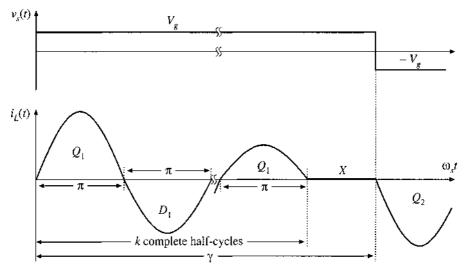

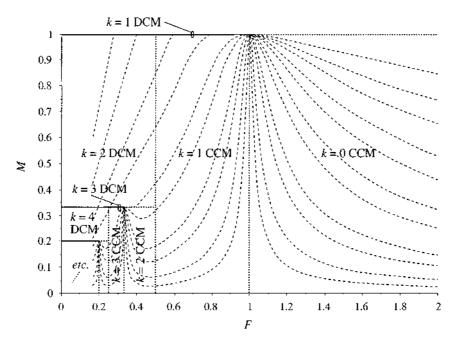

|              |                     | 19.2.2                                                             | Subharmonic Modes of the Series Resonant Converter                  | 717 |  |

|              |                     | 19.2.3                                                             | Parallel Resonant DC-DC Converter Example                           | 718 |  |

|              | 19.3                | 19.3 Soft Switching                                                |                                                                     | 721 |  |

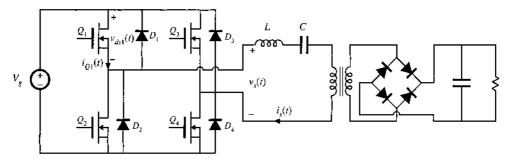

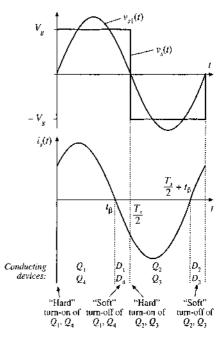

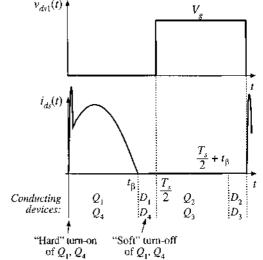

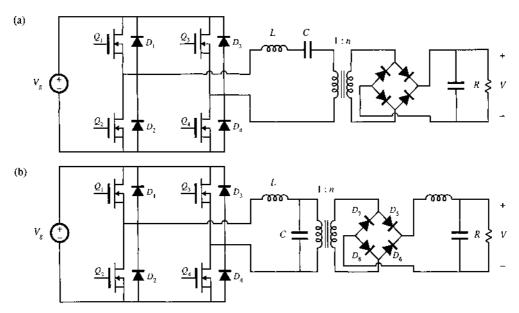

|              |                     | 19.3.1                                                             | Operation of the Full Bridge Below Resonance:                       |     |  |

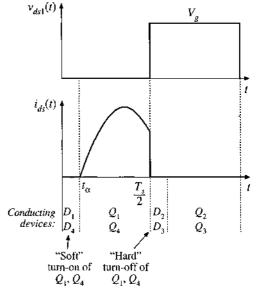

|              |                     |                                                                    | Zero-Current Switching                                              | 722 |  |

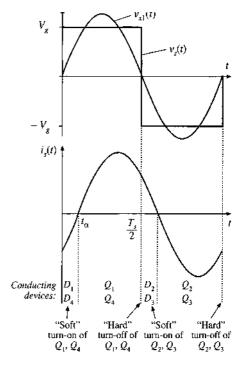

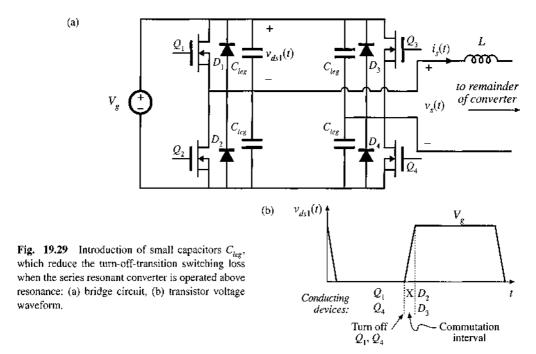

|              |                     | 19.3.2                                                             | Operation of the Full Bridge Above Resonance:                       |     |  |

|              |                     |                                                                    | Zero-Voltage Switching                                              | 723 |  |

|              | 19.4                | Load-Dependent Properties of Resonant Converters                   |                                                                     | 726 |  |

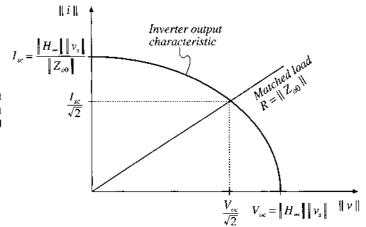

|              |                     | 19.4.1                                                             | Inverter Output Characteristics                                     | 727 |  |

|              |                     | 19.4.2                                                             | Dependence of Transistor Current on Load                            | 729 |  |

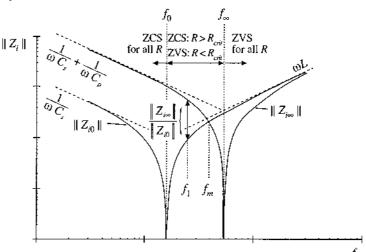

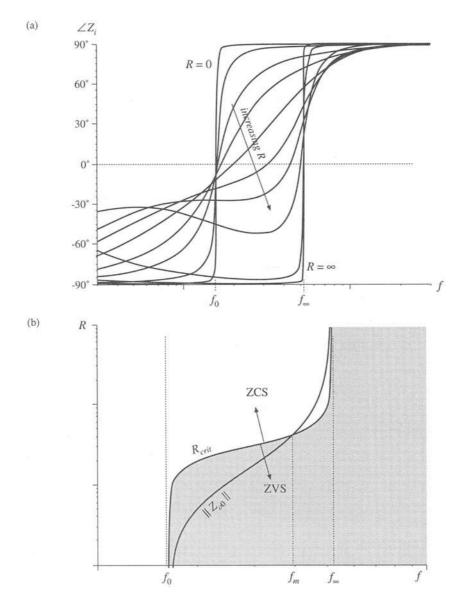

|              |                     | 19.4.3                                                             | Dependence of the ZVS/ZCS Boundary on Load Resistance               | 734 |  |

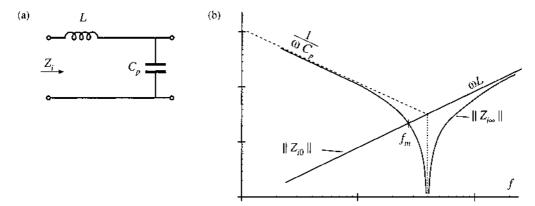

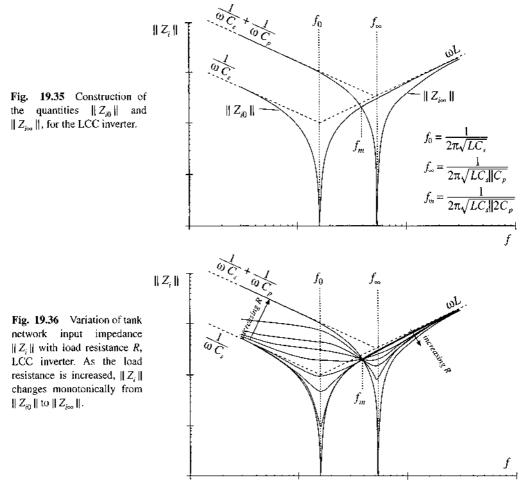

|            |                | 19.4.4                | Another Example                                                                      | 737                    |  |  |

|------------|----------------|-----------------------|--------------------------------------------------------------------------------------|------------------------|--|--|

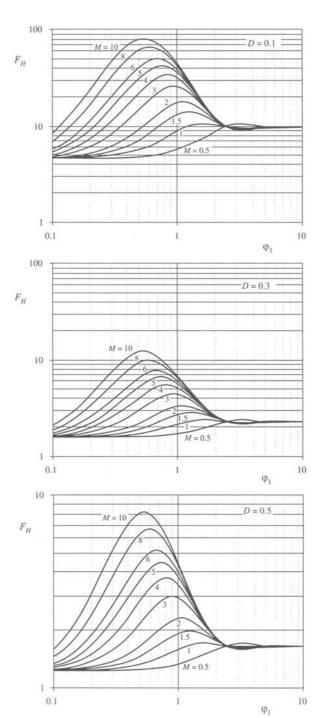

|            | 19.5           | Exact (               | Characteristics of the Series and Parallel Resonant Converters                       | 740                    |  |  |

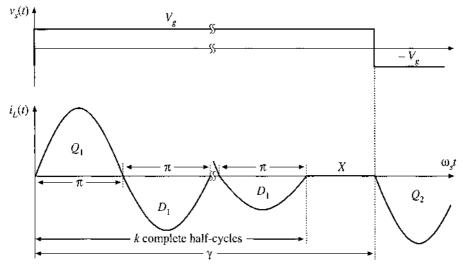

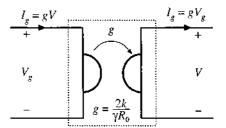

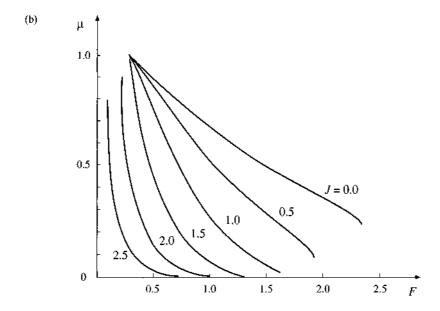

|            |                | 19.5.1                | Series Resonant Converter                                                            | 740                    |  |  |

|            |                | 19.5.2                | Parallel Resonant Converter                                                          | 748                    |  |  |

|            | 19.6           | Summary of Key Points |                                                                                      |                        |  |  |

|            | Refer          | References            |                                                                                      |                        |  |  |

|            | Probl          | ems                   |                                                                                      | 755                    |  |  |

| 20         | Soft Switching |                       |                                                                                      |                        |  |  |

|            | 20.1           | Soft-Sv               | vitching Mechanisms of Semiconductor Devices                                         | 762                    |  |  |

|            |                | 20.1.1                | Diode Switching                                                                      | 763                    |  |  |

|            |                | 20.1.2                | MOSFET Switching                                                                     | 765                    |  |  |

|            |                | 20.1.3                | IGBT Switching                                                                       | 768                    |  |  |

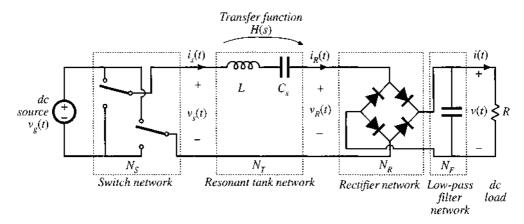

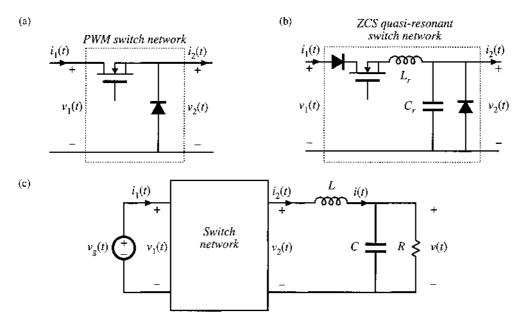

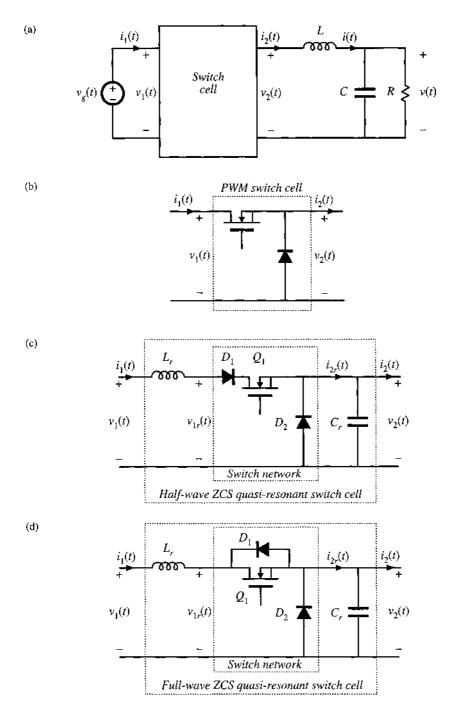

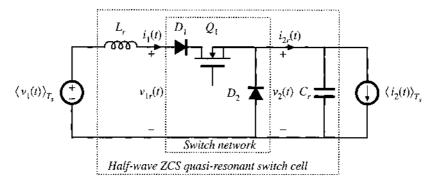

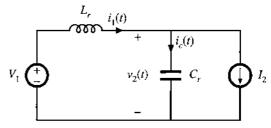

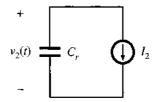

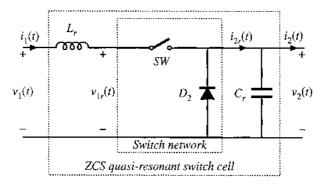

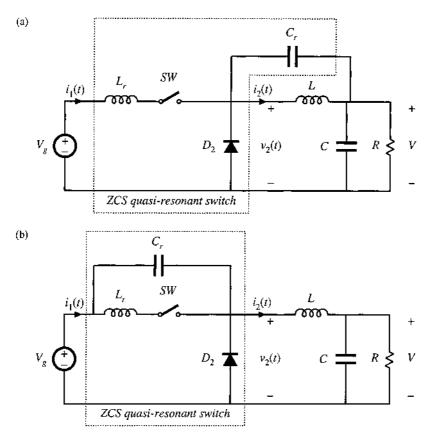

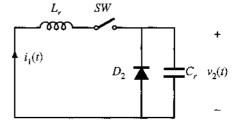

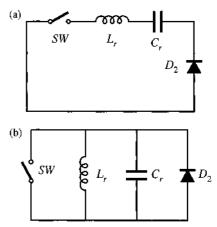

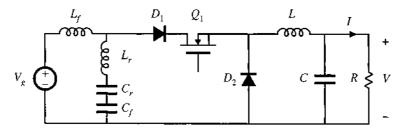

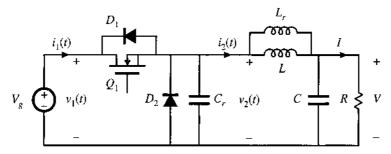

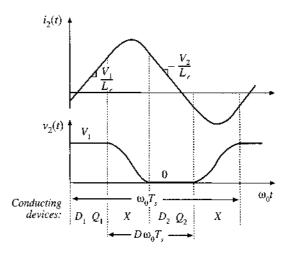

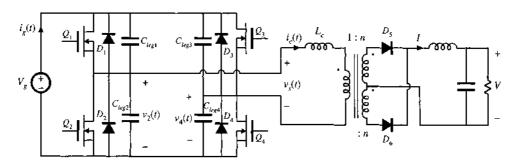

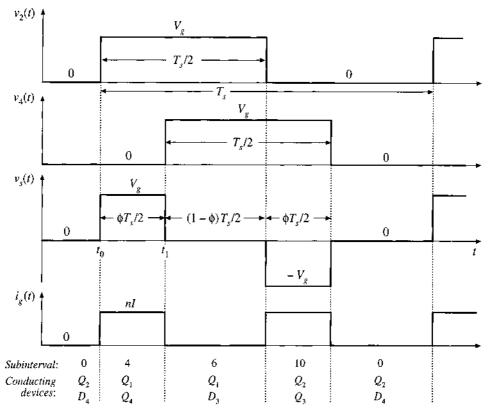

| :          | 20.2           | The Zer               | ro-Current-Switching Quasi-Resonant Switch Cell                                      | 768                    |  |  |

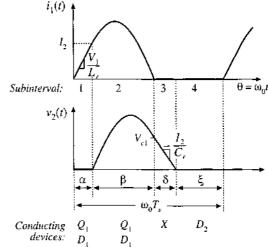

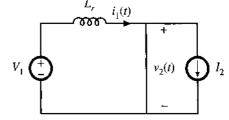

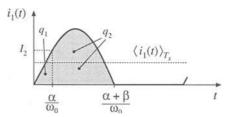

|            |                | 20.2.1                | Waveforms of the Half-Wave ZCS Quasi-Resonant Switch Cell                            | 770                    |  |  |

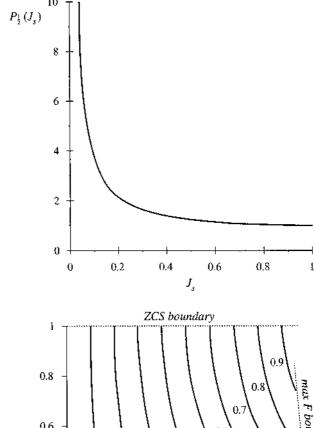

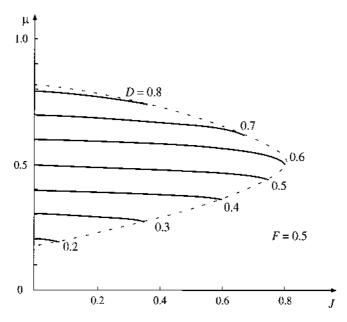

|            |                | 20.2.2                | The Average Terminal Waveforms                                                       | 774                    |  |  |

|            | 20.2           | 20.2.3                | The Full-Wave ZCS Quasi-Resonant Switch Cell                                         | 779                    |  |  |

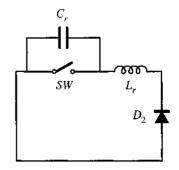

|            | 20.3           |                       | nt Switch Topologies                                                                 | 781                    |  |  |

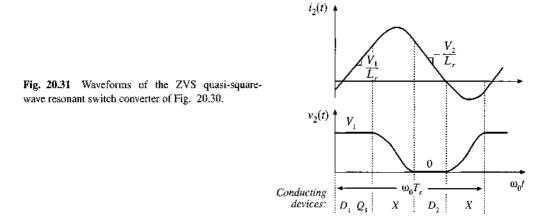

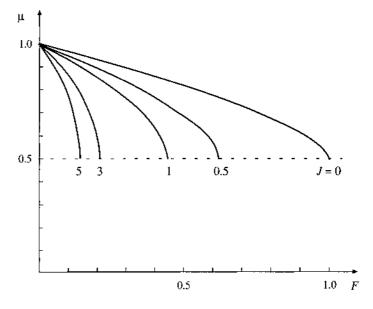

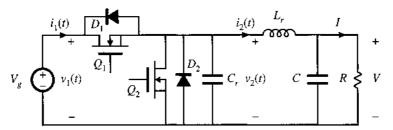

|            |                | 20.3.1 20.3.2         | The Zero-Voltage-Switching Quasi-Resonant Switch                                     | 783<br>784             |  |  |

|            |                | 20.3.2                | The Zero-Voltage-Switching Multi-Resonant Switch Quasi-Square-Wave Resonant Switches | 78 <del>4</del><br>787 |  |  |

| ,          | 20.4           |                       | vitching in PWM Converters                                                           | 790                    |  |  |

|            | 20,7.1         | 20.4.1                |                                                                                      | 791                    |  |  |

|            |                | 20.4.2                | The Auxiliary Switch Approach                                                        | 794                    |  |  |

|            |                | 20.4.3                | Auxiliary Resonant Commutated Pole                                                   | 796                    |  |  |

| :          | 20.5           | Summa                 | ry of Key Points                                                                     | 797                    |  |  |

|            | Refer          | ences                 |                                                                                      | 798                    |  |  |

|            | Proble         | ems                   |                                                                                      | 800                    |  |  |

| Appendices |                |                       |                                                                                      |                        |  |  |

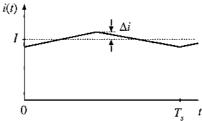

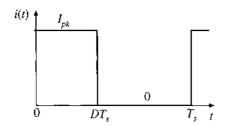

| Appe       | ndix A         | A R                   | MS Values of Commonly-Observed Converter Waveforms                                   | 805                    |  |  |

|            | A.1            | Some C                | Common Waveforms                                                                     | 805                    |  |  |

|            | A.2            | Genera                | l Piecewise Waveform                                                                 | 809                    |  |  |

| Appc       | ndix l         | B Si                  | mulation of Converters                                                               | 813                    |  |  |

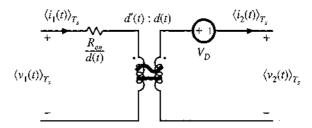

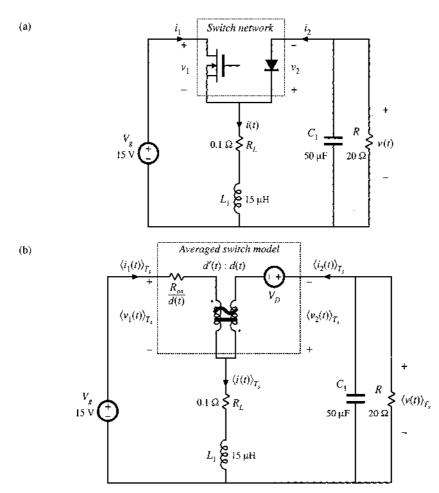

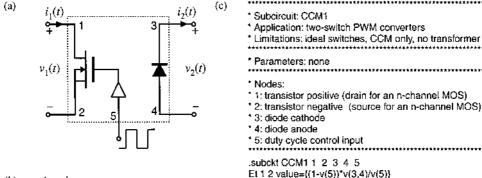

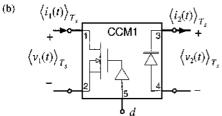

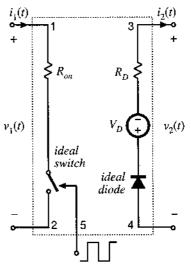

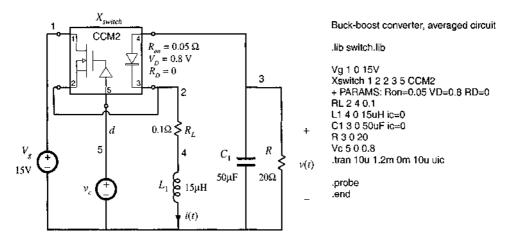

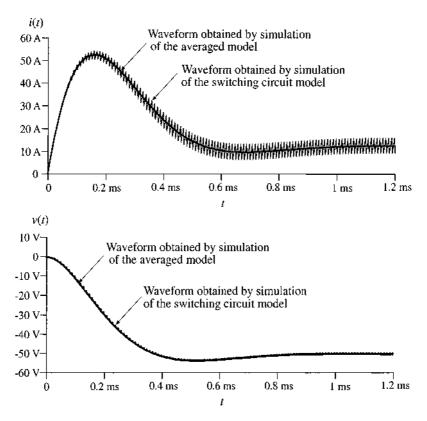

|            | B.1            | Average               | ed Switch Models for Continuous Conduction Mode                                      | 815                    |  |  |

|            |                | B.1.1                 | Basic CCM Averaged Switch Model                                                      | 815                    |  |  |

|            |                | B.1.2                 | CCM Subcircuit Model that Includes Switch Conduction Losses                          | 816                    |  |  |

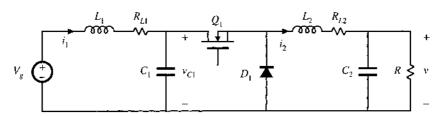

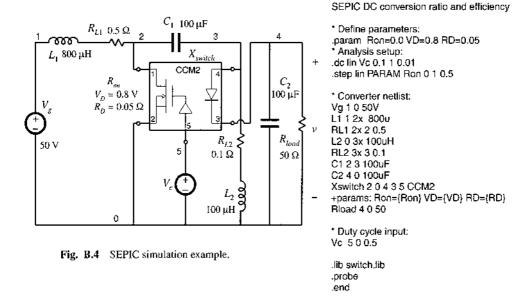

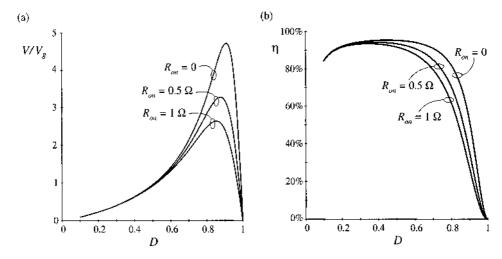

|            |                | B.1.3                 | Example: SEPIC DC Conversion Ratio and Efficiency                                    | 818                    |  |  |

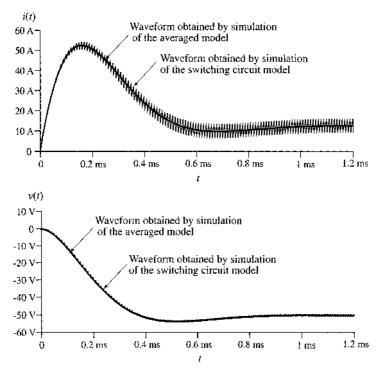

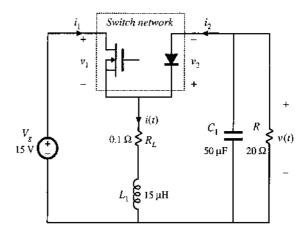

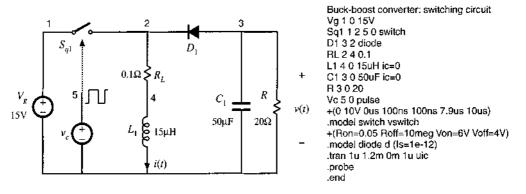

|            |                | B.1.4                 | Example: Transient Response of a Buck-Boost Converter                                | 819                    |  |  |

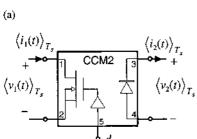

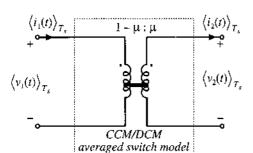

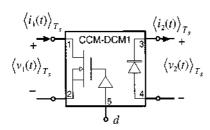

| i          | <b>B</b> .2    |                       | ned CCM/DCM Averaged Switch Model                                                    | 822                    |  |  |

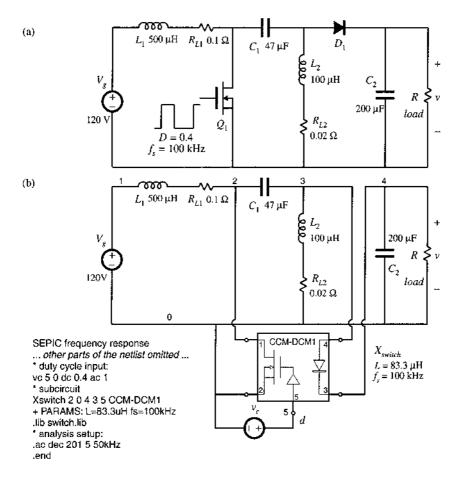

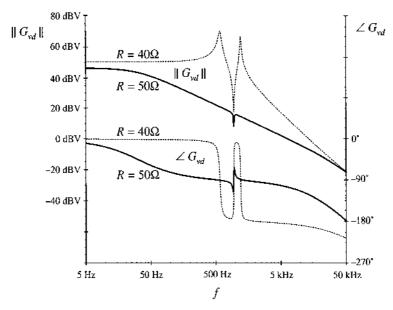

|            |                | B.2.1                 | Example: SEPIC Frequency Responses                                                   | 825                    |  |  |

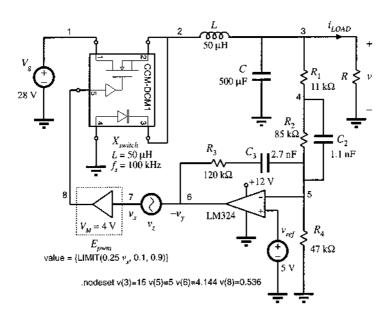

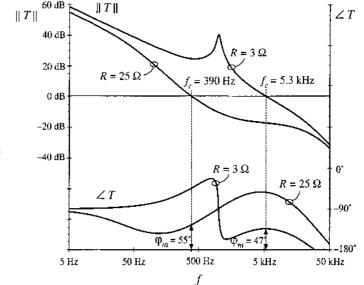

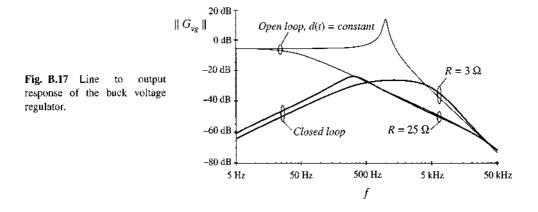

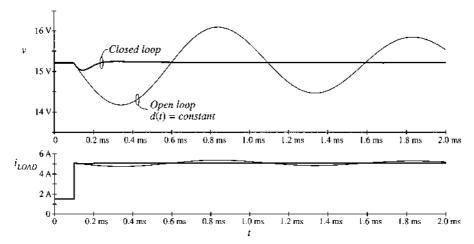

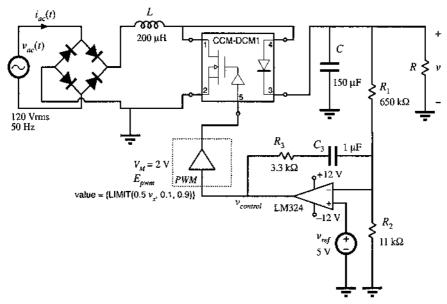

|            |                | B.2.2                 | Example: Loop Gain and Closed-Loop Responses of a Buck Voltage Regulator             | 827                    |  |  |

|            |                |                       | of a Duck voltage regulator                                                          | 627                    |  |  |

|                                                |                                                         | Contents        | xvii |  |

|------------------------------------------------|---------------------------------------------------------|-----------------|------|--|

|                                                |                                                         |                 |      |  |

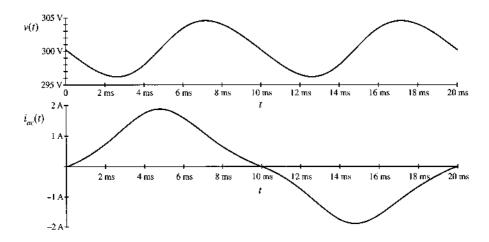

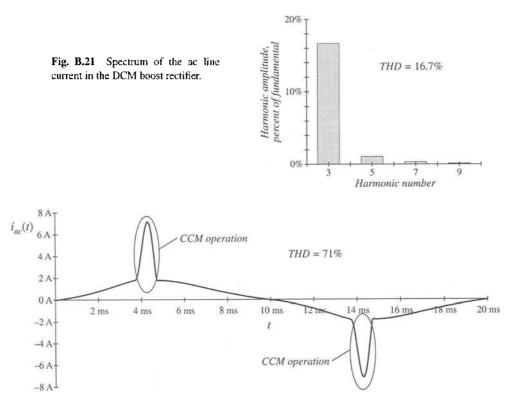

|                                                | B.2.3 Example: DCM Boost Rectifier                      |                 | 832  |  |

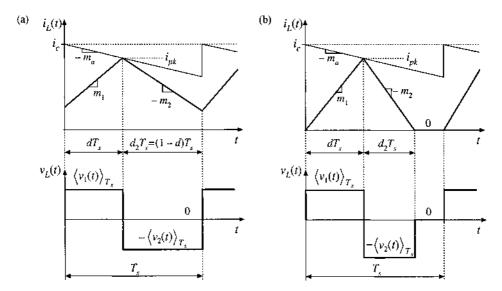

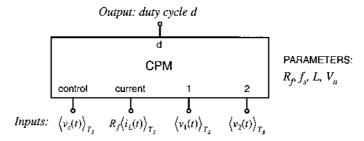

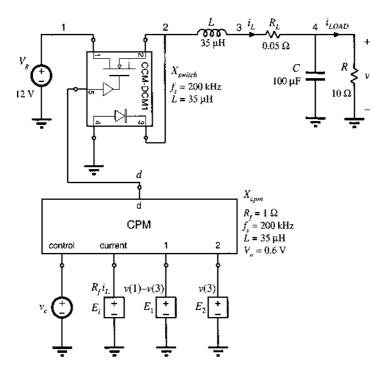

| B.3                                            | Current Programmed Control                              |                 | 834  |  |

|                                                | B.3.1 Current Programmed Mode Model for Simulation      |                 | 834  |  |

|                                                | B.3.2 Example: Frequency Responses of a Buck Convert    | er with         |      |  |

|                                                | Current Programmed Control                              |                 | 837  |  |

| Refe                                           | rences                                                  |                 | 840  |  |

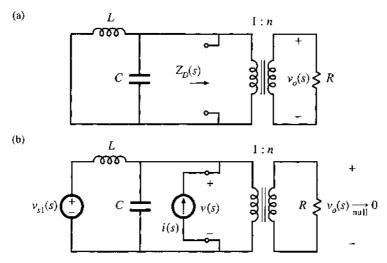

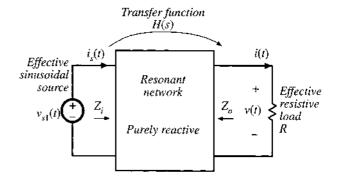

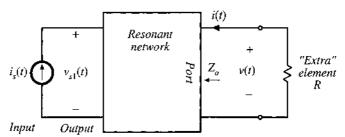

| Appendix C Middlebrook's Extra Element Theorem |                                                         | 843             |      |  |

| C.I                                            | Basic Result                                            |                 | 843  |  |

| C.2                                            | Derivation                                              |                 | 846  |  |

| C.3                                            | Discussion                                              |                 |      |  |

| C.4                                            | Examples                                                |                 |      |  |

|                                                | C.4.1 A Simple Transfer Function                        |                 | 850  |  |

|                                                | C.4.2 An Unmodeled Element                              |                 | 855  |  |

|                                                | C.4.3 Addition of an Input Filter to a Converter        |                 | 857  |  |

|                                                | C.4.4 Dependence of Transistor Current on Load in a Re- | sonant Inverter | 859  |  |

| Refe                                           | erences                                                 |                 | 861  |  |

| Appendix D Magnetics Design Tables             |                                                         | 863             |      |  |

| D.1                                            | Pot Core Data                                           |                 | 864  |  |

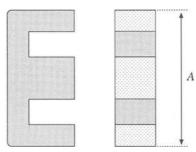

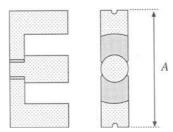

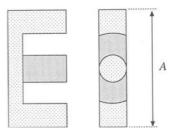

| D.2                                            | EE Core Data                                            |                 | 865  |  |

| D.3                                            | EC Core Data                                            |                 | 866  |  |

| D.4                                            | ETD Core Data                                           |                 | 866  |  |

| D.5                                            | PQ Core Data                                            |                 | 867  |  |

| D.6                                            | American Wire Gauge Data                                |                 | 868  |  |

|                                                | rences                                                  |                 | 869  |  |

| Index                                          |                                                         |                 |      |  |

### Preface

The objective of the First Edition was to serve as a textbook for introductory power electronics courses where the fundamentals of power electronics are defined, rigorously presented, and treated in sufficient depth so that students acquire the knowledge and skills needed to design practical power electronic systems. The First Edition has indeed been adopted for use in power electronics courses at a number of schools. An additional goal was to contribute as a reference book for engineers who practice power electronics design, and for students who want to develop their knowledge of the area beyond the level of introductory courses. In the Second Edition, the basic objectives and philosophy of the First Edition have not been changed. The modifications include addition of a number of new topics aimed at better serving the expanded audience that includes students of introductory and more advanced courses, as well as practicing engineers looking for a reference book and a source for further professional development. Most of the chapters have been significantly revised and updated. Major additions include a new Chapter 10 on input filter design, a new Appendix B covering simulation of converters, and a new Appendix C on Middlebrook's Extra Element Theorem, In addition to the introduction of new topics, we have made major revisions of the material to improve the flow and clarity of explanations and to provide additional specific results, in chapters covering averaged switch modeling, dynamics of converters operating in discontinuous conduction mode, current mode control, magnetics design, pulse-width modulated rectifiers, and resonant and soft-switching converters.

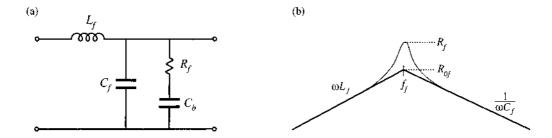

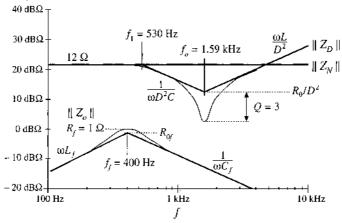

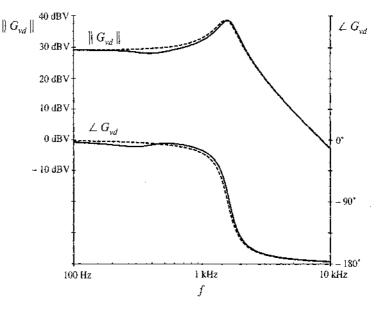

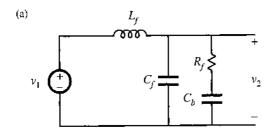

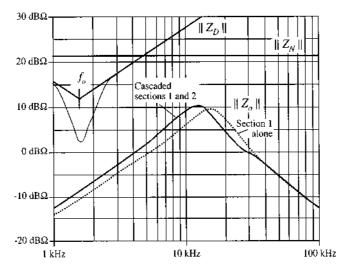

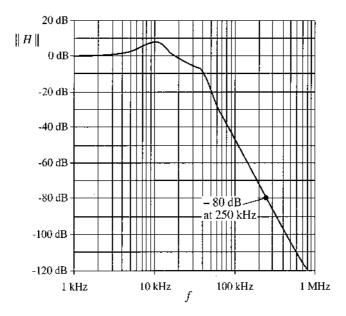

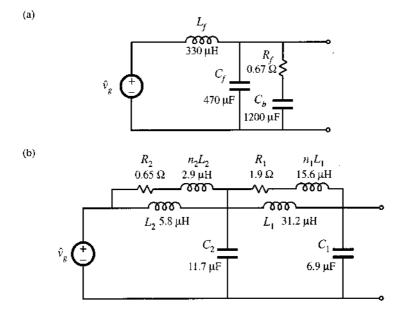

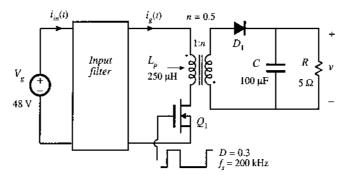

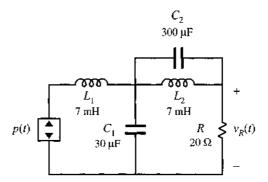

A completely new Chapter 10 covering input filter design has been added to the second addition. The problem of how the input filter affects the dynamics of the converter, often in a manner that degrades stability and performance of the converter system, is explained using Middlebrook's Extra Element Theorem. This design-oriented approach is explained in detail in the new Appendix C. Simple conditions are derived to allow filter damping so that converter transfer functions are not changed. Complete results for optimum filter damping are presented. The chapter concludes with a discussion about the design of multiple-section filters, illustrated by a design example.

Computer simulation based on the averaged switch modeling approach is presented in Appendix B, including PSpice models for continuous and discontinuous conduction mode, and current-mode control. Extensive simulation examples include: finding the dc conversion ratio and efficiency of a SEPIC, plotting the transient response of a buck-boost converter, comparing the control-to-output transfer functions of a SEPIC operating in CCM and DCM, determining the loop gain, line-to-output transfer function, and load transient response of a closed-loop buck voltage regulator, finding the input current

waveform and THD of a DCM boost rectifier, and comparing the transfer functions and output impedances of buck converters operating with current programmed control and with duty cycle control. The major purpose of Appendix B is to supplement the text discussions, and to enable the reader to effectively use averaged models and simulation tools in the design process. The role of simulation as a design verification tool is emphasized. In our experience of teaching introductory and more advanced power electronics courses, we have found that the use of simulation tools works best with students who have mastered basic concepts and design-oriented analytical techniques, so that they are able to make correct interpretations of simulation results and model limitations. This is why we do not emphasize simulation in introductory chapters. Nevertheless, Appendix B is organized so that simulation examples can be introduced together with coverage of the theoretical concepts of Chapters 3, 7, 9, 10, 11, 12, and 18.

Middlebrook's Extra Element Theorem is presented in Appendix C, together with four tutorial examples. This valuable design-oriented analytical tool allows one to examine effects of adding an extra element to a linear system, without solving the modified system all over again. The theorem has many practical applications in the design of electronic circuits, from solving circuits by inspection, to quickly finding effects of unmodeled parasitic elements. In particular, in the Second Edition, Middlebrook's Extra Element Theorem is applied to the input filter design of Chapter 10, and to resonant inverter design in Chapter 19.

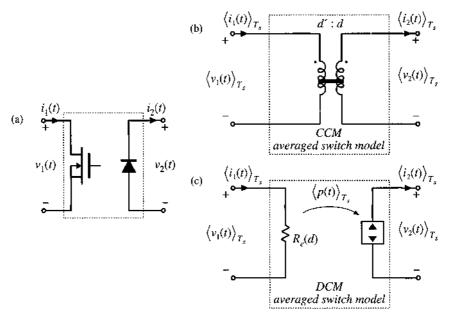

In Chapter 7, we have revised the section on circuit averaging and averaged switch modeling. The process of circuit averaging and deriving averaged switch models has been explained to allow readers not only to use the basic models, but also to construct averaged models for other applications of interest. Examples of extensions of the averaged switch modeling approach include modeling of switch conduction and switching losses. Related to the revision of Chapter 7, in Appendix B we have included new material on simulation of converters based on the averaged switch modeling approach.

Chapter 8 contains a new substantial introduction that explains the engineering design process and the need for design-oriented analysis. The discussions of design-oriented methods for construction of frequency response have been revised and expanded. A new example has been added, involving approximate analysis of a damped input filter.

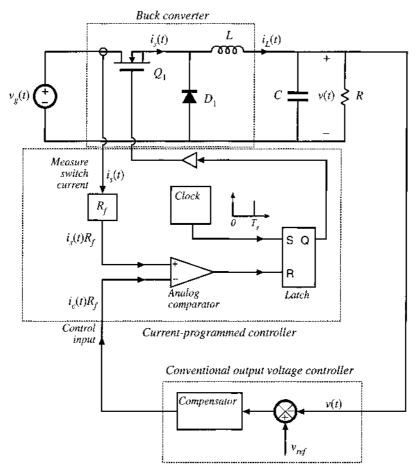

Chapter 11 on dynamics of DCM (discontinuous conduction mode) converters, and Chapter 12 on current-mode control, have been thoroughly revised and updated. Chapter 11 includes a simplified derivation of DCM averaged switch models, as well as an updated discussion of high-frequency DCM dynamics. Chapter 12 includes a new, more straightforward explanation and discussion of current-mode dynamics, as well as new complete results for transfer functions and model parameters of all basic converters.

The chapters on magnetics design have been significantly revised and reorganized. Basic magnetics theory necessary for informed design of magnetic components in switching power converters is presented in Chapter 13. The description of the proximity effect has been completely revised, to explain this important but complex subject in a more intuitive manner. The design of magnetic components based on the copper loss constraint is described in Chapter 14. A new step-by-step design procedure is given for multiple-winding inductors, and practical design examples are included for the design of filter inductors, coupled inductors and flyback transformers. The design of magnetic components (transformers and ac inductors) based on copper and core loss considerations is described in Chapter 15.

To improve their logical flow, the chapters covering pulse-width modulated rectifiers have been combined into a single Chapter 18, and have been completely reorganized. New sections on current control based on the critical conduction mode, as well as on operation of the CCM boost and DCM flyback as PWM rectifiers, have been added.

Part V consists of Chapter 19 on resonant converters and Chapter 20 on soft-switching converters. The discussion of resonant inverter design, a topic of importance in the field of high-frequency electronic ballasts, has been expanded and explained in a more intuitive manner. A new resonant inverter

design example has also been added to Chapter 19. Chapter 20 contains an expanded tutorial explanation of switching loss mechanisms, new charts illustrating the characteristics of quasi-square-wave and multi-resonant converters, and new up-to-date sections about soft-switching converters, including the zero-voltage transition full-bridge converter, the auxiliary switch approach, and the auxiliary resonant commutated pole approach for dc-dc converters and dc-ac inverters.

The material of the Second Edition is organized so that chapters or sections of the book can be selected to offer an introductory one-semester course, but yet enough material is provided for a sequence of more advanced courses, or for individual professional development. At the University of Colorado, we cover the material from the Second Edition in a sequence of three semester-long power electronics courses. The first course, intended for seniors and first-year graduate students, covers Chapters 1 to 6, Sections 7.1, 7.2, 7.5, and 7.6 from Chapter 7, Chapters 8 and 9, and Chapters 13 to 15. A project-oriented power electronics design laboratory is offered in parallel with this course. This course serves as a prerequisite for two follow-up courses. The second course starts with Section 7.4, proceeds to Appendices B and C, Chapters 10, 11 and 12, and concludes with the material of Chapters 16 to 18. In the third course we cover resonant and soft-switching techniques of Chapters 19 and 20.

The website for the Second Edition contains comprehensive supporting materials for the text, including solved problems and slides for instructors. Computer simulation files can be downloaded from this site, including a PSpice library of averaged switch models, and simulation examples.

This text has evolved from courses developed over seventeen years of teaching power electronics at the University of Colorado. These courses, in turn, were heavily influenced by our previous experiences as graduate students at the California Institute of Technology, under the direction of Profs. Slobodan Ćuk and R. D. Middlebrook, to whom we are grateful. We appreciate the helpful suggestions of Prof. Arthur Witulski of the University of Arizona. We would also like to thank the many readers of the First Edition, students, and instructors who offered their comments and suggestions, or who pointed out errata. We have attempted to incorporate these suggestions wherever possible.

ROBERT W. ERICKSON DRAGAN MAKSIMOVIĆ Boulder, Colorado

# 1 Introduction

#### 1.1 INTRODUCTION TO POWER PROCESSING

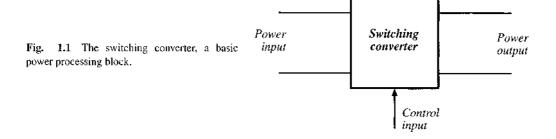

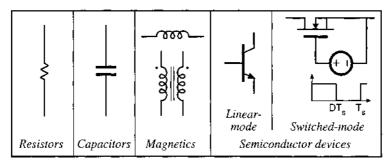

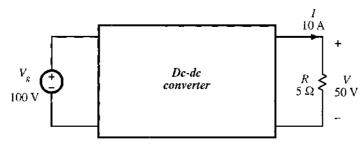

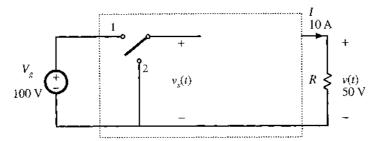

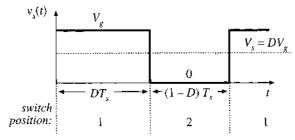

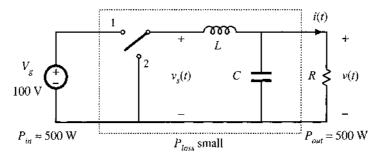

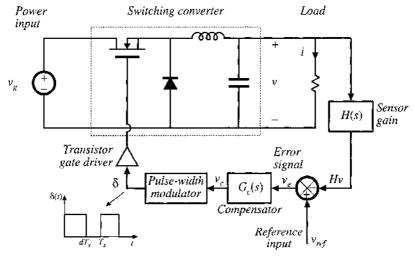

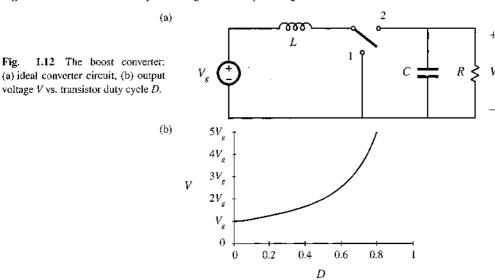

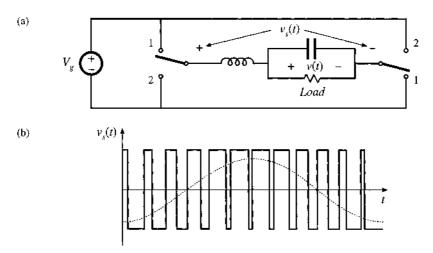

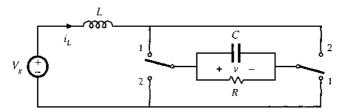

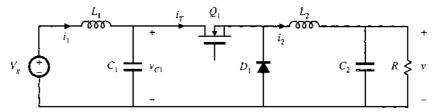

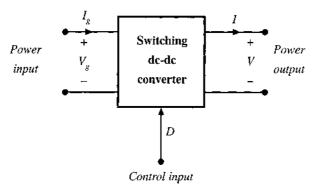

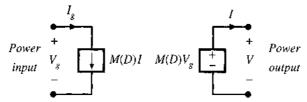

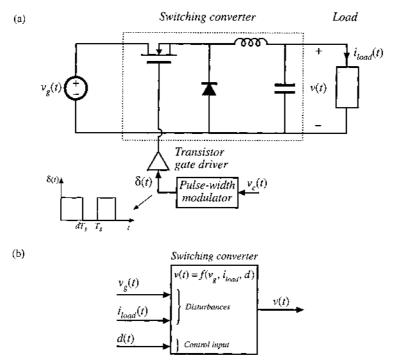

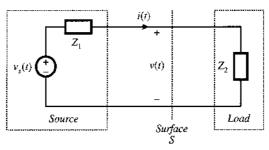

The field of power electronics is concerned with the processing of electrical power using electronic devices [1–7]. The key element is the *switching converter*, illustrated in Fig. 1.1. In general, a switching converter contains power input and control input ports, and a power output port. The raw input power is processed as specified by the control input, yielding the conditioned output power. One of several basic functions can be performed [2]. In a *dc-dc converter*, the dc input voltage is converted to a dc output voltage having a larger or smaller magnitude, possibly with opposite polarity or with isolation of the input and output ground references. In an ac-dc *rectifier*, an ac input voltage is rectified, producing a dc output voltage. The dc output voltage and/or ac input current waveform may be controlled. The inverse process, dc-ac *inversion*, involves transforming a dc input voltage into an ac output voltage of controllable magnitude and frequency. Ac-ac *cycloconversion* involves converting an ac input voltage to a given ac output voltage of controllable magnitude and frequency.

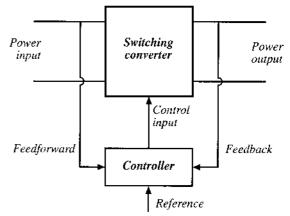

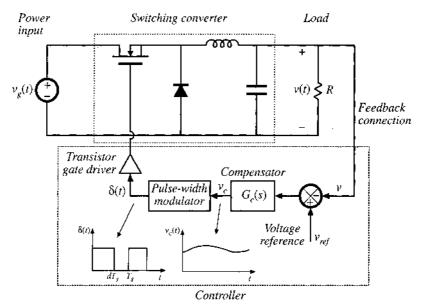

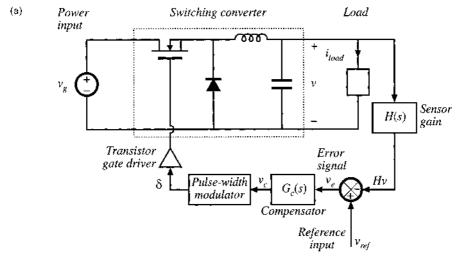

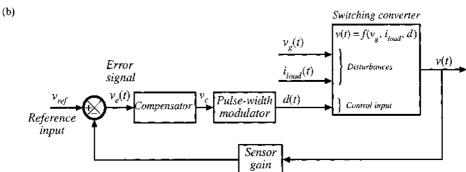

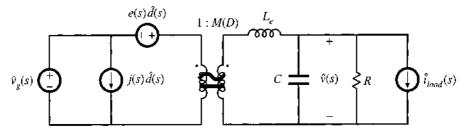

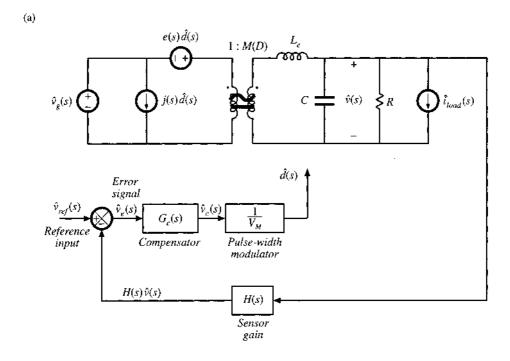

Control is invariably required. It is nearly always desired to produce a well-regulated output

Fig. 1.2 A controller is generally required.

voltage, in the presence of variations in the input voltage and load current. As illustrated in Fig. 1.2, a controller block is an integral part of any power processing system.

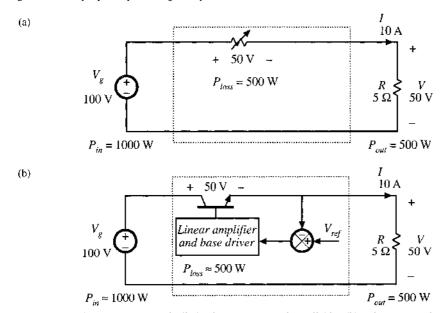

High efficiency is essential in any power processing application. The primary reason for this is usually not the desire to save money on one's electric bills, nor to conserve energy, in spite of the nobility of such pursuits. Rather, high efficiency converters are necessary because construction of low-efficiency converters, producing substantial output power, is impractical. The efficiency of a converter having output power  $P_{out}$  and input power  $P_{in}$  is

$$\eta = \frac{P_{obt}}{P_{ob}} \tag{1.1}$$

The power lost in the converter is

$$P_{loss} = P_{in} - P_{out} = P_{out} \left(\frac{1}{\eta} - 1\right)$$

(1.2)

Equation (1.2) is plotted in Fig. 1.3. In a converter that has an efficiency of 50%, power  $P_{loss}$  is dissipated by the converter elements and this is equal to the output power,  $P_{out}$ . This power is converted into heat, which must be removed from the converter. If the output power is substantial, then so is the loss power. This leads to a large and expensive cooling system, it causes the electronic elements within the converter to operate at high temperature, and it reduces the system reliability. Indeed, at high output powers, it may be impossible to adequately cool the converter elements using current technology.

Increasing the efficiency is the key to obtaining higher output powers. For example, if the converter efficiency is 90%, then the converter loss power is equal to only 11%

Fig. 1.3 Converter power loss vs. efficiency.

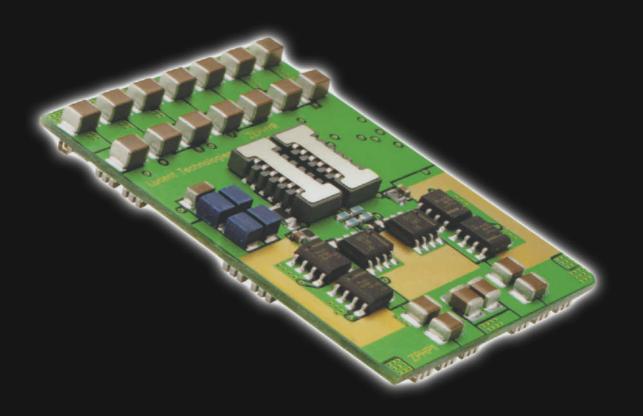

Fig. 1.4 A goal of current converter technology is to construct converters of small size and weight, which process substantial power at high efficiency.

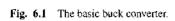

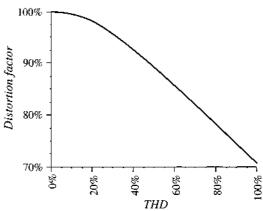

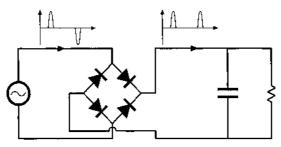

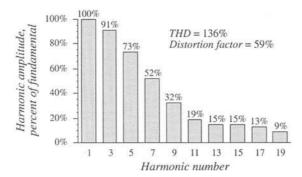

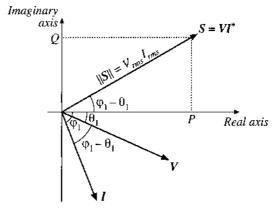

of the output power. Efficiency is a good measure of the success of a given converter technology. Figure 1.4 illustrates a converter that processes a large amount of power, with very high efficiency. Since very little power is lost, the converter elements can be packaged with high density, leading to a converter of small size and weight, and of low temperature rise.