#### FOR MORE EXCLUSIVE

# (Civil, Mechanical, EEE, ECE) ENGINEERING & GENERAL STUDIES

(Competitive Exams)

TEXT BOOKS, IES GATE PSU's TANCET & GOVT EXAMS

NOTES & ANNA UNIVERSITY STUDY MATERIALS

VISIT

#### www.EasyEngineering.net

AN EXCLUSIVE WEBSITE FOR ENGINEERING STUDENTS & GRADUATES

\*\*Note: Other Websites/Blogs Owners Please do not Copy (or) Republish this Materials without Legal Permission of the Publishers.

\*\*Disclimers: EasyEngineering not the original publisher of this Book/Material on net. This e-book/Material has been collected from other sources of net.

TECHNICAL PUBLICATIONS PUNE

# Digital Electronics

A. P. Godse D. A. Godse

Technical Publications Pune

Downloaded From: www.EasyEngineering.net

### Digital Electronics

ISBN 978-81-89411-32-9

All rights reserved with Technical Publications. No part of this book should be reproduced in any form, Electronic, Mechanical, Photocopy or any information storage and retrieval system without prior permission in writing, from Technical Publications, Pune.

#### Published by:

#### Technical Publications Pune®

#1, Amit Residency, 412, Shaniwar Peth, Pune - 411 030, India.

#### Printer:

Alert DTPrinters

Sr. no 10/3, Sinhagad Road,

Pune - 411 041

EEEbooks4U

## **Table of Contents**

| Jna | apter 1 Number Systems                             |    |

|-----|----------------------------------------------------|----|

|     | 1.1 Introduction                                   | 1  |

|     | 1.2 Decimal Number System                          | 1  |

|     | 1.3 Binary Number System                           | 2  |

|     | 1.3.1 Binary Counting                              | 3  |

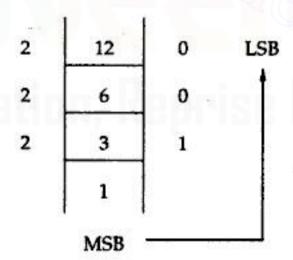

|     | 1.3.2 Binary-to-Decimal Conversion                 | 3  |

|     | 1.3.3 Fractions                                    | 5  |

|     | 1.3.4 Mixed Numbers                                | 5  |

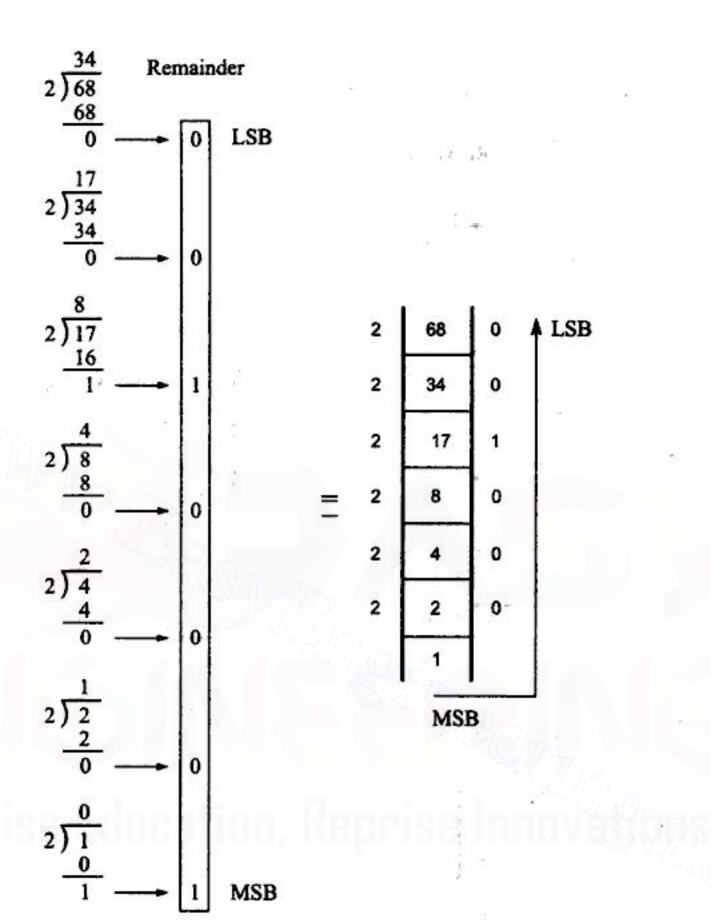

|     | 1.3.5 Decimal to Binary Conversion                 | 6  |

|     | 1.3.6 Fractional Decimal to Binary Conversion      | 8  |

| 10  | 1.3.7 Binary Arithmetic                            | 10 |

|     | 1.3.8 Signed Binary Numbers                        | 11 |

|     | 1.3.9 2's Complement Arithmetic                    | 13 |

|     | 1.4 Octal Numbers System                           | 16 |

|     | 1.4.1 Octal to Decimal Conversion                  | 17 |

|     | 1.4.2 Fractions                                    | 17 |

|     | 1.4.3 Mixed Numbers                                | 17 |

| - 2 | 1.4.4 Decimal to Octal Conversion                  | 17 |

|     | 1.4.5 Fractional Decimal to Octal Conversion       | 18 |

|     | 1.4.6 Binary to Octal Conversion                   | 18 |

|     | 1.4.7 Octal to Binary Conversion                   | 19 |

|     | 1.4.8 Usefulness of Octal System                   | 19 |

|     | 1.4.9 Octal Arithmetic                             | 19 |

|     | 1.5 Hexadecimal Number System                      | 23 |

| -   | 1.5.1 Hexadecimal to Decimal Conversion            | 24 |

|     | 1.5.2 Fractions                                    | 24 |

|     | 1.5.3 Mixed Numbers                                | 24 |

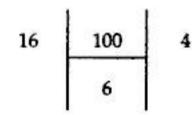

|     | 1.5.4 Decimal to Hexadecimal Conversion            | 25 |

|     | 1.5.5 Fractional Decimal to Hexadecimal Conversion | 25 |

|     | 1.5.6 Binary to Hexadecimal Conversion             | 25 |

|     | 1.5.7 Hexadecimal to Binary Conversion             | 26 |

|     | 1.5.8 Octal to Hexadecimal Conversion              | 26 |

|     | 1.5.9 Hexadecimal to Octal Conversion              | 26 |

|     | 1.5.10 Hexadecimal Arithmetic                      | 27 |

|     |                                                    |    |

| 1       | 3.2.2 Condition for Error Detection               | 78    |

|---------|---------------------------------------------------|-------|

| 3,      | 3.3 Parity Bit                                    | 78    |

| Ť       | 3.4 Block Parity                                  | 80    |

|         | 3.5 Linear Block Codes                            | 81    |

| ¥ 5-    | 3.5.1 Matrix Representation of Linear Block Codes | . 81  |

| 7       | 3.5.2 Generalized Steps for Construction of Code  | 83    |

| 150     | 3.5.3 Decoding the Received Codewords             | 85    |

| 57      | 3.5.4 Error Correction                            | 88    |

| 2       | 3.6 Binary Cyclic Codes                           | 90    |

|         | 3.7 Burst Code                                    | 91    |

|         | 3.8 Check-sums and Cyclic Redundancy Checks       | 92    |

|         | 3.9 Hamming Code                                  | 92    |

| 2.      | 3.9.1 Number of Parity Bits                       | 92    |

| 37      | 3.9.2 Locations of the Parity Bits in the Code    | 93    |

| 0.93    | 3.9.3 Assigning Values to Parity Bits             | 93    |

| 19      | 3.9.4 Detecting and Correcting an Error           | 95    |

| 10.70   | University Questions                              | 97    |

| <u></u> | 4.1 Introduction                                  | 99    |

|         | 4.2 Logical Operators                             | 100   |

|         | 4.2.1 Logical Operator NOT/INVERT                 | 100   |

|         | 4.2.2 Logical operator AND                        | 100   |

|         | 4.2.3 Logical Operator OR                         | 101   |

|         | 4.3 Logic Gates                                   | 101   |

|         | 4.3.1 Inverter : NOT gate                         | 102   |

|         | 4.3.2 AND gate                                    | 103   |

| (9)     | 4.3.3 The OR Gate                                 | 106   |

| 100     | 4.3.4 The NAND gate                               | 108   |

|         | 4.3.5 The NOR Gate                                | 110   |

|         | 4.3.6 The Exclusive-OR Gate                       | 112   |

| 1       | 4.3.7 The Exclusive-NOR Gate                      | . 114 |

| 75      | 4.4 Boolean Algebra                               | 117   |

| 7.      | 4.4.1 Logic Expressions                           | 117   |

| 12      | 4.4.2 Laws of Boolean Algebra                     | 118   |

|         | 4.4.3 Rules in Boolean Algebra                    | 121   |

|         | 4.4.4 Duality Theorem                             | 125   |

|                          | 7.5.2 Full-Subtractor                                 | 348 |

|--------------------------|-------------------------------------------------------|-----|

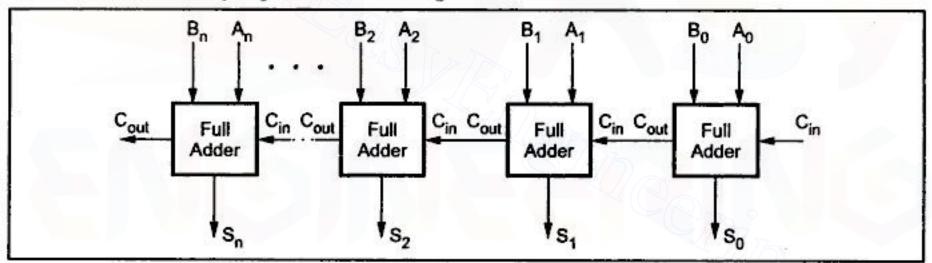

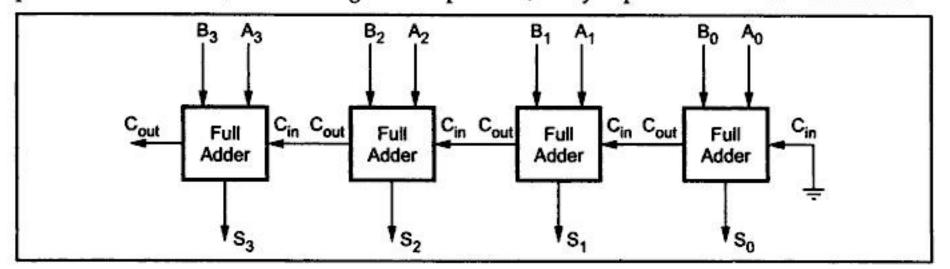

| 7.6                      | n-Bit Parallel Adder                                  | 351 |

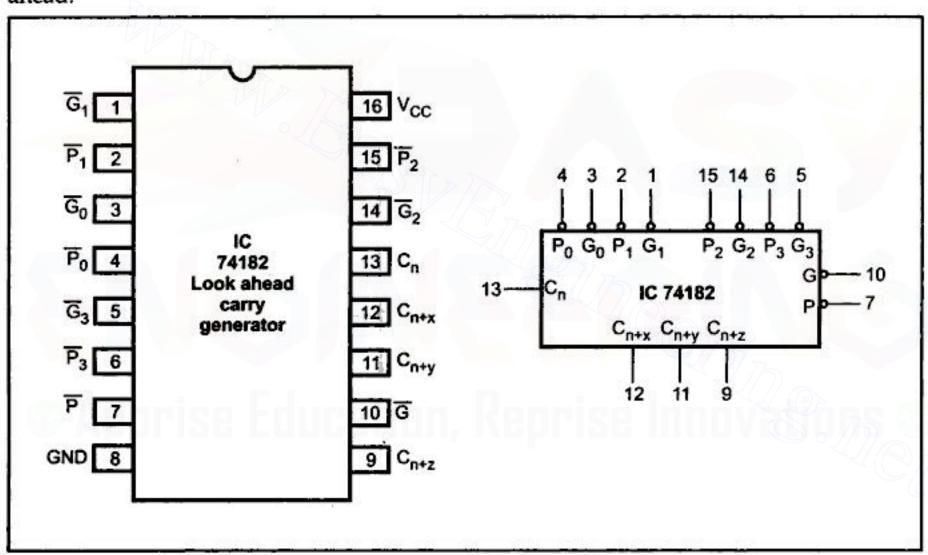

| 7.7                      | Look Ahead Carry Generator (IC 74182)                 | 352 |

| 7.8                      | Binary Parallel Adder (IC 74LS83/74LS283)             | 357 |

| 7.9                      | n-Bit Parallel Subtractor                             | 358 |

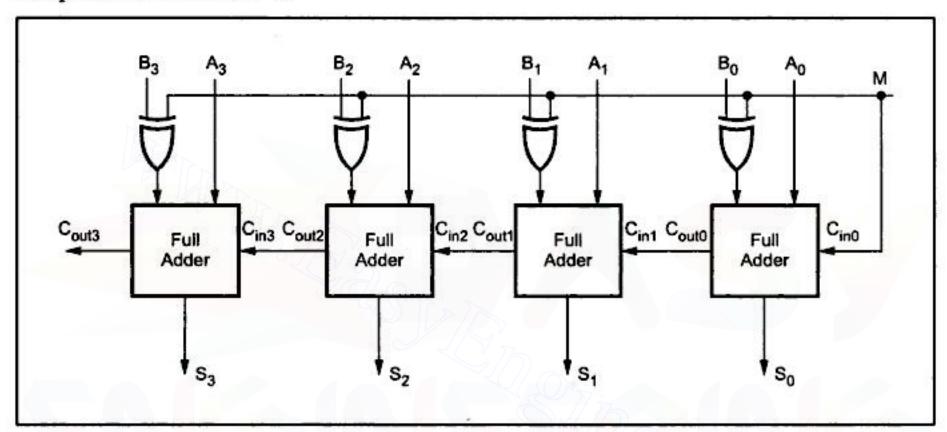

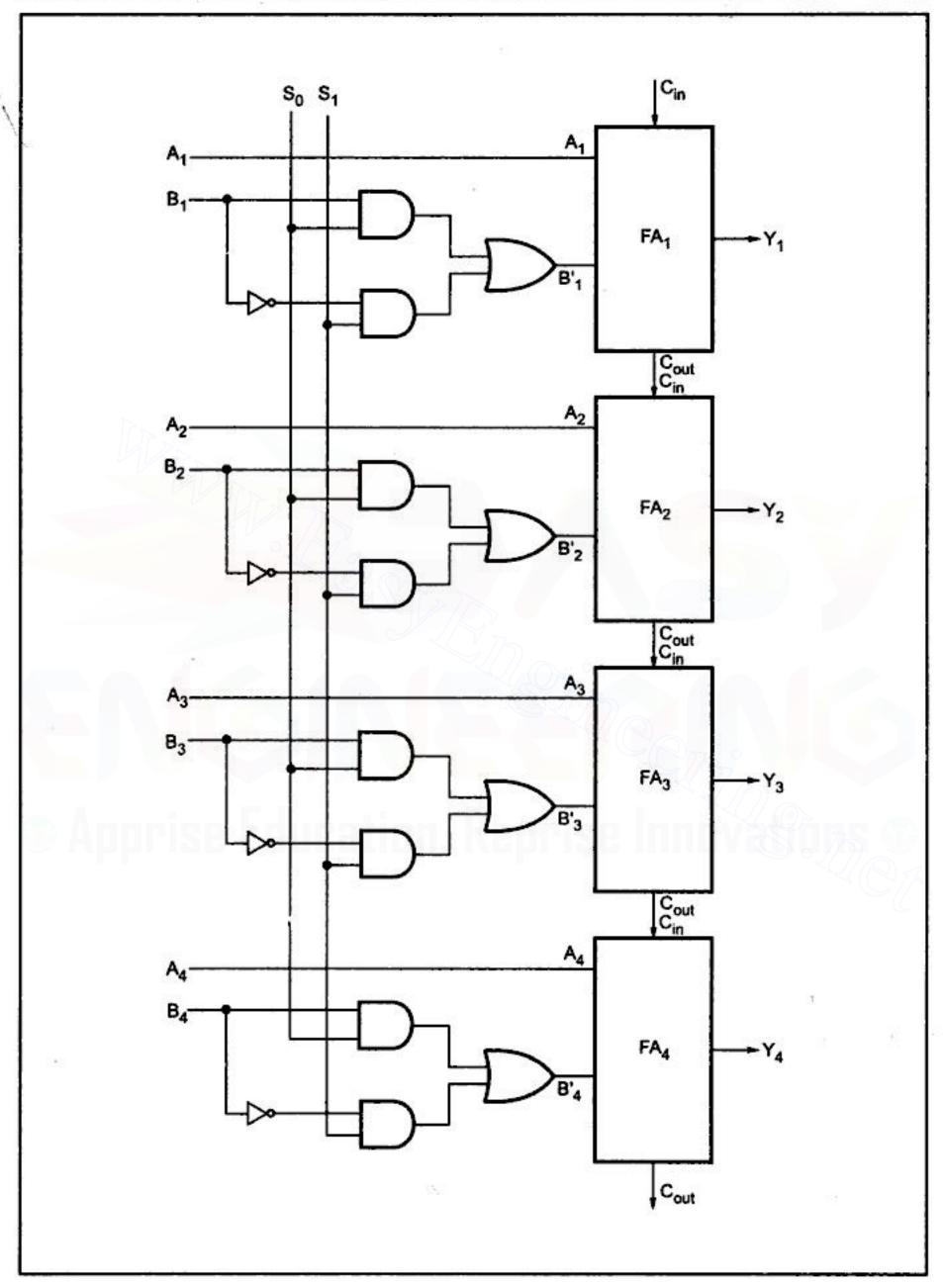

| 7.10                     | Binary Adder-Subtractor                               | 359 |

| 7.11                     | BCD Adder                                             | 359 |

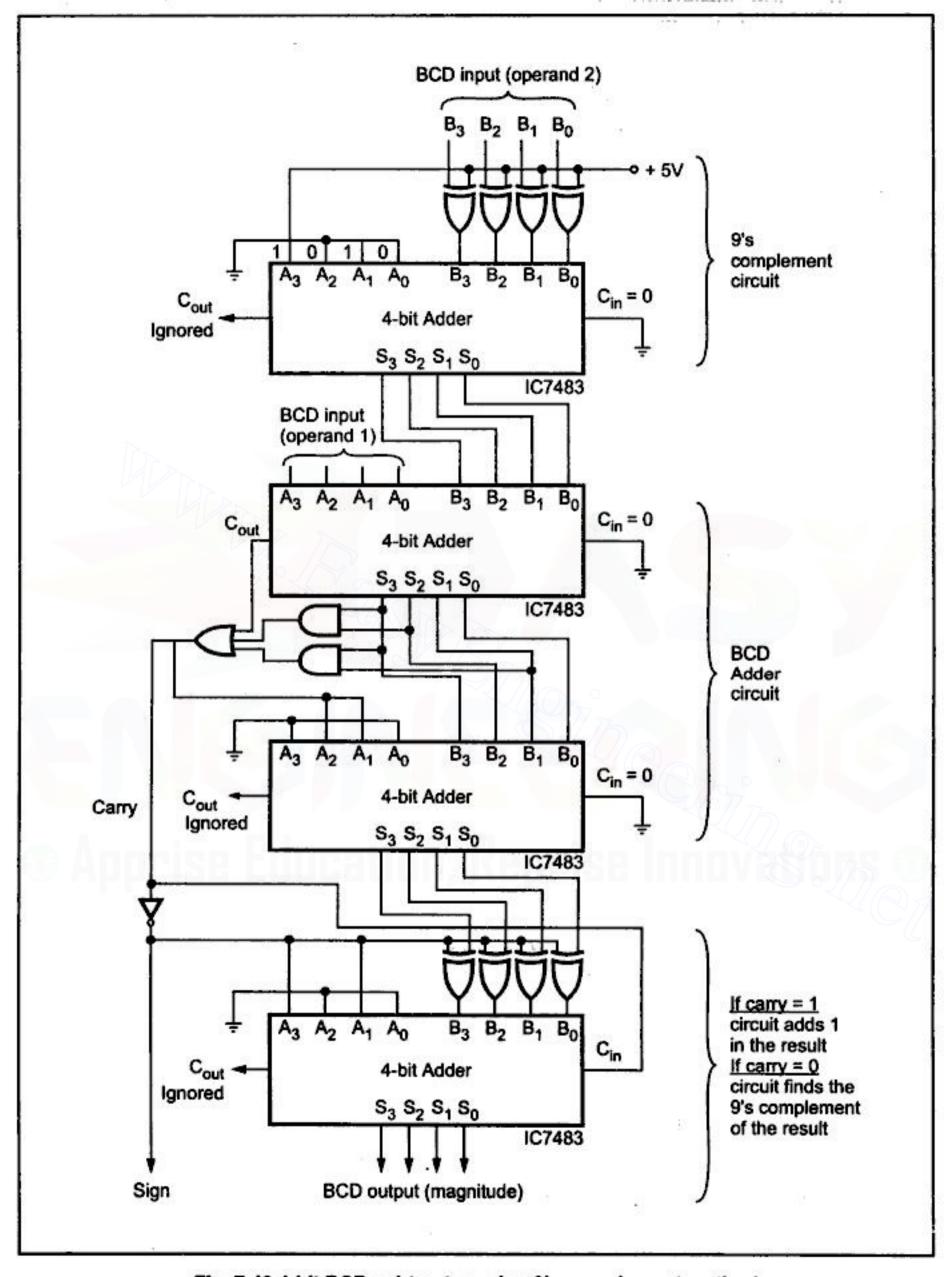

| 7.12                     | BCD Subtractor                                        | 363 |

|                          | 7.12.1 9's Complement                                 | 364 |

|                          | 7.12.2 9's Complement Subtraction                     | 364 |

|                          | 7.12.3 10's Complement Subtraction                    | 365 |

| 7.13                     | Excess-3 Adder                                        | 368 |

| 7.14                     | Excess-3 Subtraction                                  | 369 |

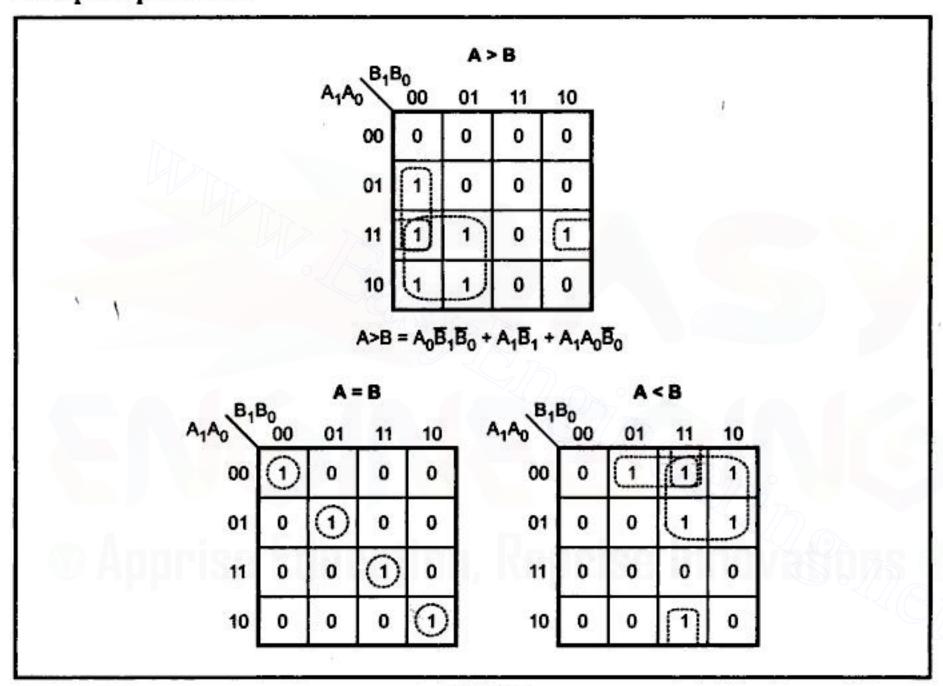

| 7.15                     | Digital Comparator                                    | 371 |

| Univ                     | versity Questions                                     | 378 |

| Chapter 8                | Combinational Logic with MSI and LSI                  | 381 |

| 8.1                      | Introduction                                          | 381 |

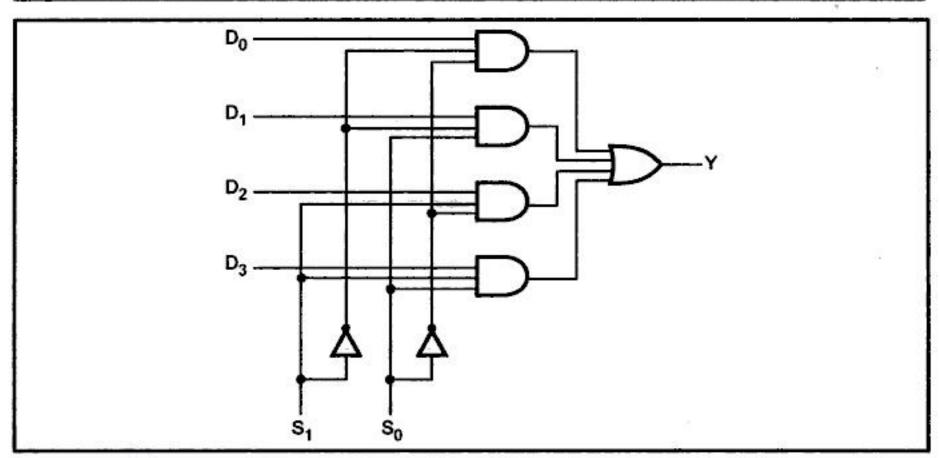

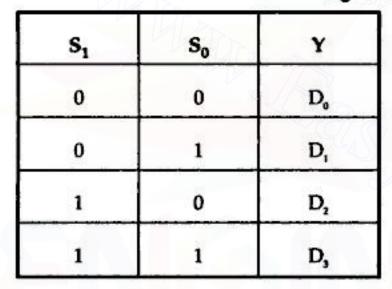

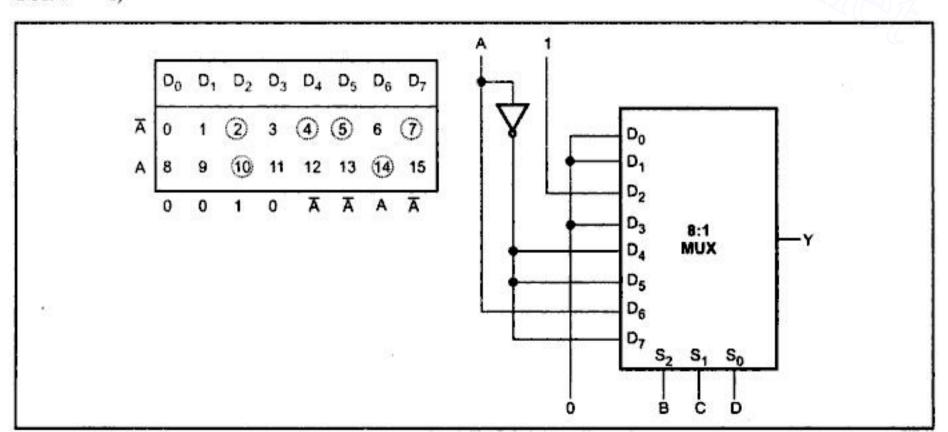

| 8.2                      | Multiplexer                                           | 381 |

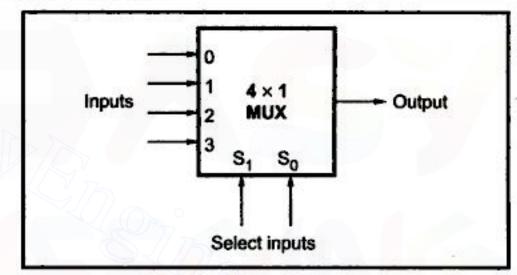

|                          | 8.2.1 Boolean Function Implementation                 | 384 |

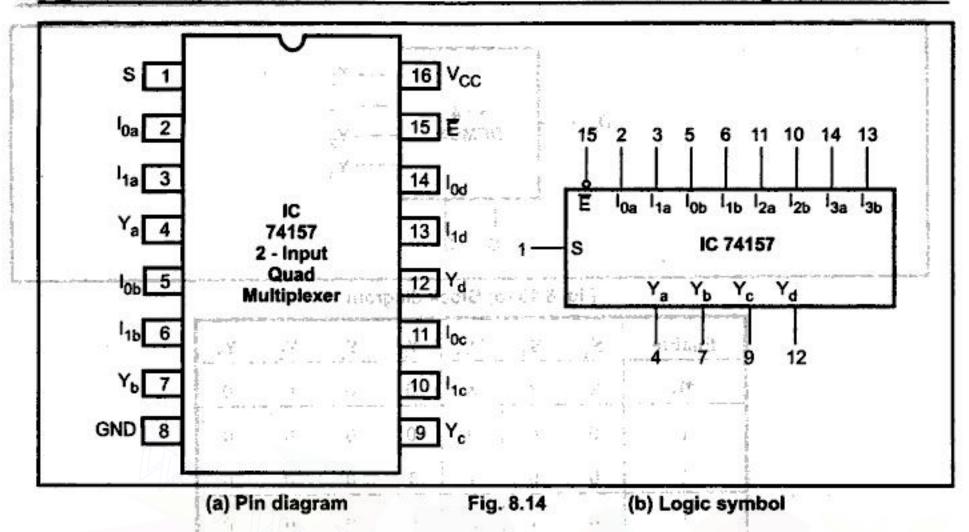

|                          | 8.2.2 Multiplexer ICs                                 | 392 |

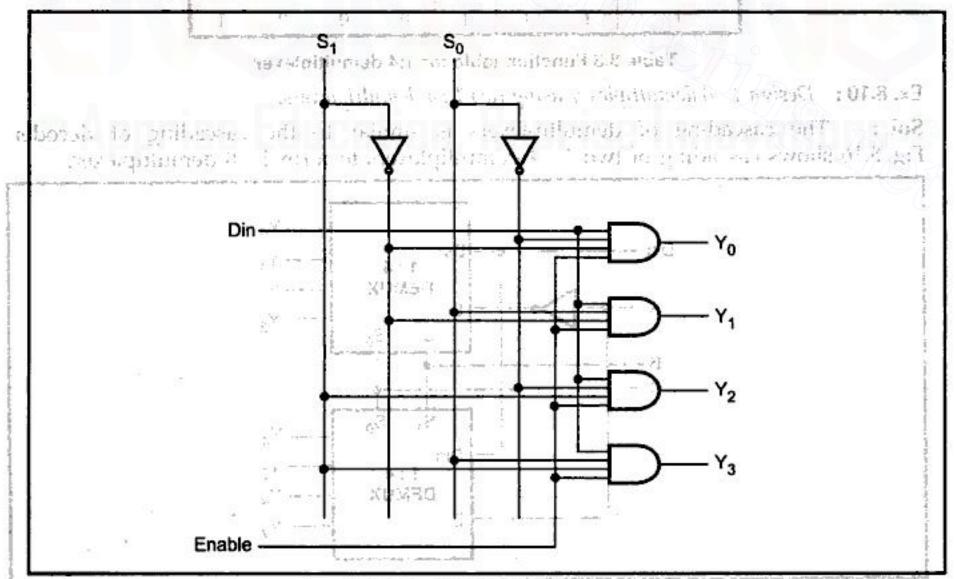

| 8.3                      | Demultiplexer                                         | 393 |

| 8.4                      | Decoders                                              | 396 |

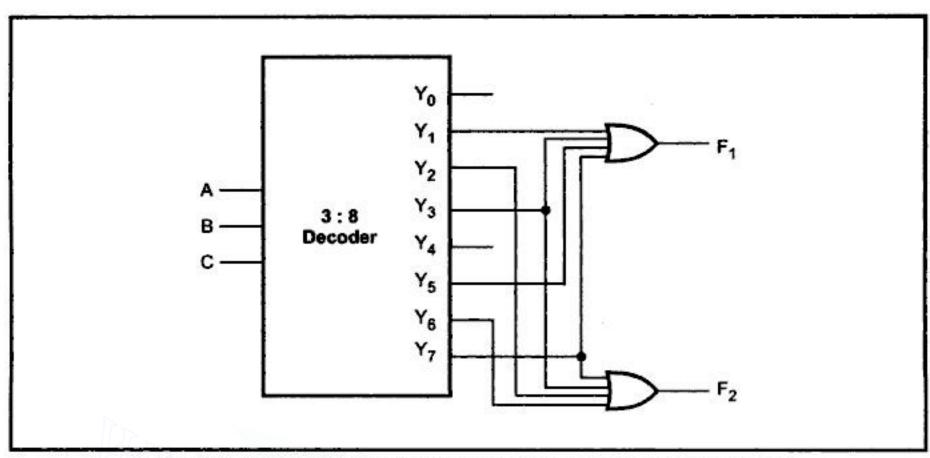

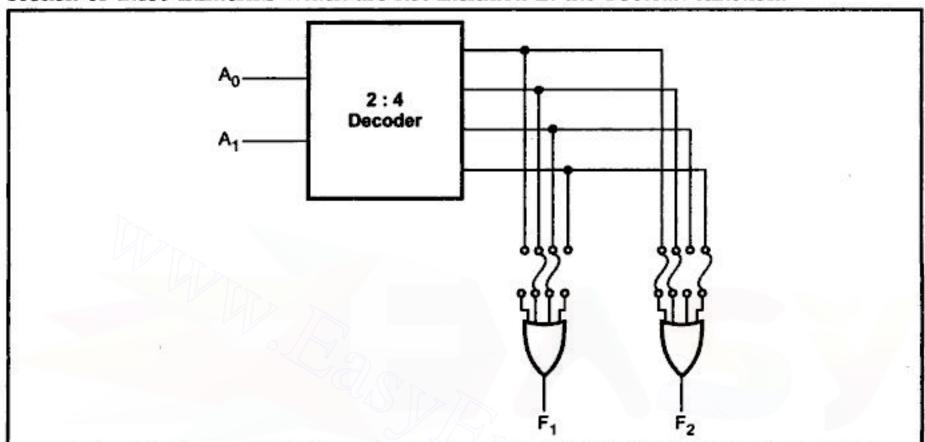

|                          | 8.4.1 Boolean Function Implementation                 | 397 |

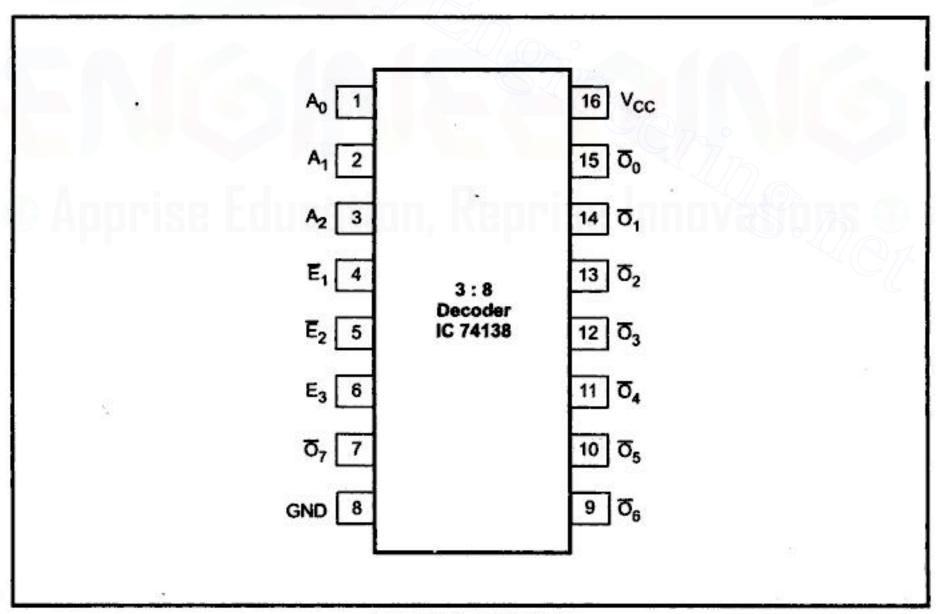

|                          | 8.4.2 Decoder IC 74138                                | 398 |

|                          | 8.4.3 Decoder IC 7442                                 | 401 |

| 8.5                      | Encoder                                               | 401 |

|                          | 8.5.1 Priority Encoder                                | 402 |

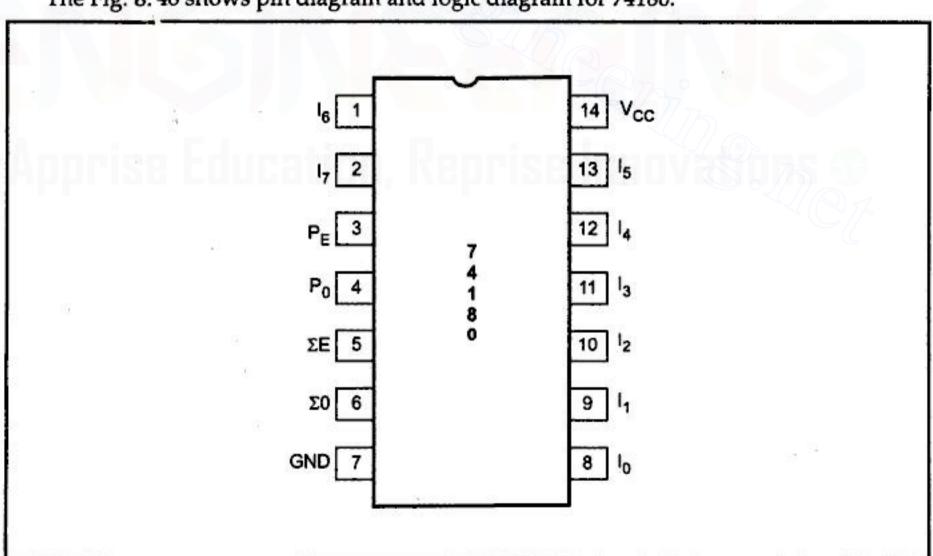

|                          | 8.5.2 Encoder IC ( 74148)                             | 404 |

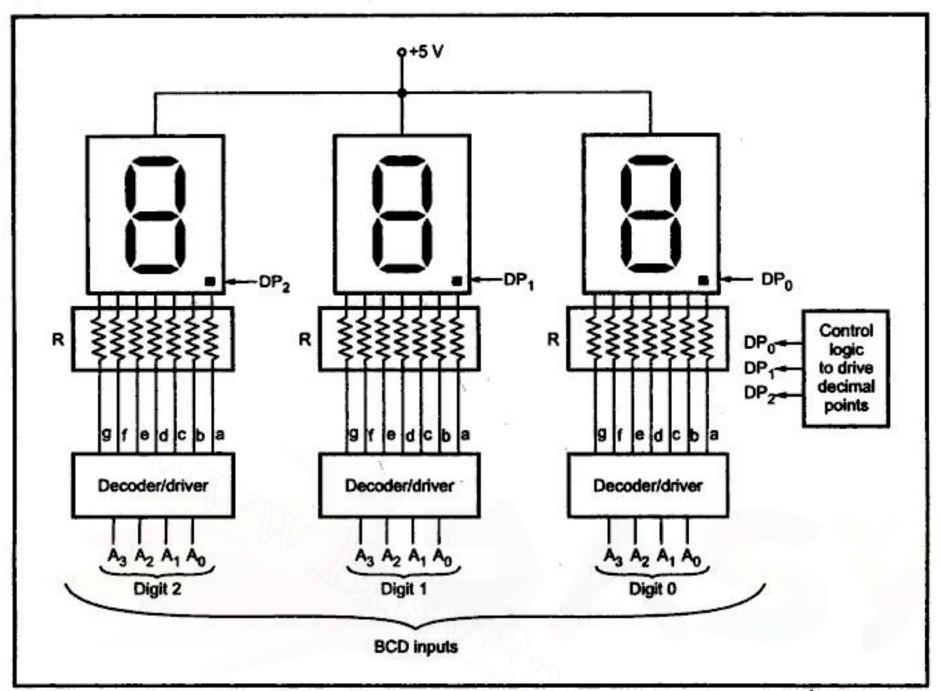

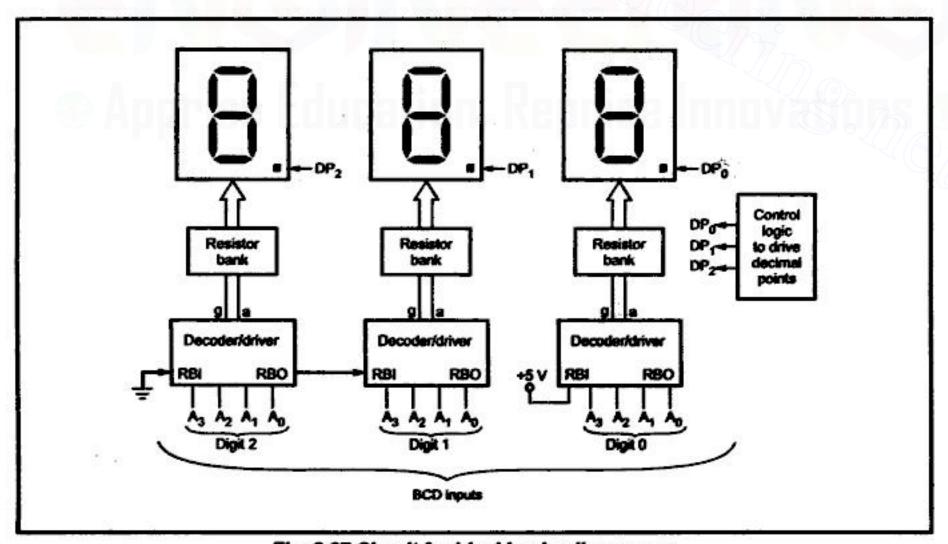

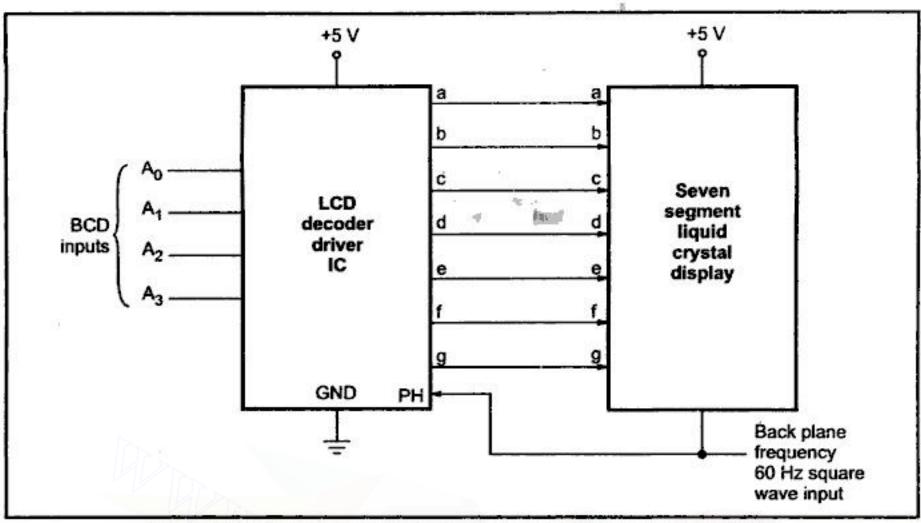

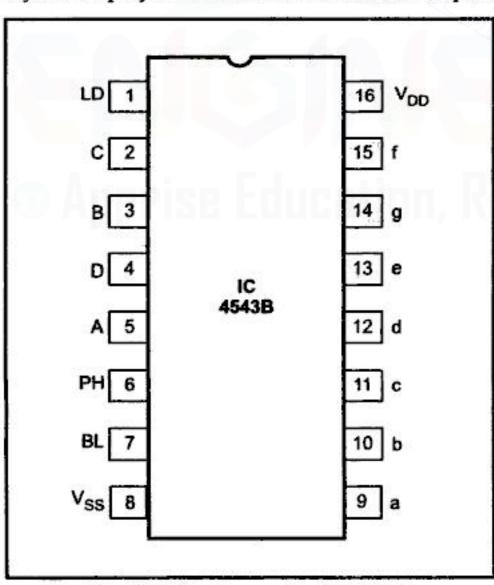

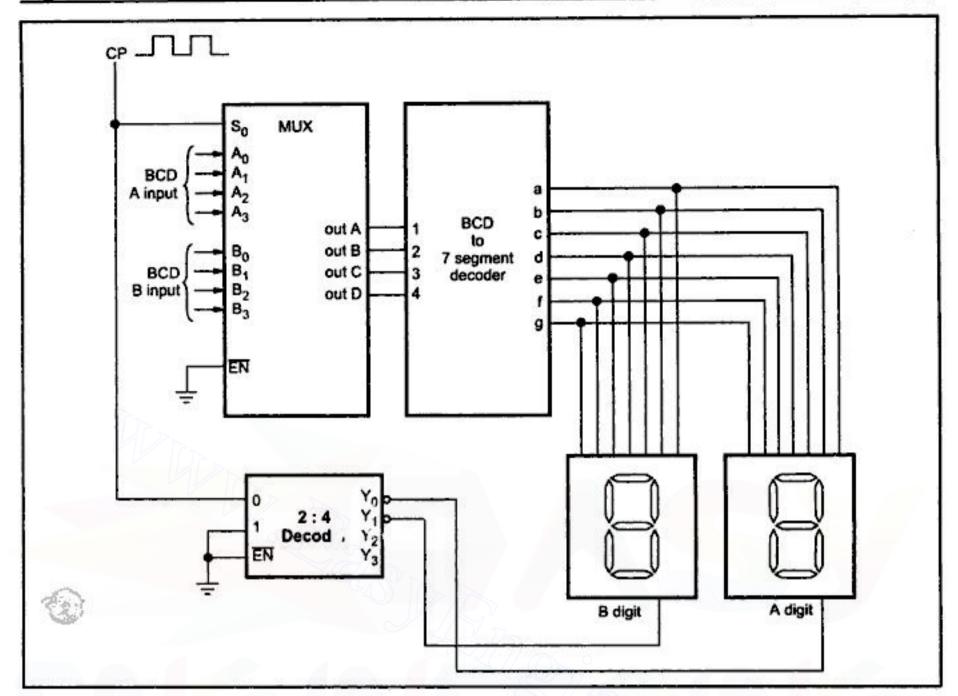

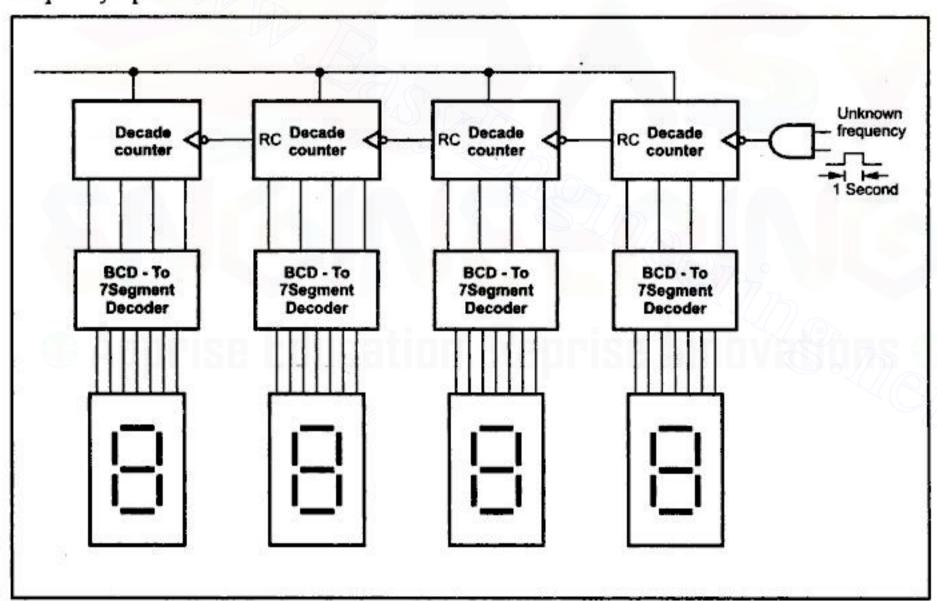

| 8.6                      | BCD-To- 7 Segment Display Decoder/Driver              | 405 |

|                          | 8.6.1 Basic Connection for Driving 7-Segment Displays | 409 |

| 10 <u>0</u> 01 <u>00</u> | 8.6.2 Seven Segment Decoder/Driver for LCD Display    | 416 |

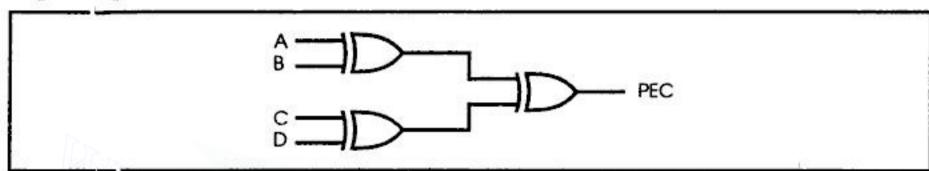

|                          | Parity Generator and Checker                          | 418 |

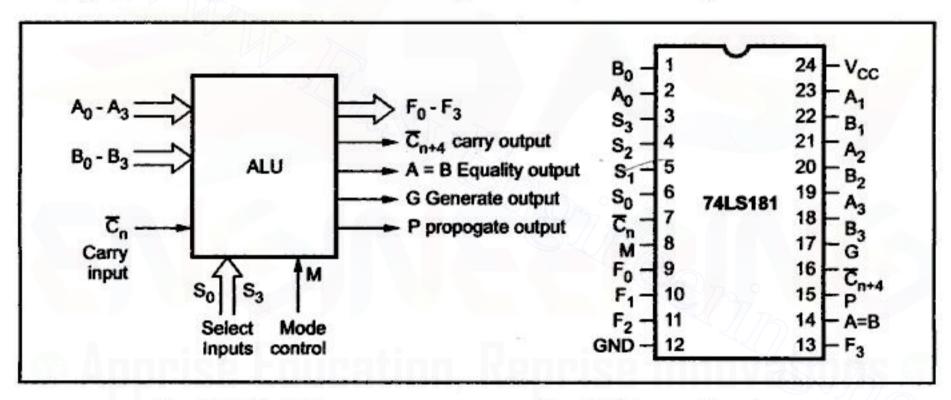

| 8.8                      | Design of ALU                                         | 423 |

| 12                       | 8.8.1 Design of Arithmetic Unit                       | 423 |

|                          | 8.8.2 Design of Logic Unit                            | 426 |

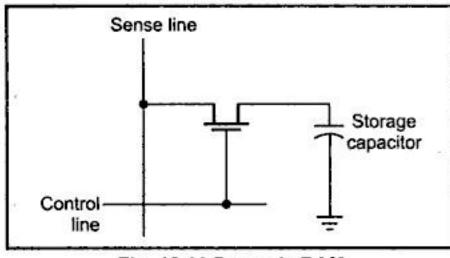

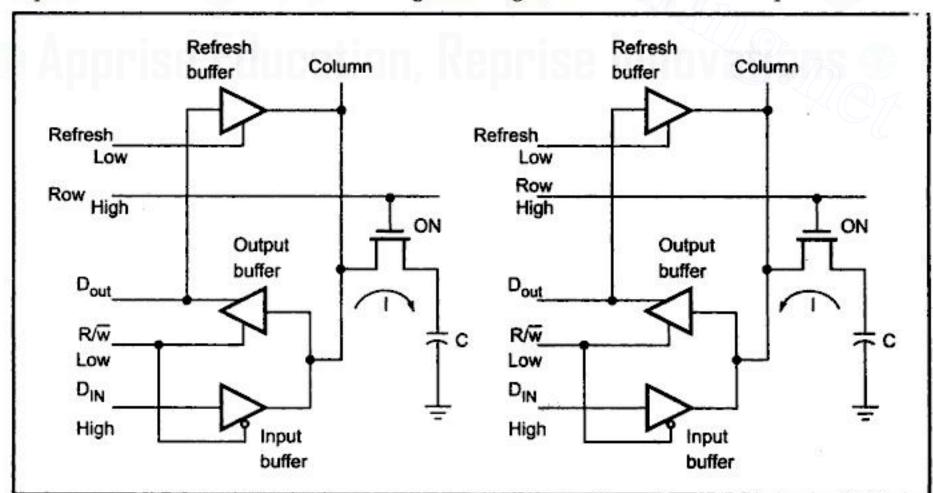

| 12.5.2 Dynamic RAM                                | 689 |

|---------------------------------------------------|-----|

| 12.5.2.1 Write Operation                          | 690 |

| 12.5.2.2 Read Operation                           | 691 |

| 12.5.2.3 Refresh Operation                        | 691 |

| 12.5.3 Comparison Between SRAM and DRAM           | 692 |

| 12.6 Memory Structure and Its Requirements        | 692 |

| 12.7 Standard Memory Chips                        | 693 |

| 12.7.1 Characteristics of Memory :                | 693 |

| 12.7.2 Standard Memory Chips                      | 694 |

| 12.7.3 Memory Cycles                              | 694 |

| 12.8 Typical Memory ICs                           | 697 |

| 12.8.1 IC 2764 (EPROM)                            | 697 |

| 12.8.2 IC 2114 (RAM)                              | 698 |

| 12.9 Expanding Word Size                          | 700 |

| 12.10 Expanding Memory Capacity                   | 700 |

| University Questions                              | 702 |

| Chapter 13 Programmable Logic Devices             | 703 |

| 13.1 Introduction                                 | 703 |

| 13.2 Read Only Memory (ROM)                       | 703 |

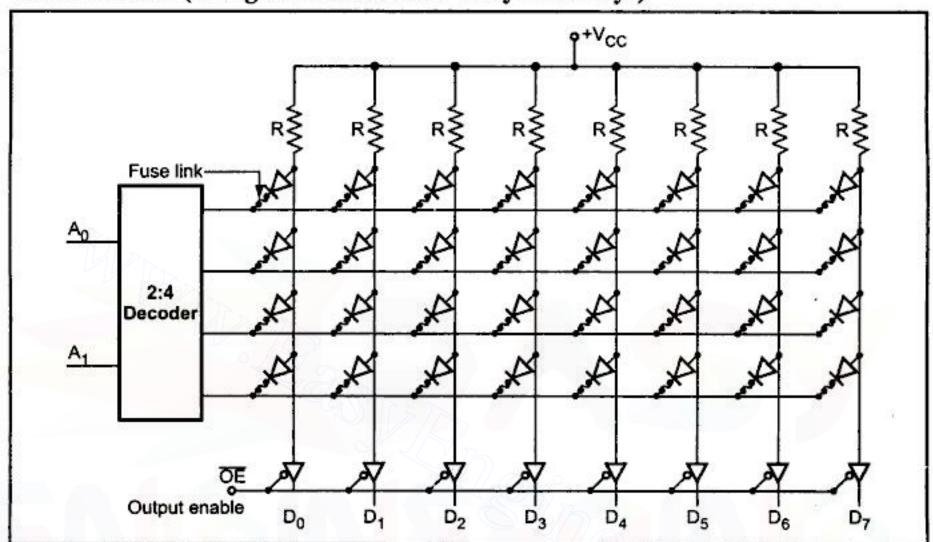

| 13.2.1 Combination Logic Implementation Using ROM | 704 |

| 13.2.2 Types of ROMs                              | 708 |

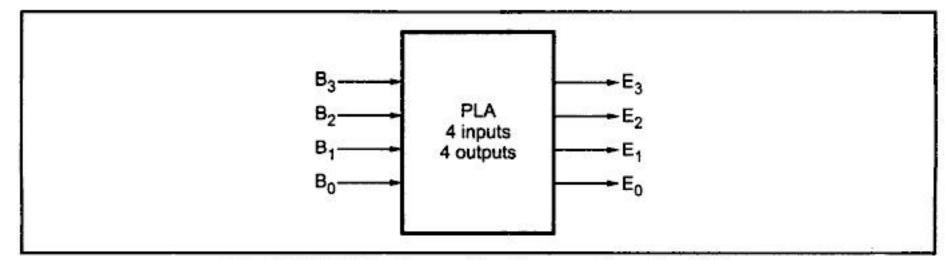

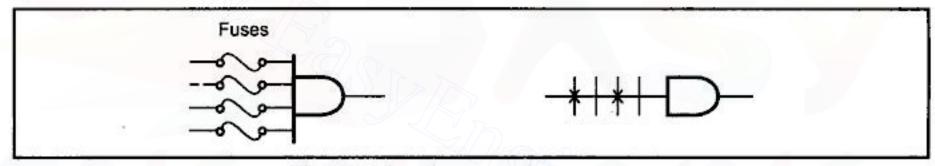

| 13.3 Programmable Logic Array (PLA)               | 708 |

| 13.4 Programmable Array Logic (PAL)               | 714 |

| University Questions                              | 723 |

| Appendix - A Typical Digital ICs                  | 724 |

| References                                        | 728 |

| Index                                             | 729 |

#### **Number Systems**

#### Streamlined method

We can streamline binary to decimal conversion by performing following steps:

- 1. Write the binary number

- Directly under the binary number write 1, 2, 4, 8, 16..., working from right to left.

- If digit is zero, cross out the decimal weight for that position.

- 4. Add the remaining weight to obtain the decimal equivalent of the binary number.

Ex. 1.3: Convert binary number 1010 to its decimal equivalent.

Sol.:

Step 1:1010 (number)

Step 2:8421 (Binary weights)

Step 3:8421

**Step 4**:  $8 + 2 = 10_{10}$

Note:

The subscript 10 identifies this as a decimal number.

#### 1.3.2.1 Double Dabble Method

A popular way to convert binary numbers to decimal numbers is the double dabble method. In this method, the conversion takes place in the following steps:

- 1. Multiply most significant digit (leftmost digit) by 2.

- 2. Add next adjacent digit to the result.

- 3. Multiply result by 2.

- Add next adjacent digit to the result.

- 5. Repeat steps 3 and 4 until all the bits are over.

Ex. 1.4: Convert binary number 10101 to its decimal equivalent.

Sol.:

Step 1:

$$1 \times 2 = 2$$

$$Step 2:2+0 = 2$$

$$Step 3: 2 \times 2 = 4$$

$$Step 4: 4+1 = 5$$

Step

$$3:5\times2=10$$

Step

$$4:10+0=10$$

**Step 3**:

$$10 \times 2 = 20$$

Step 4:

$$20 + 1 = 21_{10}$$

EEEbooks4U

#### **Review Questions**

- Convert 67 to binary using both methods.

- 2. Convert 81310 to binary using both methods and check your answer by converting back to decimal.

#### 1.3.6 Fractional Decimal to Binary Conversion

In case of fractional decimal numbers, numbers are multiplied by 2 and carries are recorded from the integer position. These carries when read downward represent binary equivalent to fractional decimal number. This means that the first carry produced is the MSB and the last carry produced is the LSB.

Ex. 1.11: Convert 0.8125 decimal number to its binary equivalent.

| Sol.: | Fraction | I | Base |   | Resul | t |       |                 | Recorded ( | Carries |

|-------|----------|---|------|---|-------|---|-------|-----------------|------------|---------|

|       | 0.8125   | × | 2    | = | 1.625 | = | 0.625 | with a carry of | 1          | MSB     |

|       | 0.625    | × | 2    | = | 1.25  | = | 0.25  | with a carry of | 1          |         |

|       | 0.25     | × | 2    | = | 0.5   | = | 0.5   | with a carry of | 0          |         |

|       | 0.5      | × | 2    | = | 1.0   | = | 0.0   | with a carry of | 1          | LSB     |

Reading carries downward we get,

binary fraction = 0.1101, which is equivalent to 0.8125 decimal.

Ex. 1.12: Convert 0.95 decimal number to its binary equivalent

| Sol.: | Fraction |   | Base |   | Res | ult |     |                 | Recorded | Carries |

|-------|----------|---|------|---|-----|-----|-----|-----------------|----------|---------|

|       | 0.95     | × | 2    | = | 1.9 | =   | 0.9 | with a carry of | 1        | MSB     |

|       | 0.9      | × | 2    | = | 1.8 | =   | 0.8 | with a carry of | 1        |         |

|       | 0.8      | × | 2    | = | 1.6 | =   | 0.6 | with a carry of | 1        |         |

|       | 0.6      | × | 2    | = | 1.2 | =   | 0.2 | with a carry of | 1        |         |

|       | 0.2      | × | 2    | = | 0.4 | =   | 0.4 | with a carry of | 0        |         |

|       | 0.4      | × | 2    | = | 0.8 | =   | 0.8 | with a carry of | 0        |         |

|       | 0.8      | × | 2    | = | 1.6 | =   | 0.6 | with a carry of | 1        | LSB     |

In this case, 0.8 is repeated and if we multiply further, we will get repeated sequence. If we stop here, we get 7 binary digits, . 1111001. This answer is an approximate answer. To get more accurate answer we have to continue multiplying by 2 until we have as many digits as necessary for our application.

#### **Number Systems**

In case of unsigned 8-bit binary numbers the decimal range is 0 to 255. For signed magnitude 8-bit binary numbers the largest magnitude is reduced from 255 to 127 because we need to represent both positive and negative numbers.

Maximum positive number

$0111\ 11111 = +127$

Maximum negative number

$1111\ 1111 = -128$

#### 1's complement Representation

The 1's complement of a binary number is the number that results when we change all 1's to zeros and the zeros to ones.

Ex. 1.17: Find 1's complement of (1 1 0 1)2

Sol.:

1101 ← number

$0010 \leftarrow 1$ 's complement

Ex. 1.18: Find 1's complement of 1 0 1 1 1 0 0 1

Sol.:

1011 1001 number

0100 0110 1's complement

#### 2's Complement Representation

The 2's complement is the binary number that results when we add 1 to the 1's complement. It is given as

2's complement = 1's complement + 1

The 2's complement form is used to represent negative numbers.

Ex. 1.19: Find 2's complement of (1 0 0 1)<sub>2</sub>

Sol.:

1001 number 0110 1's complement

+ 1

0111 2's complement

Ex. 1.20: Find 2's complement of (1 0 1 0 0 0 1 1)2

Sol.:

1010 0011 number

01011100

1's complement

+ 1

0 1 0 1 1 1 0 1 2's complement

Number Systems

CASE 4: Both negative

Ex. 1.28: Subtract -68 from - 15

Sol.:

$$(-15)$$

$(-15)$

$- \equiv +$

$(-68)$   $68$

2's complement of 15

In 8-bit addition carry after 8th bit is ignored. After addition of 2's complement of 15 (1 1 1 1 0 0 0 1) and 68 we get result (0 0 1 1 0 1 0 1)<sub>2</sub> which is equivalent to decimal 53 and our answer is verified.

#### **Review Questions**

1. Determine the 1's complement of each binary number.

(a) 10011<sub>2</sub>

(b) 111011,

(c) 10001<sub>2</sub>

2. Determine the 2's complement of each binary number.

(a) 100<sub>2</sub>

(b) 10000,

(c) 111001,

3. Perform the following subtraction using the 2's complement method.

(a) 1110112-1010012 (b) 1001112-1000102

#### 1.4 Octal Numbers System

We know that the base of the decimal number system is 10 because it uses the digits 0 to 9, and the base of binary number system is 2 because it uses digits 0 and 1. The octal number system uses first eight digits of decimal number system: 0, 1, 2, 3, 4, 5, 6, and 7. As it uses 8 digits, its base is 8.

When we write an octal number say, 567, it can be represented in power of 8 as

#### Digital Electronics

To obtain the sum of multi-digit octal numbers, the procedure just described is applied to each column of digits as illustrated in the following example.

Ex. 1.38: Add

$$167_8$$

and  $325_8$

Sol.:

$$\begin{array}{ccc}

1 & 1 & \leftarrow \text{Carry} \\

1 & 6 & 7

\end{array}$$

$$\begin{array}{c}

1 & 6 & 7 \\

3 & 2 & 5 \\

\hline

5 & 1 & 4_8

\end{array}$$

If the decimal sum of several octal digits is 16 or greater, subtract 16 and set carry equal to 2. In general, we can express any decimal sum in octal by repeatedly subtracting 8 until the result is one of the octal digits through 0 to 7. Each time 8 is subtracted, the amount of the carry is increased by 1. This procedure is illustrated in the following example.

The better way to perform octal subtraction is to convert the numbers to binary, perform the subtraction, and convert the result back to octal. However, the complement methods already described for binary can also be used. The 7's and 8's complements for octal numbers are found and used like 1's and 2's complements to perform subtraction.

#### Subtraction with 7's complement

The 7's complement of an octal number is found by subtracting each digit from 7, as illustrated in Ex. 1.40.

The steps for octal subtraction using 7's complement method are as given below:

Step 1: Find 7's complement of subtrahend

Step 2: Add two octal numbers (first number and 7's complement of the second number)

Setp 3: If carry is produced in the addition, add carry in the least significant bit of the sum; otherwise find 7's complement of the sum as a result with negative sign.

$$= 3 \times 256 + F(15) \times 16 + D(13) \times 1$$

= 768 + 240 + 13

= 1021<sub>10</sub>

#### 1.5.1 Hexadecimal to Decimal Conversion

The hexadecimal number can be converted into decimal number using following steps.

- Multiply most significant digit (leftmost digit) by 16.

- 2. Add next adjacent digit to the result.

- 3. Multiply result by 16.

- 4. Add next adjacent digit to the result.

- 5. Repeat steps 3 and 4 until all the digits are over.

Example 1.46 :Convert hexadecimal number 7E4H to its decimal equivalent.

Sol.:

**Step 1**:  $7 \times 16 = 112$

**Step 2:** 112 + E (Decimal 14) = 126

**Step 3:**  $126 \times 16 = 2016$

Step 4:  $2016 + 4 = 2020_{10}$

#### 1.5.2 Fractions

In the above section we have considered only hexadecimal integer numbers. In case of hexadecimal fraction numbers, we have to see the weights of digit positions to the right of the decimal point. These are given as 1/16, 1/256, 1/4096 and so on. In power of 16, the weights are 16<sup>-1</sup>, 16<sup>-2</sup>, 16<sup>-3</sup>, 16<sup>-4</sup> and so on. These weights may be written in decimal form as 0.0625, 0.0039 and so on.

Ex. 1.47 Convert hexadecimal number 0.582<sub>H</sub> to its decimal equivalent

Sol.:

$$0.582_H = 5 \times 16^{-1} + 8 \times 16^{-2} + 2 \times 16^{-3}$$

=  $0.3125 + 0.03125 + 4.8828 \times 10^{-4}$

=  $0.34424_{10}$

#### 1.5.3 Mixed Numbers

In general mixed (numbers with an integer and a fractional part) hexadecimal numbers can be represented as

$$N = A_n 16^n + A_{n-1} 16^{n-1} + \dots + A_1 16^1 + A_0 16^0 + A_{-1} 16^{-1} + A_{-2} 16^{-2} + \dots$$

where  $N = \text{Number}$

$$A = \text{Digit}$$

$$n = \text{Digit number}$$

Ex. 1.48: Convert (9 B2.1A) to its decimal equivalent

Sol.:

$$N = 9 \times 16^{2} + B(11) \times 16^{1} + 2 \times 16^{0} + 1 \times 16^{-1} + A(10) \times 16^{-2}$$

$$= 2304 + 176 + 2 + 0.0625 + 0.039$$

$$= 2482.1_{10}$$

#### **Digital Electronics**

28

#### **Number Systems**

Hexadecimal subtraction is best accomplished using the complement method. The 15's and 16's complements for hex numbers are found and used like 1's and 2's complements to perform subtraction.

#### Subtraction with 15's Complement

The 15's complement of a hexadecimal number is found by subtracting each digit from 15, as illustrated in Ex. 1.59.

Ex. 1.59: Find 15's complement of A 9 BH

The steps for hexadecimal subtraction using 15's complement method are as given below:

Step 1: Find 15's complement of subtrahend

Step 2: Add two hexadecimal numbers (first number and 15's complement of the second number.)

Step 3: If carry is produced in the addition, add carry to the least significant bit of the sum; otherwise find 15's complement of the sum as a result with a negative sign.

Ex. 1.60: Use the 15's complement method of subtraction to compute B 0  $2_H$  - 9 8  $F_H$

Sol.: Step 1: 15 15 15

$$-\frac{9 \ 8 \ F}{6 \ 7 \ 0} \leftarrow 15 \text{'s complement}$$

Step 2: B 0 2

$$+\frac{6 \ 7 \ 0}{1 \ 7 \ 2}$$

Step 3: 1 7 2

$$+\frac{1}{1 \ 7 \ 3}$$

∴ B 0 2<sub>H</sub> - 98 F<sub>H</sub> → 173<sub>H</sub>

#### **Digital Electronics**

#### **Solved Examples**

Ex. 1.69: Convert the following binary numbers to Decimal, Hexadecimal and Octal form:

i) (101101.1101)<sub>2</sub>

ii) (11011011.100101)<sub>2</sub>

Sol.:

i) (101101.1101)<sub>2</sub>

**Decimal Conversion**

$$= 2^{5} \times 1 + 0 \times 2^{4} + 1 \times 2^{3} + 1 \times 2^{2} + 0 \times 2^{1}$$

$$+ 1 \times 2^{0} + 1 \times 2^{-1} + 1 \times 2^{-2} + 0 \times 2^{-3} + 1 \times 2^{-4}$$

$$= 32 + 8 + 4 + 1 + \frac{1}{2} + \frac{1}{4} + \frac{1}{16}$$

$$= 45 + 0.5 + 0.25 + 0.0625$$

$$= 45 + 0.8125$$

$$= 45.8125$$

$(101101.1101)_2 = (45.8125)_{10}$

Hex Conversion: 10 1101 . 1101

2 D . D = 2D.DH

Octal Conversion: 101 101 . 110 1

$5 \quad 5 \quad . \quad 6 \quad 4 = 55.64_8$

ii) (11011011.100101)<sub>2</sub>

$$= 1 \times 2^{7} + 1 \times 2^{6} + 0 \times 2^{5} + 1 \times 2^{4} + 1 \times 2^{3}$$

$$+ 0 \times 2^{2} + 1 \times 2^{1} + 1 \times 2^{0} + 1 \times 2^{-1}$$

$$+ 0 \times 2^{-2} + 0 \times 2^{-3} + 1 \times 2^{-4}$$

$$+ 0 \times 2^{-5} + 1 \times 2^{-6}$$

$$= 128 + 64 + 0 + 16 + 8 + 0 + 2 + 1$$

1.

Since we have subtracted larger number from smaller number result is negative and hence it is necessary to take 2's complement of this result.

Since final carry is zero, so the answer is negative and in 2's complement form.

$$\therefore (1\ 0\ 0\ 0\ 1\ 0\ 0)_2 - (1\ 0\ 1\ 0\ 1)_2 = (0\ 0\ 1\ 0\ 0\ 0)_2$$

Ex. 1.82: Perform the following operation

$$(737)_8 - (123)_{16} + (100)_{10}$$

Write the answer in hexadecimal form

(Dec-99)

EEEbooks4U

**Sol.**:

$$(737)_8 = (111011 \ 11)_2 = (1 \ D \ F)_{16}$$

$$(100)_{10} = 64_{\rm H}$$

Now

$$(737)_8 - (123)_{16} + (100)_{10} = 120_H$$

Ex. 1.83: Convert the following decimal numbers to binary

i) (12.0625)<sub>10</sub>

(Dec-99)

$$0.0625 \times 2 = 0.125 \quad 0$$

$0.125 \times 2 = 0.25 \quad 0$

$0.25 \times 2 = 0.5 \quad 0$

$0.5 \times 2 = 0 \quad 1$

$(12.0625)_{10} = (1 \ 1 \ 0 \ 0 \ 0 \ 0 \ 0 \ 1)_2$

Ans.: i) 10000000 (in 2's complement form), ii) 100000001

8. Solve the following

i)

$$A5_H + 2C_H = ()_{10}$$

ii)  $1101 \times 1001 = ...$

(Dec-92)

Ans. : i) 209, ii) 111 01 01

9. Determine 2's complement of

(Dec-92)

i) 8F<sub>H</sub> ii) FF<sub>H</sub>

Ans. : i) 1000 0001, ii) 0000 0001

10. Determine decimal equivalent of the following in sign magnitude form

(Dec-92)

i) 8D<sub>H</sub> ii) FF<sub>H</sub>

Ans. : i) - 13, ii) - 127

11. i) Add the hexadecimal numbers:

FE1 + CA9

ii) Perform the subtraction of hexadecimal numbers

(May-93)

FA7 – 1 FD

Ans.: i) 1C 8A, ii) DAA

12. Carry out the following:

i) Convert (11001011.01110)2 into decimal

- ii) Convert decimal number (61.3) to binary (upto 5 bit binary)

- iii) Convert octal number 574 to binary and decimal.

iv) Convert hex number A92 to octal.

(May-93)

Ans.: (203.4375)<sub>10</sub>, ii) (111101.010011001)<sub>2</sub>, iii) (101 111 100)<sub>2</sub>, 380 iv) (5222)<sub>8</sub>

13. Determine 2's complement of

(May-93) Ans.: i) 89<sub>H</sub>, ii) 02<sub>H</sub>)

14. Carry out the following

i) 77<sub>H</sub>, ii) FE<sub>H</sub>

(May-93)

$$(756)_8 + (125)_8 - (176)_8 = (...?...)_8$$

Ans.: (705)8

15. Convert the following numbers to hexadecimal.

(Dec-93)

Ans.: i) (0 F 5)<sub>16</sub>, ii) (16.9)<sub>16</sub>, iii) (1 B.D)<sub>16</sub> iv) (2.8)<sub>16</sub>

16. Carry out the following arithmetic operations and represent result in the same format.

(Dec-93)

Ans.: i) (402)<sub>8</sub>, ii) (62 D8)<sub>16</sub>

17. Using 2's complement perform the following:

$$i)$$

$(42)_{10} - (68)_{10}$   $ii)$   $(25) - (16)_{10}$

(Dec-93)

What are the advantages of using 2's complement method over 1's complement Ans. : (-26)10, ii) (9)10

18. Solve the following.

i) 1101.01 × 100.1 ii) 111110.1 + 0101

(Dec-93)

Ans.: i) 1110111.01, ii) 1100.1

#### Digital Electronics

#### 48

#### Number Systems

64. Perform the following subtraction using 1's complement method:

(0011.1001) - (0001.1110)

(May-2000)

65. (a) Perform the following:

(i) Convert to binary:  $(19.75)_{10} = (19.75)_{10} = (19.75)_{10} = (19.75)_{10} = (19.75)_{10} = (19.75)_{10} = (19.75)_{10} = (19.75)_{10} = (19.75)_{10} = (19.75)_{10} = (19.75)_{10} = (19.75)_{10} = (19.75)_{10} = (19.75)_{10} = (19.75)_{10} = (19.75)_{10} = (19.75)_{10} = (19.75)_{10} = (19.75)_{10} = (19.75)_{10} = (19.75)_{10} = (19.75)_{10} = (19.75)_{10} = (19.75)_{10} = (19.75)_{10} = (19.75)_{10} = (19.75)_{10} = (19.75)_{10} = (19.75)_{10} = (19.75)_{10} = (19.75)_{10} = (19.75)_{10} = (19.75)_{10} = (19.75)_{10} = (19.75)_{10} = (19.75)_{10} = (19.75)_{10} = (19.75)_{10} = (19.75)_{10} = (19.75)_{10} = (19.75)_{10} = (19.75)_{10} = (19.75)_{10} = (19.75)_{10} = (19.75)_{10} = (19.75)_{10} = (19.75)_{10} = (19.75)_{10} = (19.75)_{10} = (19.75)_{10} = (19.75)_{10} = (19.75)_{10} = (19.75)_{10} = (19.75)_{10} = (19.75)_{10} = (19.75)_{10} = (19.75)_{10} = (19.75)_{10} = (19.75)_{10} = (19.75)_{10} = (19.75)_{10} = (19.75)_{10} = (19.75)_{10} = (19.75)_{10} = (19.75)_{10} = (19.75)_{10} = (19.75)_{10} = (19.75)_{10} = (19.75)_{10} = (19.75)_{10} = (19.75)_{10} = (19.75)_{10} = (19.75)_{10} = (19.75)_{10} = (19.75)_{10} = (19.75)_{10} = (19.75)_{10} = (19.75)_{10} = (19.75)_{10} = (19.75)_{10} = (19.75)_{10} = (19.75)_{10} = (19.75)_{10} = (19.75)_{10} = (19.75)_{10} = (19.75)_{10} = (19.75)_{10} = (19.75)_{10} = (19.75)_{10} = (19.75)_{10} = (19.75)_{10} = (19.75)_{10} = (19.75)_{10} = (19.75)_{10} = (19.75)_{10} = (19.75)_{10} = (19.75)_{10} = (19.75)_{10} = (19.75)_{10} = (19.75)_{10} = (19.75)_{10} = (19.75)_{10} = (19.75)_{10} = (19.75)_{10} = (19.75)_{10} = (19.75)_{10} = (19.75)_{10} = (19.75)_{10} = (19.75)_{10} = (19.75)_{10} = (19.75)_{10} = (19.75)_{10} = (19.75)_{10} = (19.75)_{10} = (19.75)_{10} = (19.75)_{10} = (19.75)_{10} = (19.75)_{10} = (19.75)_{10} = (19.75)_{10} = (19.75)_{10} = (19.75)_{10} = (19.75)_{10} = (19.75)_{10} = (19.75)_{10} = (19.75)_{10} = (19.75)_{10} = (19.75)_{10} = (19.75)_{10} = (19.75)_{10} = (19.75)_{10} = (19.75)_{10} = (19.75)_{10} = (19.75)_{10} = (19.75)_{10$

(ii) Convert to decimal:  $(F4D2)_{16} = ($

(Dec-2000, May-2002)

66. Performing the following:  $(5531)_8 - (3261)_8 + (100)_{10}$

Write the answer in hexadecimal form.

(Dec-2000, May-2002)

67. Convert the following numbers from the given base to other three bases indicated:

1) Decimal 52.45 to binary, octal and hex.

Ans.: (64.3463), (110100.011100110011), (34.733),

Hexadecimal 2AC5 to binary, octal and decimal.

Ans.: (0010101011000101), (25305), (10949),

(May-2001)

68. Perform the following subtraction using 1s complement and 2s complement method 45 + (-17)

Give the result in sign-magnitude form.

(May-2001)

69. Determine the values of base x if :

(Dec-2001)

$(i)(211)_x = (152)_8$

(ii) (193), = (623),

Ans. : i) x = 7 ii) x = 16

70. Using 2's complement method, perform:

$$(i) (156)_{10} - (99)_{10} \quad (ii) (16)_{10} - (25)_{10}$$

(Dec-2001)

71. Carry out the following conversions: (268.75), into binary, octal and hexadecimal.

Ans.: (100001100.11)2, (414.6)8, (10C.C)16

(Dec-2001)

72. Determine the base  $x : (211)_x = (152)_8$

(May-2002)

73. What do you mean by sign magnitude form of representation?

(May-2002)

74. Convert the following numbers into decimal:

i) 100100111000.0111 (BCD), ii) 11001101.1112, iii) CF.516, iv) 2345.

(Dec.-2002)

75. Write sign-magnitude, 1's complement and 2's complement forms for the following decimal numbers:

i) + 9.5 ii) - 17.0

(May-2003)

76. Perform the indicated operations: i)  $(FDC)_{16}$ :  $(A29)_{16}$  ii)  $(241)_8$  –  $(176)_8$

(May-2003)

77. Perform the following subtractions using 2's complement method:

i) 0011.1001 - 0001.1110 ii)  $(3F)_{16} - (5C)_{16}$  (Dec.-2003)

78. Give 4-bit sign-magnitude, 1's complement and 2's complement representation of a number in a tabular (Dec.-2003) form.

000

EEEbooks4U

#### 2.3.1 BCD Addition

The addition of two BCD numbers can be best understood by considering the three cases that occur when two BCD digits are added.

#### Sum equals 9 or less with carry 0

Let us consider additions of 3 and 6 in BCD.

The addition is carried out as in normal binary addition and the sum is 1 0 0 1, which is BCD code for 9.

#### Sum greater than 9 with carry 0

Let us consider addition of 6 and 8 in BCD

The sum 1 1 1 0 is an invalid BCD number. This has occurred because the sum of the two digits exceeds 9. Whenever this occurs the sum has to be corrected by the addition of six (0110) in the invalid BCD number, as shown below

After addition of 6 carry is produced into the second decimal position.

#### Sum equals 9 or less with carry 1

Let us consider addition of 8 and 9 in BCD

In this, case, result (0001 0001) is valid BCD number, but it is incorrect. To get the correct BCD result correction factor of 6 has to be added to the least significant digit sum, as shown.

From the above examples we can summarize steps for 9's complement BCD subtraction as follows:

- Find the 9's complement of a negative number

- Add two numbers using BCD addition

- If carry is generated add carry to the result otherwise find the 9's complement of the result.

Ex. 2.2: Perform each of the following decimal subtractions in 8-4-2-1 BCD using 9's complement method.

#### **Digital Electronics**

60

#### **Binary Codes**

#### Ex. 2.4: → Excess-3 for 8 a) 1011 → Excess-3 for 6 1001 1 0100 0011 0011 Add 3 → Excess-3 for 14 0100 0111 (1) (4) b) $0 \ 1 \ 0 \ 0 \rightarrow Excess-3$ for 1 → Excess-3 for 2 + 0101 1001 Sub 3 0011

#### 2.5.2 Excess-3 Subtraction

To perform Excess-3 subtraction we have to

- · Complement the subtrahend

- · Add complemented subtrahend to minuend

- If carry = 1 Result is positive. Add 3 and end around carry

If carry = 0 Result is negative. Subtract 3.

1 0 1 1 → Excess-3 for 8 + 0 1 1 1 → Complement of 5 in Excess-3

$0110 \rightarrow Excess-3$  for 3

$0\ 1\ 1\ 0 \rightarrow Excess-3$  for 3

b) 5-8

1 0 0 0 → Excess-3 for 5 + 0 1 0 0 → Complement of 8 in Excess-3

1 1 0 0 - 0 0 1 1

$1001 \rightarrow \text{Excess-3 for} - 3$

180° error in the disk position. Since it is physically impossible to have all the brushes precisely aligned, some error will always be present at the edges of the sectors.

If we use gray code to represent disk position then error due to improper brush alignment can be reduced. This is because the gray code assures that only one bit will change each time the decimal number is incremented. So in 3-bit code, error may occur due to one bit position. Other two bits positions of two adjacent sectors are always same and hence there is no possibility of error. Therefore in 3-bit code probability of error is reduced upto 66%. In case of 4-bit code it is reduced upto 75%.

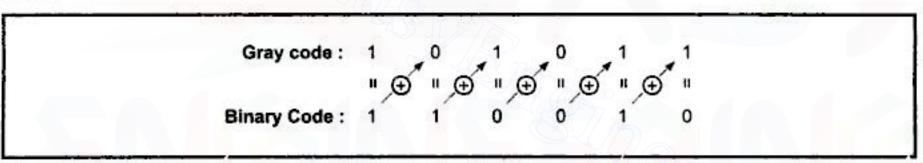

#### 2.6.2 Gray-to-Binary Conversion

The gray to binary code conversion can be achieved using following steps.

- The most significant bit of the binary number is the same as the most significant bit of the gray code number. So write it down.

- To obtain the next binary digit, perform an exclusive-OR-operation between the bit just written down and the next gray code bit. Write down the result.

- Repeat step 2 until all gray code bits have been exclusive-ORed with binary digits. The sequence of bits that have been written down is the binary equivalent of the gray-code number.

Ex. 2.8: Convert gray code 101011 into its binary equivalent.

Sol. :

Fig. 2.3

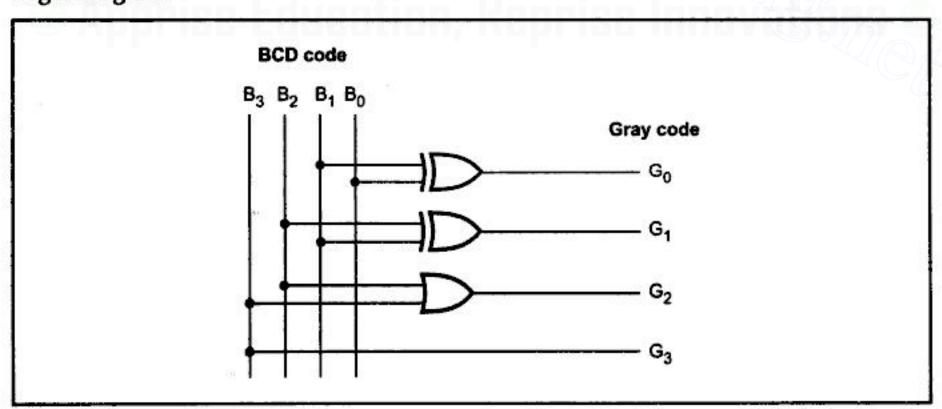

#### 2.6.3 Binary to Gray Conversion

Let us represent binary number as

B<sub>1</sub> B<sub>2</sub> B<sub>3</sub> B<sub>4</sub> ... B<sub>n</sub> and its equivalent gray code as

With this representation gray code bits are obtained from the binary bits as follows:

$$G_1 = B_1$$

$$G_2 = B_1 \oplus B_2$$

$$G_3 = B_2 \oplus B_3$$

$$G_4 = B_3 \oplus B_4$$

$$\vdots$$

$$G_n = B_{n-1} \oplus B_n$$

**Binary Codes**

| 1010 |     | CC  | SM  | ⊄ | !  |   |   |      |   | 1 |

|------|-----|-----|-----|---|----|---|---|------|---|---|

| 1011 |     |     |     |   | \$ | , | # |      | Ш |   |

| 1100 |     |     |     | < | ٠  | % | æ | <br> | Ш | 1 |

| 1101 |     |     |     | ( | )  | _ | , |      |   |   |

| 1110 |     |     |     | + | ;  | > | = |      |   |   |

| 1111 | CU1 | CU2 | CU3 | 1 |    | ? | " |      |   |   |

68

Table 2.9 Partial EBCDIC table

#### Definitions of control abbreviations :

Digital Electronics

| BS  | Backspace           | LC  | Lowercase   | meanings of unfamiliar symbols: |

|-----|---------------------|-----|-------------|---------------------------------|

| BYP | Bypass              | LF  | Line feed   | Vertical bar : logical OR       |

| CC  | Cursor control      | NL  | New line    | - Logical NOT                   |

| CUI | Customer use        | PF  | Punch off   | - Hypen or minus sign           |

| CU2 | Customer use        | PN  | Punch on    | - Underscore (01101101)         |

| CU3 | Customer use        | PRE | Prefix      | Example of code format:         |

| DL  | Delete              | RES | Restore     | 01234567 Bit positions          |

| DS  | Digit select        | RS  | Reader stop | 11000110 is F                   |

| EOB | End of block        | SM  | Set Mode    |                                 |

| EOT | End of transmission | SP  | Space       |                                 |

| FS  | Field separator     | TM  | Tape mark   |                                 |

| HT  | Horizontal tab      | UC  | Uppercase   |                                 |

| IL  | Idle                |     |             |                                 |

#### 2.8.3 Hollerith Code

Herman Hollerith developed a way to feed information into the digital computer using punched cards. The code used in the system to represent alphanumeric information is known as Hollerith code. A Hollerith card consists of 80 columns and 12 rows as shown in the Fig. 2.5. Each column represents an alphanumeric character with holes in the appropriate rows. A hole is sensed as a 1 and the absence of a hole is sensed as a 0 by the circuit in the card reader. The 12 rows are marked starting from the top as 12, 11, 0, 1, 2, 3, 4., 5, 6, 7, 8 and 9. Each row is a 1-bit information. Thus the Hollerith code is 12-bit code. The first three rows of the card are called the zone punch rows and remaining nine row are called the numeric punch rows. The numbers are represented in the column by a single punch. For example, punch on 5 represents number 5. The alphabets are represented using two punches. A letter A is a 12-1 punch, i.e. punch in row 1 and row 12. For example,

$$B = 12 - 2$$

,  $C = 12 - 3...$ ,  $I = 12 - 9$ ,  $J = 11 - 1$ ,  $K = 11 - 2$ , ...,  $R = 11 - 9$ .

*i*)

$$(65)_{10} + (58)_{10}$$

*ii*)  $(113)_{10} + (101)_{10}$

#### Sol. :

Ex. 2.5: Convert each of the following decimal numbers to excess-3 code i) (18)10 ii) (56)10

**Sol.**: i)

$$18_{10} = 0100$$

1011 in excess-3

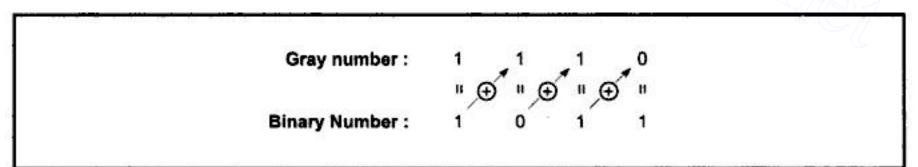

Ex. 2.6: Convert gray number 1110 to its BCD equivalent.

$56_{10} = 1000 \quad 1001 \text{ in excess-3}$

Sol. :

Fig. 2.8

$$11_{10} = 0001 \ 0001 \ \text{in BCD}$$

$$11_{10} = 0001 \ 0001 \ \text{in BCD}$$

$$1110 \ \text{in gray} = 0001 \ 0001 \ \text{in BCD}$$

(Dec-2000)

46. What do you mean by ASCII codes? Give one application.

(Dec-2000)

47. With suitable examples explain weighted and non-weighted codes.

(May-2001)

48. What are excess-3 and gray code? Express decimal 1 to 9 in gray code, excess-3 code and 8221 code.

(Dec-2001)

49. What do you mean by self complementing code? Write two self complementing codes. (May-2002)

50. Represent the following decimal numbers in each of the given codes using 12-bit notation:

i) 491 ii) 27

Codes: i) 8421 ii) 5421 iii) 2421

(May-2003)

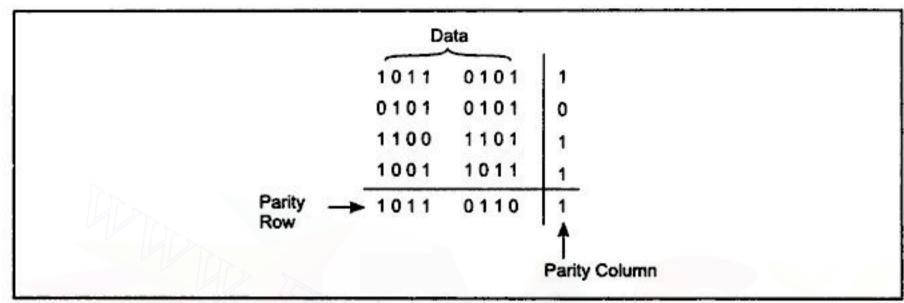

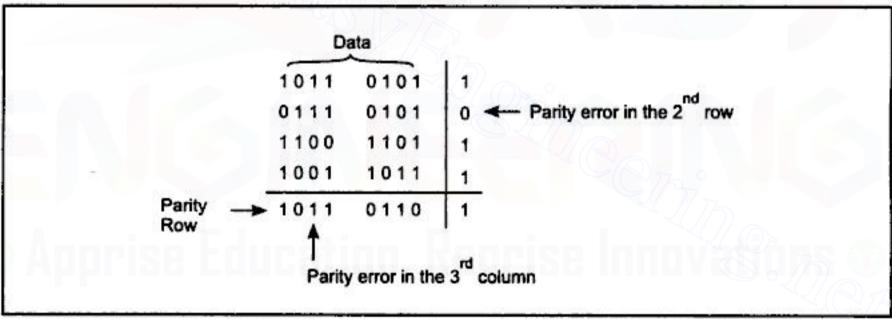

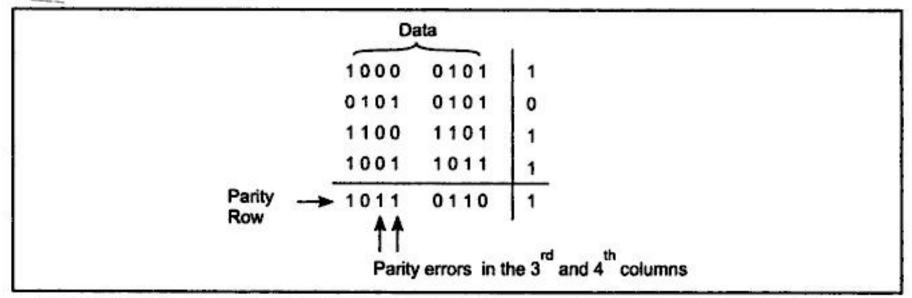

#### 3.4 Block Parity

When several binary words are transmitted or received in succession, the resulting collection of bits can be regarded as a block of data, having rows and columns. For example, four eight bit words in succession form an 4 × 8 block. Parity bits can then be assigned to both rows and columns, as shown in Fig. 3.1 (a). This scheme is known as block parity. It makes it possible to correct any single error occurring in a data word and to detect any two errors in a word. Let us see how we can do this.

Fig. 3.1 (a) Adding even parity bits to the rows and columns of a 4 × 8 data block

Fig. 3.1 (b) Parity errors in the third column and second row mean that the third bit in the second word is in error, so it can be corrected.

Fig. 3.1 (c) Parity errors in two columns mean that two errors have occurred in one data word

#### **Error Detecting & Correcting Codes**

Sol.: Here n = 6 and k = 3. Therefore message code is 3 bit having eight combinations (000 - 111). As n = 6, check bits are n - k = 3.

#### Code for message 0 0 0:

We know that,

$$C = DG$$

$$= \begin{bmatrix} 000 \end{bmatrix} \begin{bmatrix} 1 & 0 & 0 & 1 & 0 & 0 \\ 0 & 1 & 0 & 1 & 0 & 1 \\ 0 & 0 & 1 & 1 & 1 & 1 \end{bmatrix}$$

$$= \begin{bmatrix} 0 \cdot 1 \oplus 0 \cdot 0 \oplus 0 \cdot 0 & 0 \cdot 0 \oplus 0 \cdot 1 \oplus 0 \cdot 0 & 0 \cdot 0 \oplus 1 \cdot 0 \\ \oplus 0 & 1 & 0 \cdot 1 \oplus 0 \cdot 1 \oplus 0 \cdot 1 & 0 \cdot 0 \oplus 0 \cdot 0 \oplus 0 \cdot 1 \\ 0 \cdot 0 \oplus 1 \cdot 1 \oplus 0 \cdot 1 & 0 \end{bmatrix}$$

$$= \begin{bmatrix} 0000000 \end{bmatrix}$$

Similarly we have,

#### Code for message 0 0 1:

$$C = [001] \begin{bmatrix} 1 & 0 & 0 & 1 & 0 & 0 \\ 0 & 1 & 0 & 1 & 0 & 1 \\ 0 & 0 & 1 & 1 & 1 & 1 \end{bmatrix}$$

= 001111

#### Code for message 0 1 0:

$$C = [010] \begin{bmatrix} 1 & 0 & 0 & \vdots & 1 & 0 & 0 \\ 0 & 1 & 0 & \vdots & 1 & 0 & 1 \\ 0 & 0 & 1 & \vdots & 1 & 1 & 1 \end{bmatrix}$$

= 010101

#### Code for message 0 1 1:

$$C = [011] \begin{bmatrix} 1 & 0 & 0 & \vdots & 1 & 0 & 0 \\ 0 & 1 & 0 & \vdots & 1 & 0 & 1 \\ 0 & 0 & 1 & \vdots & 1 & 1 & 1 \end{bmatrix}$$

= 011010

#### Code for message 100:

$$C = [100] \begin{bmatrix} 1 & 0 & 0 & 1 & 0 & 0 \\ 0 & 1 & 0 & 1 & 0 & 1 \\ 0 & 0 & 1 & 1 & 1 & 1 \end{bmatrix}$$

= 100 100

#### Code for message 101:

$$C = \begin{bmatrix} 1 & 0 & 1 & 0 & 0 \\ 0 & 1 & 0 & 1 & 0 & 1 \\ 0 & 0 & 1 & 1 & 1 & 1 \end{bmatrix}$$

= 101011

$$\mathbf{R}^{\mathsf{T}} = \begin{bmatrix} 1 \\ 1 \\ 0 \\ 0 \\ 1 \\ 0 \end{bmatrix}$$

$$HR^{T} = \begin{bmatrix} 1 & 1 & 1 & 1 & 1 & 0 & 0 \\ 0 & 0 & 1 & 1 & 0 & 1 & 0 \\ 0 & 1 & 1 & 1 & 0 & 0 & 1 \end{bmatrix} \begin{bmatrix} 1 \\ 1 \\ 0 \\ 0 \\ 1 \\ 0 \end{bmatrix}$$

$$= \begin{bmatrix} 1 \cdot 1 & 0 & 1 \cdot 1 & 0 & 1 \cdot 0 & 0 & 0 \cdot 1 & 0 \cdot 0 \\ 0 \cdot 1 & 0 & 0 \cdot 1 & 0 & 1 \cdot 0 & 0 \cdot 0 & 0 \cdot 1 & 0 \cdot 0 \\ 0 \cdot 1 & 0 \cdot 1 & 0 & 1 \cdot 0 & 0 & 0 \cdot 0 & 0 \cdot 1 & 0 \cdot 0 \\ 0 \cdot 1 & 0 \cdot 1 & 0 & 1 \cdot 0 & 0 \cdot 0 & 0 \cdot 0 & 0 \cdot 1 & 0 \cdot 0 \end{bmatrix}$$

$$= \begin{bmatrix} 0 \\ 1 \\ 1 \end{bmatrix}$$

Since  $HR^T \neq 0$ , received code is wrong.

#### 3.5.4 Error Correction

It is assumed that the coding/decoding system has been designed to correct single error only. In order to correct the codeword we multiply received codeword with transpose of parity-check matrix to get **syndrome**. Then result of RH<sup>T</sup>, i.e. syndrome is compared with the row of transpose of parity-check matrix (H<sup>T</sup>). Matching row number is the number of bit in error. Error bit is then inverted to get the correct code.

The procedure is given below:

1. Find S = RHT

where

R: Received code

HT : Transpose of T

$S = [S_1, S_2, S_3 ...]$  is called **syndrome**.

Match the result, i.e. S with row of H<sup>T</sup>. The number of row where the match occur gives the number of bit in error. This bit is inverted to correct the error.

Ex. 3.8: For a (6, 3) block code received code is

$$110100$$

. If  $A = \begin{bmatrix} 1 & 0 & 0 \\ 1 & 0 & 1 \\ 1 & 1 & 1 \end{bmatrix}$ . Find the received code

is correct or wrong. If wrong correct it.

The decoding technique for the burst code is similar to the technique used for cyclic codes.

92

#### 3.8 Check-sums and Cyclic Redundancy Checks

Check-sums and cyclic redundancy checks are used to detect error in the transmission of block of data. Check-sum is formed by adding all the data bytes in the block, ignoring any carries. It is the arithmetic sum of all data bytes. The resulting sum is stored after the data block. When the data is read, it is re-added and the sum is compared with the recorded check-sum. There is no error in the data transmission if both the sum matches; otherwise data has to be re-transmitted.

The cyclic redundancy check (CRC) involves dividing the string of data bytes by a constant. Any remainder from this division is written in as 2 CRC bytes, or characters. When the data is read out, these 2 bytes are subtracted from the data string. The result is divided by the original constant. This division gives a zero remainder if the data contains no errors. The CRC method is usually used for error checking of disk storage.

Ex. 3.9: What would be the checksum of the following characters?

(May-2000)

01011010 11000101 11011001

Sol.: The checksum is

01011010

- + 11000101

- + 11011001

In hexadecimal it is represented as (F8)16

#### 3.9 Hamming Code

Hamming code not only provides the detection of a bit error, but also identifies which bit is in error so that it can be corrected. Thus Hamming code is called error detecting and correcting code. The code uses a number of parity bits (dependent on the number of information bits) located at certain positions in the code group. Follows sections describe how Hamming code can be constructed for single error correction.

#### 3.9.1 Number of Parity Bits

As mentioned earlier, number of parity bits depend on the number of information bits. If the number of information bits is designed x, then the number of parity bits, P is determined by the following relationship:

$$2_{p} \geq x + p + 1 \qquad \dots (1)$$

For example, if we have four information bit, i.e. x = 4, then P is found by trial and error using equation 1. Let p = 2. Then

$$2^{P} = 2^{2} = 4$$

#### Error Detecting & Correcting Codes

| Step 2: | Check for | r parity bits |

|---------|-----------|---------------|

|         |           | 1             |

For P<sub>1</sub>: P<sub>1</sub> checks locations 1, 3, 5, and 7.

There is one 1 in the group.

For P2: P2 checks locations 2, 3, 6 and 7.

There are two 1s in the group

For P<sub>4</sub>: P<sub>4</sub> checks locations 4, 5, 6 and 7.

There are one 1 in the group

The resultant word is 101. This says that the bit in the number 5 location is in error. It is 0 and should be a 1. Therefore, the correct code is 0 1 1 0 0 1 1, which agrees with the transmitted code.

Ex. 3.13: The Hamming code 1 0 1 1 0 1 1 0 1 is received. Correct it if any errors. There are four parity bits and odd parity is used.

Sol.: Step 1: Construct a bit location table

| Bit designation        | D <sub>9</sub> | P <sub>8</sub> | D <sub>7</sub> | D <sub>6</sub> | D <sub>5</sub> | P <sub>4</sub> | D <sub>3</sub> | P <sub>2</sub> | P <sub>1</sub> |

|------------------------|----------------|----------------|----------------|----------------|----------------|----------------|----------------|----------------|----------------|

| Bit location           | 9              | 8              | 7              | 6              | 5              | 4              | 3              | 2              | 1              |

| Binary location number | 1001           | 1000           | 0111           | 0110           | 0101           | 0100           | 0011           | 0010           | 0001           |

| Received code          | 1              | 0              | 1              | 1              | 0              | 1              | 1              | 0              | 1              |

Step 2: Check for parity bits

For  $P_1$ :  $P_1$  checks locations 1, 3, 5, 7 and 9.

There are four 1s in the group

∴Parity check for odd parity is wrong ······ → 1 (LSB)

For P<sub>2</sub>: P<sub>2</sub> checks locations 2, 3, 6 and 7.

There are three 1s in the group

$\therefore$ Parity check for odd parity is correct  $\cdots \rightarrow 0$

For P4: P4 checks locations 4, 5, 6 and 7.

There are three 1s in the group

$\therefore$  Parity check for odd parity is correct  $\cdots \rightarrow 0$

For P<sub>8</sub>: P<sub>8</sub> checks locations 8 and 9.

There is one 1 in the group

$\therefore$  Parity check for odd parity is correct  $\cdots \rightarrow 0$

The resultant word is 0 0 0 1. This says that the bit in the number 1 location is in error. It is 1 and should be a 0. Therefore, the correct code is 1 0 1 1 0 1 1 0 0.

basic elements forming the building blocks for complex digital system such as the computer.

Irish logician and mathematician George Boole developed a mathematical system for formulating logical statements with symbols, so that problems could be written and solved in a manner similar to ordinary algebra. Boolean algebra, as it is known today, finds application in the analysis and design of digital systems.

In this chapter we will study logic gates and we will see how their operation can be described using Boolean algebra. We will also see how logic gates can be combined to produce logic circuits, and how these circuits can be described and analyzed using Boolean algebra.

#### 4.2 Logical Operators

We know that, to represent and solve arithmetic expressions we use arithmetic operators such as +, -, × and +. Similarly, we can use logical operators to represent and solve logical expressions. There are three basic logical operators: NOT/INVERT, AND and OR.

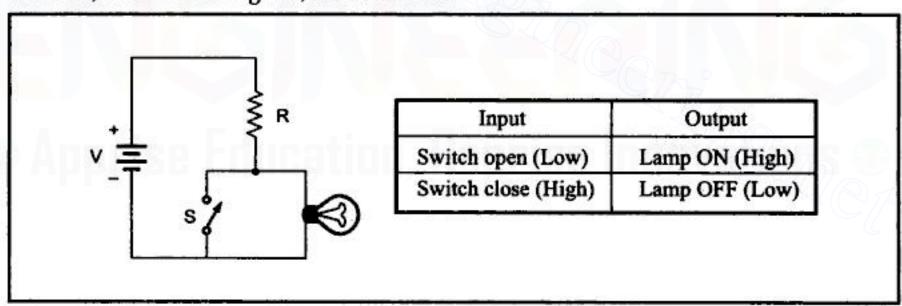

#### 4.2.1 Logical Operator NOT/INVERT

The inversion (or complementing or negation) operator is written as a bar over its argument. Sometimes it is written "NOT". Thus the inverse of A is Aor NOT A. The logic operator NOT can be better understood if the switching-circuit realization of NOT function, as shown in Fig. 4.1, is considered.

Fig. 4.1 Switching circuit analogy of NOT function

When the switch S is open, lamp is 'ON' and when the switch S is close, lamp is 'OFF'.

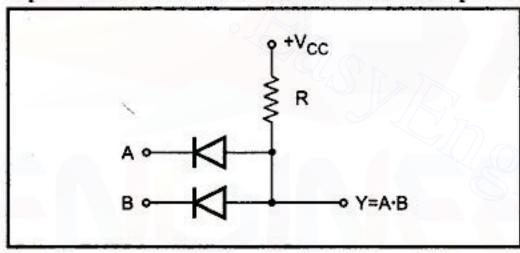

#### 4.2.2 Logical operator AND

It is denoted by 'x' or '.' These signs may be omitted, similar to ordinary algebra. For example: A ·B, A × B or AB has a same meaning. A ·B may be read as 'A and B' or 'A times B'. A ·B is high if A and B are both high and otherwise low. The logic operator AND can be better understood if the switching-circuit realization of AND function as shown in Fig. 4.2, is considered. AND gate denotes lowest value of the input variables.

The truth table for a two-input AND gate is shown in Table 4.2. This table can be expanded for any number of inputs. For any AND gate, regardless of the number of inputs, the output is high only when all inputs are HIGH.

| Inp | Inputs |   |  |  |  |  |

|-----|--------|---|--|--|--|--|

| A   | В      | Y |  |  |  |  |

| 0   | 0      | 0 |  |  |  |  |

| 0   | 1      | 0 |  |  |  |  |

| 1   | 0      | 0 |  |  |  |  |

| 1   | 1      | 1 |  |  |  |  |

Table 4.2 Truth table for 2 input AND gate

Fig. 4.9 shows one way to build a 2-input AND gate. The inputs are labelled A and B, while the output is Y. Let us assume a supply voltage  $V_{CC}$  of +5 V. Also we will assume the input voltages are either 0 V (Low) or +5 V (High). With 2 inputs, there are four possible input cases and we will now observe the output for all four input cases.

Fig. 4.9 2-input AND gate

CASE 1: A is low and B is low: When both input voltages are low, the cathode of each diode is grounded. Therefore, the positive supply forward-biases both diodes in parallel. Because of this, the output voltage is ideally zero (practically 0.7 V for Si). This means Y is low.

#### CASE 2: A is low and B is high:

When A is low, the upper diode is forward-biased (ON), and it pulls the output down to a low voltage, i.e. Y = 0. With the B input high, the lower diode goes into reverse bias (OFF).

CASE 3: A is high and B is low: Because of the symmetry of the circuit, the circuit operation is similar to case 2. But in this case, upper diode is reverse biased (OFF), lower diode is forward biased (ON), and Y is low.

CASE 4: A is high and B is high: When both inputs are at +5 V, both diodes are reverse biased and there is no current through diodes and resistor R. This pulls up the output Y to the supply voltage. Therefore, Y is high.

#### **Pulsed Operation:**

In a majority of applications, the inputs to a gate are not constant levels but are voltages that change with time between two logic levels and that can be classified as pulse waveforms. Let us study the operation of AND gate with pulsed input waveforms. Keep in mind that an AND gate obeys the truth table operation regardless of whether its inputs are constant levels or pulsed levels. In studying the pulsed operation of the AND gate, we

Fig. 4.16 Pin diagram of a 7432

#### 4.3.4 The NAND gate

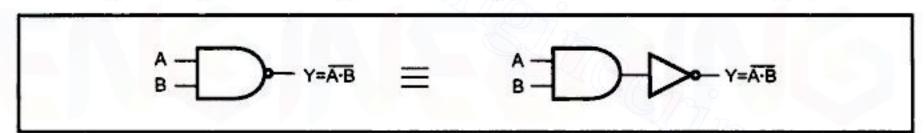

The term NAND is a contraction of NOT-AND and implies an AND function with a complemented (inverted) output. A standard logic symbol for a two-input NAND gate and its equivalency to an AND gate followed by an inverter are shown in Fig. 4.17.

Fig. 4.17 NAND gate symbol and equivalent circuit

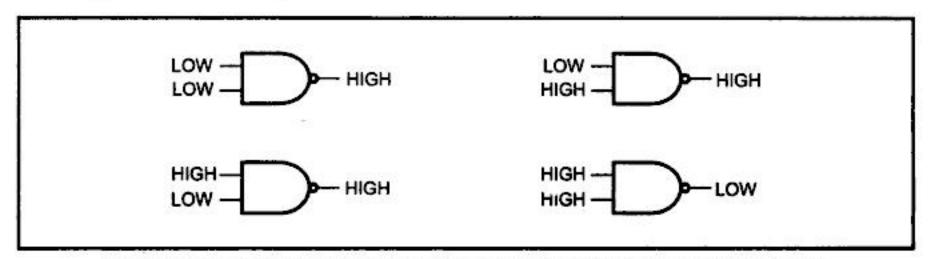

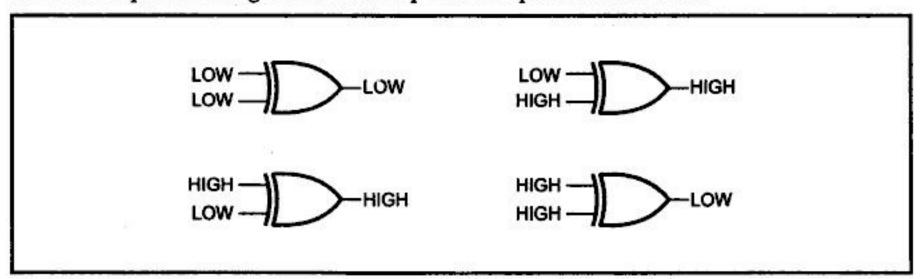

The NAND gate is a universal gate as it can be used to construct an AND gate, an OR gate an inverter, or any combination of these functions. The logical operation of the NAND gate is such that a LOW output occurs only when all inputs are HIGH. When any of the inputs is LOW, the output will be HIGH. Note that this operation is opposite to that of the AND as far as output is concerned. Fig. 4.18 illustrates the logical operation of a two-input NAND gate for all four input combinations.

Fig. 4.18 Four possible inputs for two input NAND Gate and resulting outputs

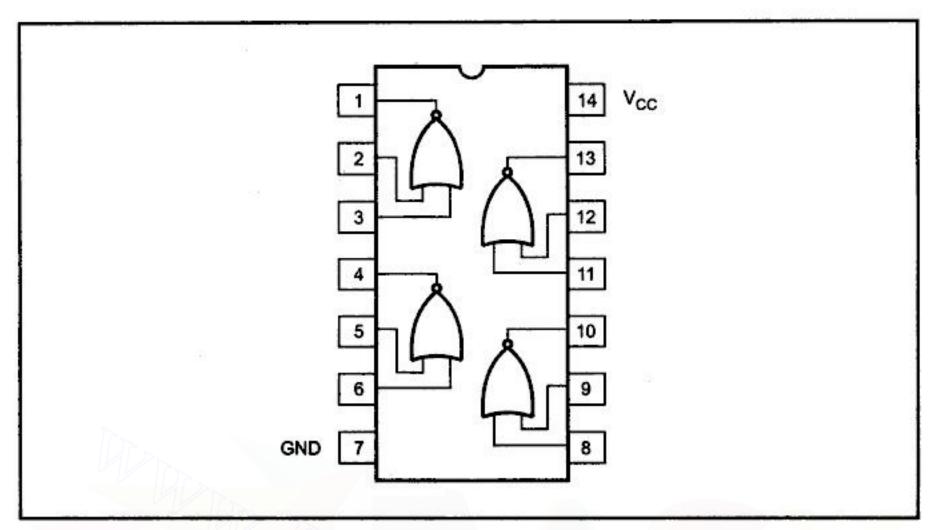

Fig. 4.24 Pln diagram of a 7402

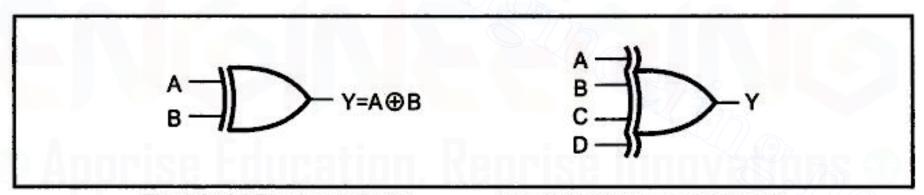

#### 4.3.6 The Exclusive-OR Gate

The EX-OR gate is an abbreviation for Exclusive-OR gate. An EX-OR gate has two or more inputs and one output, as indicated by the standard logic symbol in Fig. 4.25 where EX-OR gates with two and four inputs are shown.

Fig. 4.25 (a) Two input EX-OR

Fig. 4.25 (b) Four input EX-OR

It recognizes only the words that have an odd number of ones. This means that for odd number of ones, output of EX-OR gate is high. The Fig. 4.26 illustrates the logic operation for a two-input EX-OR gate for all four possible input combinations.

Fig. 4.26 Four possible inputs for two input EX-OR gate and resulting outputs

Fig. 4.32 Pin diagram of a 74266

#### Points to Remember

- In digital systems, two voltage levels represent the two binary digits, 1 and 0. If

the higher of the two voltages represents 1 and the lower voltage represents 0,

the system is called a positive logic system. On the other hand, if the lower

voltage represents a 1 and the higher voltage represents a 0, the system is

called a negative logic system.

- 2. Three basic logical operators are: AND, OR and NOT.

- 3. Logic gates are the basic elements that make up a digital system.

- 4. The logic gate is a digital circuit with one or more inputs but only one output.

- The inverter performs a basic logic function called inversion. It changes one logic level to its opposite level.

- For any AND gate, regardless of the number of inputs, the output is HIGH only when all inputs are HIGH.

- An OR gate produces a HIGH on the output when any of the inputs is HIGH. The output is LOW only when all of the inputs are LOW.

- The logical operation of NAND gate is such that a low output occurs only when all inputs are HIGH.

- The logic operation of the NOR gate is such that a LOW output occurs when any of its inputs is HIGH. The output is HIGH, only when all of its inputs are LOW.

- 10. For odd number of ones, at the input, the output of EX-OR gate is HIGH.

- 11. For even number of ones at the input, or inputs having all zeroes, the output of EX-NOR gate is HIGH.

### **Digital Electronics**

120

#### Logic Gates and Boolean Algebra

| V-12.7.2. |   | Act and the second |       |             |   |   |   |   |       |             |

|-----------|---|--------------------|-------|-------------|---|---|---|---|-------|-------------|

| A         | В | С                  | A + B | (A + B) + C |   | Α | В | С | B + C | A + (B + C) |

| 0         | 0 | 0                  | 0     | 0           |   | 0 | 0 | 0 | 0     | 0           |

| 0         | 0 | 1                  | 0     | 1           |   | 0 | 0 | 1 | 1     | 1           |

| 0         | 1 | 0                  | 1     | 1           |   | 0 | 1 | 0 | 1     | 1           |

| 0         | 1 | 1                  | 1     | 1           | = | 0 | 1 | 1 | 1     | 1           |

| 1         | 0 | 0                  | 1     | 1           |   | 1 | 0 | 0 | 0     | . 1         |

| 1         | 0 | 1                  | 1     | 1           |   | 1 | 0 | 1 | 1     | 1           |

| 1         | 1 | 0                  | 1     | 1           |   | 1 | 1 | 0 | 1     | 1           |

| 1         | 1 | 1                  | 1     | 1           |   | 1 | 1 | 1 | 1     | 1           |

Table 4.11 Truth tables for associative law for OR gates

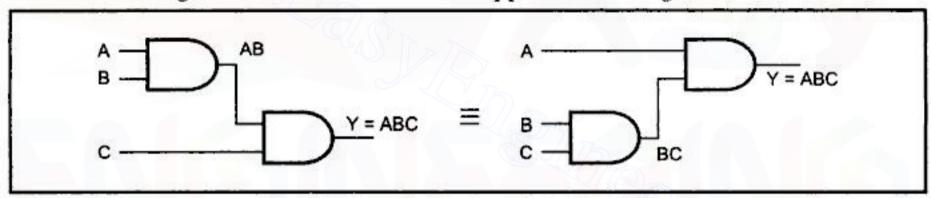

LAW 2: (AB) C = A (BC): The associative law of multiplication states that it makes no difference in what order the variables are grouped when ANDing several variables. For three variables, A AND B ANDed with C is the same as A ANDed with B and C. The Fig. 4.35 illustrates this law as applied to AND gates.

Fig. 4.35 Associative law applied to AND gates

| A | В | С | AB | (AB) C | R   | A | В | С | BC | A (BC) |

|---|---|---|----|--------|-----|---|---|---|----|--------|

| 0 | 0 | 0 | 0  | 0      | 111 | 0 | 0 | 0 | 0  | 0      |

| 0 | 0 | 1 | 0  | 0      |     | 0 | 0 | 1 | 0  | 0      |

| 0 | 1 | 0 | 0  | 0      |     | 0 | 1 | 0 | 0  | 0      |

| 0 | 1 | 1 | 0  | 0      |     | 0 | 1 | 1 | 1  | 0      |

| 1 | 0 | 0 | 0  | 0      |     | 1 | 0 | 0 | 0  | o      |

| 1 | 0 | 1 | 0  | 0      |     | 1 | 0 | 1 | 0  | 0      |

| 1 | 1 | 0 | 1  | 0      |     | 1 | 1 | 0 | 0  | o      |

| 1 | 1 | 1 | 1  | 1      | 1   | 1 | 1 | 1 | 1  | 1      |

Table 4.12 Truth table for associative law for AND gates

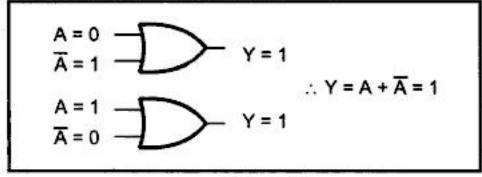

#### Illustration of Rule 6

Fig. 4.42

Rule 6 says that when variable and its complement are ORed, the result is always 1. As shown in Fig. 4.42, when A = 0,  $A + \overline{A} = 0 + 1 = 1$  and when A = 1,  $A + \overline{A} = 1 + 0 = 1$ .

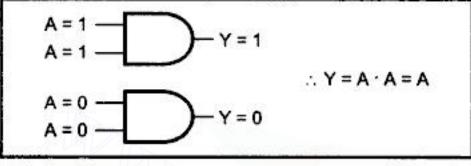

#### Illustration of Rule 7

Fig. 4.43

Rule 7 says that if variable is ANDed with itself, the result is equal to the variable. As shown in Fig. 4.43, when A = 1,  $1 \cdot 1 = 1$  and when A = 0,  $0 \cdot 0 = 0$ .

#### Illustration of Rule 8

Fig. 4.44

#### Illustration of Rule 9

Fig. 4.45

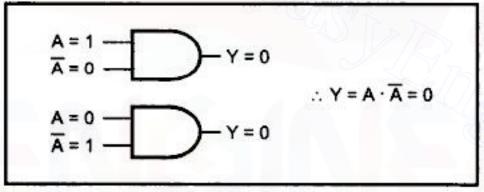

Rule 8 says that when variable and its complement are ANDed, the result is always 0. As shown in Fig. 4.44, when A = 1,  $A \cdot \overline{A} = 1 \cdot 0 = 0$ , and when A = 0,  $A \cdot \overline{A} = 0 \cdot 1 = 0$ .

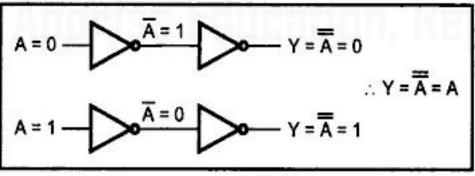

Rule 9 says that if a variable is complemented twice, the result is the variable itself. When A = 0, A = 0 and when A = 1, A = 1.

#### Proof of Rule 10

Rule 10 is given as

$$A + AB = A$$

$L.H.S. = A + AB$

$= A (1 + B)$

$= A (1)$

$= A$

#### Proof of Rule 11

Rule 11 is given as  $A + \overline{AB} = A + B$

Distributive law Rule 2 :  $(1 + A = 1)^*$ Rule 4  $(A \cdot 1 = A)$  ... proved

## 4.5 Universal Property

The NAND and NOR gates are known as universal gates, since any logic function can be implemented using NAND or NOR gates. This is illustrated in following sections

$= \overline{A} + B + \overline{C} + \overline{B}$

$= \overline{A} + \overline{C} + 1$

Rule 11 :  $[A + \overline{A}B = A + B]$

Rule 6:  $[A + \overline{A} = 1]$

Rule 2: [A + 1 = 1]

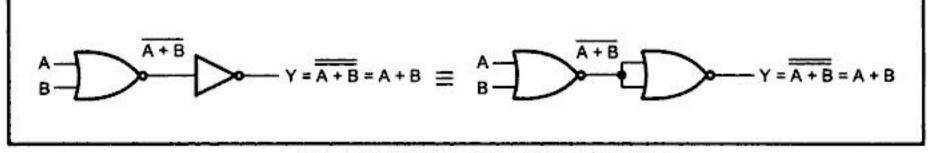

#### OR Function:

An OR function can be generated using only NOR gates. It can be generated by simply inverting output of NOR gate; i.e.  $\overline{A} + \overline{B} = A + B$ . Fig. 4.53 shows the two input OR gate using NOR gates.

Fig. 4.53 OR function using NOR gates

| A | В | A + B |   | A | В | A+B | A+B |

|---|---|-------|---|---|---|-----|-----|

| 0 | 0 | 0     |   | 0 | 0 | 1   | 0   |

| 0 | 1 | 1     | = | 0 | 1 | 0   | 1   |

| 1 | 0 | 1     | 3 | 1 | 0 | 0   | 1   |

| 1 | 1 | 1     |   | 1 | 1 | 0   | 1   |

Table 4.20 Truth table

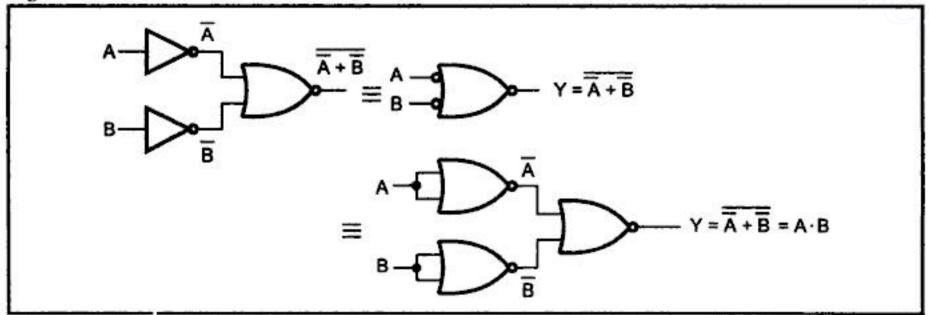

#### AND Function:

AND function is generated using only NOR gates as follows: We know that Boolean expression for AND gate is

$$Y = A \cdot B$$

$= \overline{A} \cdot \overline{B}$

$= \overline{A} + \overline{B}$

Rule 9 :  $[\overline{A} = A]$

DeMorgan's Theorem 2

The above equation is implemented using only NOR gates as shown in the Fig. 5.54.

Fig. 4.54 AND function using NOR gates

Note: Bubble at the input of NOR gate indicates inverted input.

#### **NOR Circuit**

Fig. 4.59

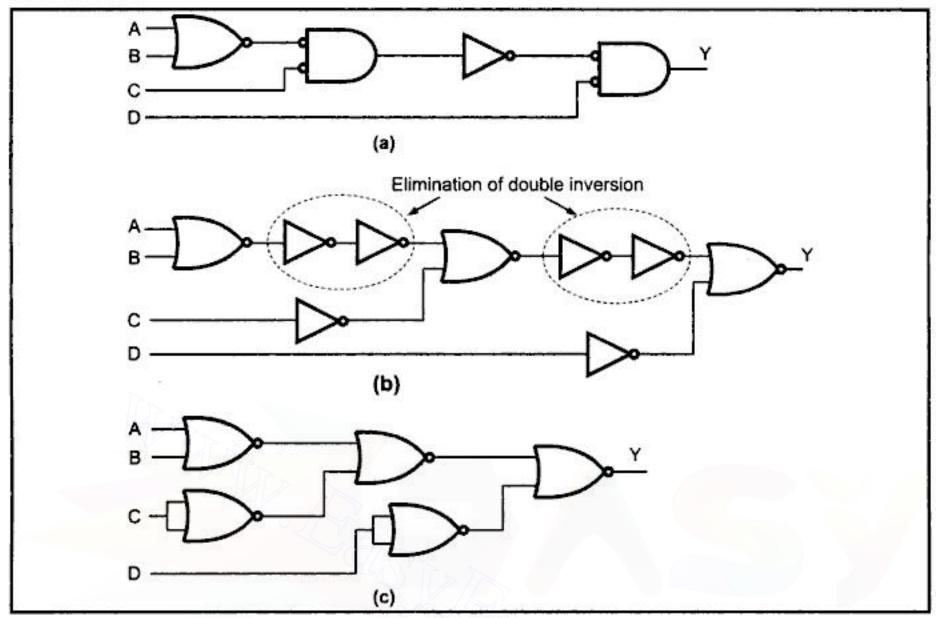

The straight forward method for implementing the given expression uses two AND gates, one OR gate and one inverter, as shown in the Fig. 4.57. Now we will see implementation of this circuit accomplished by replacing each AND gate, OR gate and inverter by its equivalent NAND gate using steps mentioned earlier. This is illustrated in Fig. 4.58. If we now compare original circuit and the circuit with NAND gates, we find that three ICs are required (AND, OR, and INVERTER) to implement original circuit, whereas only two NAND ICs are required for the circuit with NAND gates. (With two NAND ICs we have 8 NAND gates and only 6 NANDs are required to implement the logic circuits).

Applying similar steps for NOR gate we get NOR circuit as shown in Fig. 4.59. Here, we need only two ICs of NOR gate.

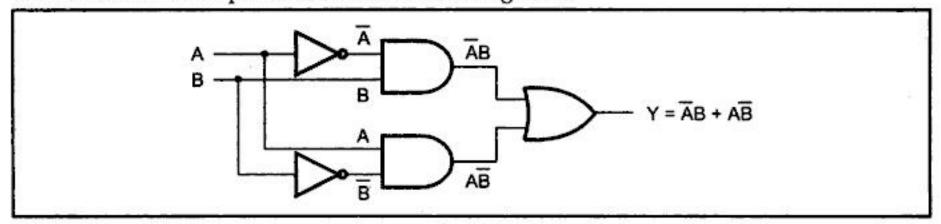

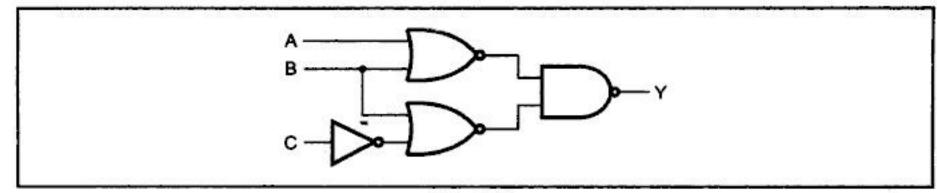

Ex. 4.16: Implement Boolean expression for EX-OR gate using NAND gates. (Dec-99, Dec-2002)

Sol.: Boolean expression for EX-OR gate is AB + AB. Using AND/OR/INV logic the circuit can be implemented as shown in Fig. 4.60.

Fig. 4.60

EEEbooks4U

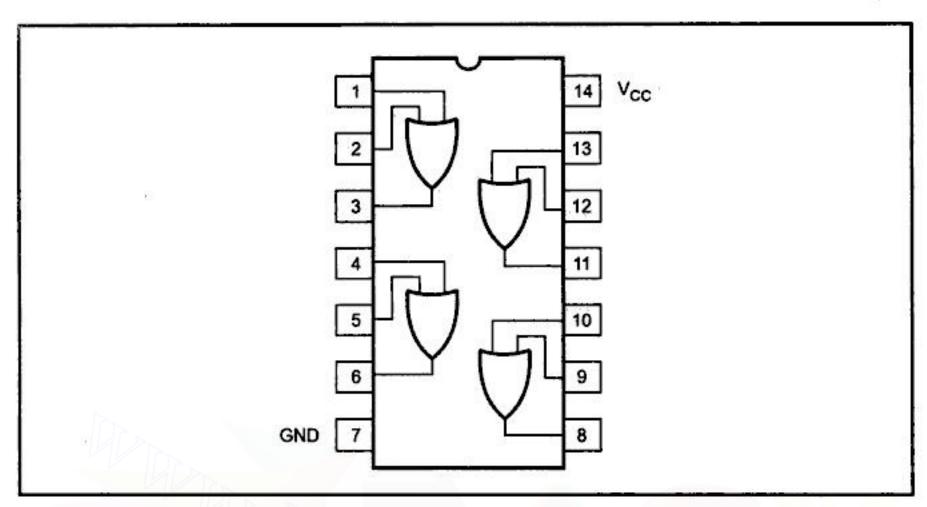

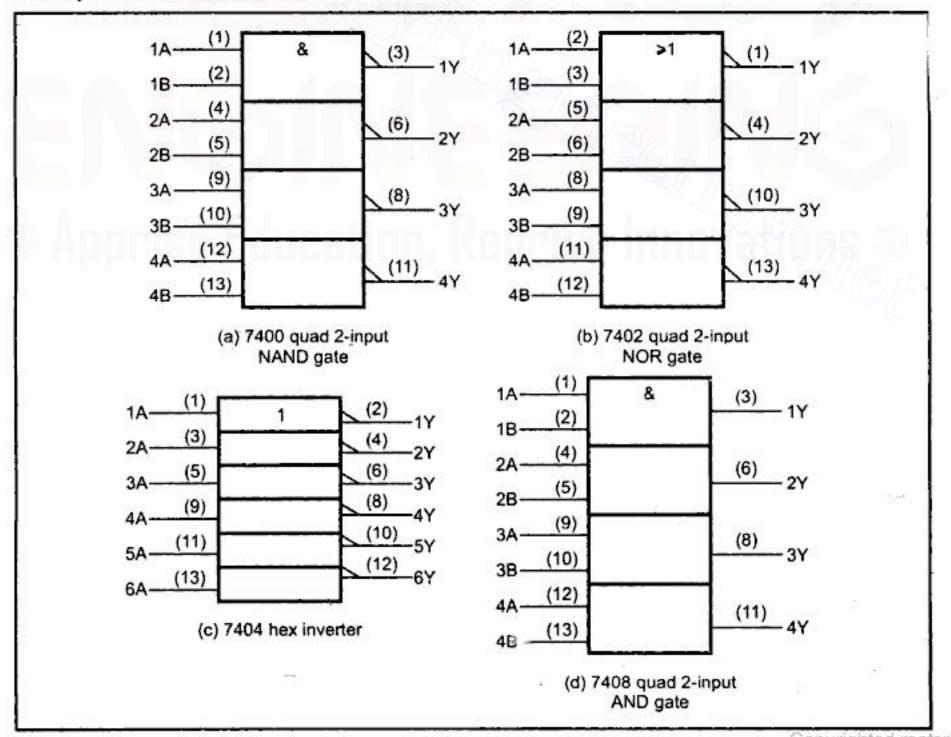

The symbols used to represent logic gates in this chapter have been used in the digital industry for many years. These symbols work well for the logic gates because each gate symbol has distinctive shape, and each gate input has the same function. They do not provide enough useful information, however, for the more complex logic devices such as Flip-Flops, counters decoders etc. In order to provide more useful information about these complex logic devices, a new set of standards was introduced jointly by the American National standards Institute (ANSI) and the institute of Electrical and Electronics Engineers (IEEE) in 1984. This standard is commonly known as standard 91-1984 and is now being used by many industries and manufacturers of electronic devices.

The principal difference in the new standard is that it uses rectangular symbols for all devices instead of different symbol shapes for each device. A special dependency notation system is used to indicate how the outputs depend on the inputs. These dependency notations are also called as qualifying symbols, which are placed inside the rectangle to indicate the type of logic operations.

Fig. 4.64 (See Fig. on previous page) shows the newer rectangular symbols for various gates.

The ANSI/IEEE logic symbols for integrated circuits containing multiple logic gates are drawn by stacking rectangles on top of each other, one rectangle for each gate. Fig. 4.65 shows the ANSI/IEEE symbols for each of the 7400- series circuits whose pin diagrams are already shown in section 4.3.

Fig. 4.65 (continued on next page)

Copyrighted material Downloaded From: www.EasyEngineering.net

## **Digital Electronics**

#### 144

### Logic Gates & Boolean Algebra

Ex. 4.21: Determine the truth table for the circuit shown in Fig. 4.71.

Fig. 4.71

#### Sol.:

$$Y = \overline{A + B \cdot B + \overline{C}}$$

$$= \overline{A + B} + \overline{B + \overline{C}}$$

$$= A + B + B + \overline{C}$$

$$= A + B + \bar{C}$$

De Morgan's Theorem 1

Rule 9 :

$$\overline{A} = A$$

Rule

$$5: [A + A = A]$$

| A  | В | С | Y |

|----|---|---|---|

| 0  | 0 | 0 | 1 |

| 0  | 0 | 1 | 0 |

| 0  | 1 | 0 | 1 |

| 0  | 1 | 1 | 1 |

| 1  | 0 | 0 | 1 |

| 1  | 0 | 1 | 1 |

| 1, | 1 | 0 | 1 |

| 1  | 1 | 1 | 1 |

Truth table 4.24

Ex. 4.22: Simplify the following expression

$$Y = (A + B)(\overline{A} + C)(\overline{B} + \overline{C})$$

$$= (A\overline{A} + AC + \overline{A}B + BC)(\overline{B} + \overline{C})$$

$$= (AC + \overline{A}B + BC)(\overline{B} + \overline{C})$$

$$= (AC + \overline{A}B + BC)(\overline{B} + \overline{C})$$

$$= A\overline{B}C + AC\overline{C} + \overline{A}B\overline{B} + \overline{A}B\overline{C} + B\overline{B}C + BC\overline{C}$$

$$= A\overline{B}C + \overline{A}B\overline{C}$$

Rule 8:  $[A\overline{A} = 0]$

Ex. 4.23: Simplify each of the following using Demorgan's theorem

a)

$$\overline{(A+B)(\overline{A}+B)}$$

b)  $\overline{A}\overline{B}\overline{C}D$

### Logic Gates & Boolean Algebra

## Therefore logic circuit is

Fig. 4.78

Ex. 4.27: Implement Y = ABCD using two inputs NAND gates

Sol.:

$$Y = ABCD$$

$$= \overline{AB} + \overline{CD}$$

$$= \overline{AB} + \overline{CD}$$

$$= \overline{AB} + \overline{CD}$$

DeMorgan's Theorem 1

$$= \overline{AB} + \overline{CD}$$

DeMorgan's Theorem 2

$$= \overline{AB} + \overline{CD}$$

## Therefore the logic circuit is

Flg. 4.79

Ex. 4.28: Draw the circuit shown in Fig. 4.80 using ANSI/IEEE symbols

Fig. 4.80

### Digital Electronics

i)

#### Logic Gates & Boolean Algebra

$$F_{1} = \overline{x} y \overline{z} + \overline{x} \overline{y} z$$

$$= \overline{x} y \overline{z} + \overline{x} \overline{y} z$$

$$= \overline{x} y \overline{z} + \overline{x} \overline{y} z$$

$$= (\overline{x} + \overline{y} + \overline{z}) \cdot (\overline{x} \overline{y} \overline{z})$$

$$= (x + \overline{y} + z) \cdot (x + y + \overline{z})$$

$$= x x + xy + x\overline{z} + x \overline{y} + y \overline{y} + y \overline{z} + xz + y z + z\overline{z}$$

$$= x + xy + x \overline{z} + x \overline{y} + y \overline{z} + xz + y z$$

$$= x (1 + y + \overline{z} + y + z) + y \overline{z} + yz$$

$$= x + y \overline{z} + y z$$

ii)

$$F_2 = x (\overline{y} \overline{z} + y z)$$

..

$$\overline{F_2} = \overline{x} (\overline{y} \overline{z} + y z)$$

$$= \overline{x} + (\overline{y} \overline{z} + y z)$$

$$= \overline{x} + (\overline{y} \overline{z} \cdot y z)$$

$$= \overline{x} + [(\overline{y} + z) \cdot (\overline{y} + z)]$$

$$= \overline{x} + [(y + z) \cdot (\overline{y} + \overline{z})]$$

$$= \overline{x} + (y \overline{y} + y \overline{z} + y z + z \overline{z})$$

$$= \overline{x} + (y \overline{z} + \overline{y} z)$$

### **Review Questions**

- 1. Draw a typical digital signal waveform and properly identify the two operating levels.

- 2. Define positive logic and negative logic.

- 3. Write the names of basic logical operators.

- 4. What is a logic gate?

- 5. Draw the logic symbol and construct the truth table for each of the following gates:

- a) Two input NAND gate

- b) Three input OR gate

- c) Two input EX-OR gate

- d) Three input EX-NOR gate

- e) NOT gate

- 6. Write the names of Universal Gates.

- 7. Why are NAND and NOR gates known as Universal gates?

- 8. Give the Boolean expressions used for following gates

- a) AND

- b) NOR

- c) EX-OR

- d) OR

- e) NOT

| Digital | Ele | ctr | oni | ÇS |

|---------|-----|-----|-----|----|

|         |     |     |     |    |

#### Logic Gates & Boolean Algebra

34. 'NAND and NOR gates are called universal gates.' Justify.

(Dec-96)

35. Implement EX-OR gate using only four NAND gates.

(May-97)

36. Verify the Boolean function

$$AB + \overline{A}C + BC = AB + \overline{A}C$$

(May-97)

37. State and explain principle of duality.

(May-97)

38. Using Boolean Algebra prove:

$$i) A + BC = (A + B) \times (A + C)$$

$$ii)\left(\overline{AC}\right)\left(\overline{B}+\overline{C}\right)\left(\overline{B}\right)=\left(\overline{A}+\overline{B}+\overline{C}\right)+\overline{B}+\overline{C}$$

iii)

$$\overline{(AB + BC)}$$

.  $AC = \overline{A} + \overline{C}$

(May-97)

39. By using Boolean algebra simplify the following:

(Dec-97)

i)

$$\overline{AB} + \overline{ABC} + \overline{A(B+AB)}$$

ii)

$$(AB + \overline{AC} + A\overline{B}C(AB + C)$$

$$iii)$$

( $\overline{CD}$  + A) + A + CD + AB

$$(v) \overline{A + B \cdot A + B}$$

Ans.: i) A+BC, ii) 1, iii) CD + B, iv) 0

40. Implement OR Gate using Diodes and verify its truth table.

(Dec-97)

- 41. Demonstrate by means of truth tables the validity of the following theorems of Boolean algebra:

- (i) The associative law

- (ii) The distributive law

- (iii) De Morgan's theorem for three variables.

(May-98)

42. Simplify the following Boolean functions:

(i)

$$\overline{W} \overline{X} YZ + \overline{W} XYZ + W \overline{X} YZ + W XYZ + W XY \overline{Z}$$

(ii)

$$\overline{ABC} + AB + \overline{ABC} + \overline{BC}$$

.

(May-98)

Ans.: i) Y (z + WX), ii) 1

43. By using the rules of Boolean algebra reduce the following expressions:

(i)

$$Y = (A + \overline{B} + \overline{C})(\overline{A} + B)(B + \overline{C}).$$

(ii)

$$L = \overline{PQ}RS + \overline{PQ}$$

(Dec-98)

Ans.: (i)

$$AB + \overline{C}(\overline{A} + B)$$

, (ii)  $R(S + PQ)$

44. Implement the EX-OR logic operation with only NAND gates.

(Dec-99)

45. State and explain the De Morgan's theorem.

(Dec-99, May-2000, Dec-2000)

46. Using Boolean Algebra, show that

(Dec-99)

i)

$$\overline{ab} + bc + \overline{abc} = \overline{a+bc}$$

ii)

$$D(\overline{A} + \overline{B}) + \overline{B}(C + AD) = D + \overline{B}C$$

$$iii)(A+B)(A+C)=A+BC$$

iv)

$$x y z + xyz + xyz + xyz = y$$

47. Using Boolean Algebra show that

(i)

$$AB + AC + \overline{B}C = AB + \overline{B}C$$

#### Simplification of Boolean Functions

Let us see one standard sum of products expression:

$$Y = A\overline{B} C + ABC + \overline{A}B \overline{C}$$

$$= AC (\overline{B} + B) + \overline{A} B\overline{C}$$

$$= AC + \overline{A} B\overline{C}$$

161

Here, the original expression is standard sum of products, but the simplified expression is not a standard sum of products. It is only sum of products.

Similarly, we can say that a product of sums is a standard (canonical) product of sums if every sum terms involves every literal or its complement. For example,

$$Y = (A + B + C) (A + \overline{B} + C)$$

## 5.2.4 Converting Expressions in Standard SOP or POS Forms

Sum of products form can be converted to standard sum of products by ANDing the terms in the expression with terms formed by ORing the literal and its complement which are not present in that term. For example for a three literal expression with literals A, B and C, if there is a term AB, where C is missing, then we form term  $(C + \overline{C})$  and AND it with AB. Therefore, we get AB  $(C + \overline{C}) = ABC + AB\overline{C}$

Ex. 5.1: Convert the given expression in standard SOP form.

$$Y = AC + AB + BC$$

$$= AC (B + \overline{B}) + AB (C + \overline{C}) + BC (A + \overline{A})$$

$$= ABC + A\overline{B}C + ABC + AB\overline{C} + ABC + \overline{A}BC$$

$$= ABC + A\overline{B}C + AB\overline{C} + \overline{A}BC \quad \text{Rule 5} : [A + A = A]$$

Ex. 5.2: Convert the given expression in standard SOP form

$$Y = A + AB + ABC$$

$$= A \cdot (B + \overline{B}) \cdot (C + \overline{C}) + AB \cdot (C + \overline{C}) + ABC$$

$$= (AB + A\overline{B}) \cdot (C + \overline{C}) + ABC + AB\overline{C} + ABC$$

$$= ABC + AB\overline{C} + AB\overline{C} + AB\overline{C} + ABC + AB\overline{C} + ABC$$

$$= ABC + AB\overline{C} + AB\overline{C} + AB\overline{C} + ABC + ABC + ABC$$

Similarly product of sums form can be converted to standard product of sums by ORing the terms in the expression with terms formed by ANDing the variable and its complement which are not present in that term. For example for a three literal expression with literals A, B and C if there is a term A + B where literal C is missing, then form term  $C.\overline{C}$  and OR A + B with it. Therefore, we get,

$$A + B + C \cdot \overline{C} = (A + B + C) (A + B + \overline{C})$$

Rule 12:  $(A + BC) = (A + B) (A + C)$

Ex. 5.3: Convert the given expression in standard POS form

$$Y = (A + B) (B + C) (A + C)$$

$$= (A + B + C \cdot \overline{C}) (B + C + A \cdot \overline{A}) (A + C + B \cdot \overline{B})$$

$$= (A + B + C) (A + B + \overline{C}) (A + B + C) (\overline{A} + B + C) (A + B + C) (A + \overline{B} + C)$$

$$= (A + B + C) (A + B + \overline{C}) (\overline{A} + B + C) (A + \overline{B} + C)$$

Ex. 5.4: Convert the given expression in standard POS form

$$Y = A (A + B) (A + B + C)$$

EEEbooks4U

165

## 5.4 Algebraic Simplification

The Boolean algebra theorems that we studied in the previous section can be used to simplify expressions for a logic circuit. The steps for simplification of boolean expression using boolean algebra can be generalized as follows:

- The original expression is put into the sum of products form by repeated application of DeMorgan's theorems and multiplication of terms.

- Once it is in the sum of products form, the product terms are checked for common factors and factoring is performed whenever possible.

Boolean rules are used simultaneously which results in the elimination of one or more terms.

Now we will see some examples to illustrate the above mentioned technique.

**Ex. 5.5:** Simplify the expression  $Z = A B + A \overline{B} \cdot (\overline{A} \overline{C})$

Sol. :

Step 1: Apply the DeMorgan's theorem and multiply out all terms to get expression in sum of products form

$$Z = A B + A \overline{B} \cdot (\overline{A} \overline{C})$$

$= A B + A \overline{B} \cdot (\overline{A} + \overline{C})$  De Morgan's theorem 1

$= A B + A \overline{B} \cdot (A + C)$  Rule :  $[\overline{A} = A]$

$= A B + A \overline{B} A + A \overline{B} C$  Distributive law

Step 2: Search for common terms for factorization and apply boolean rules

$$Z = A B + A \overline{B} A + A \overline{B} C$$

$$= A B + A \overline{B} + A \overline{B} C$$

$$= A B + A \overline{B} (1 + C)$$

$$= A B + A \overline{B}$$

$$= A (B + \overline{B})$$

$$= A (B + \overline{B})$$

$$= A (B + \overline{A})$$

Ex. 5.6: Simplify the logic circuit shown in Fig. 5.2 and implement simplified logic circuit using logic gates.

Fig. 5.2

**Sol.**: The expression for given logic circuit is

$$Y = A B + A (B + C) + B (B + C)$$

Step 1: Multiply out all terms to get expression in sum of product form

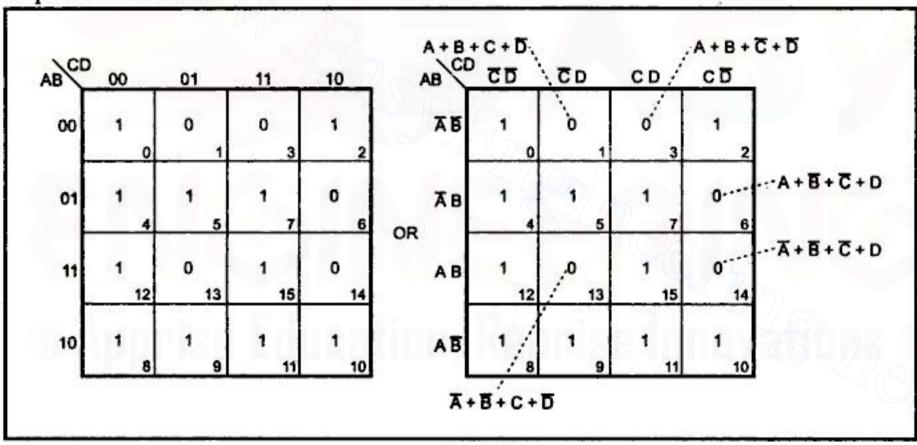

example, in Fig. 5.5 (a) the only change that occurs in moving along the bottom row from AB to AB is the change from B to B. Similarly, the only change that occurs in moving down the right column from AB to AB is the change from B to AB. Irrespective of number of variables the labels along each row and column must conform to the single-change rule.

169

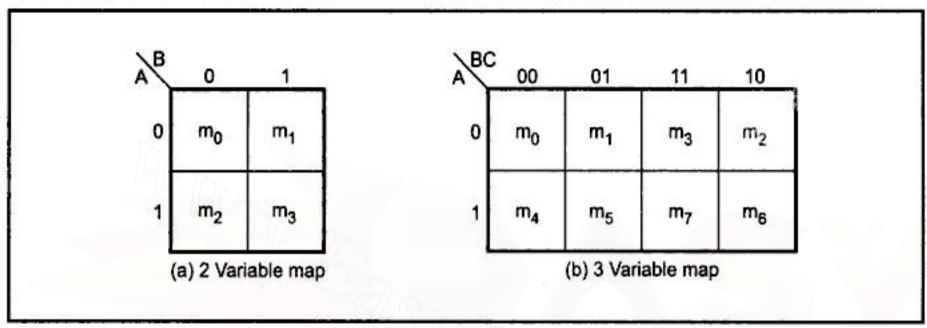

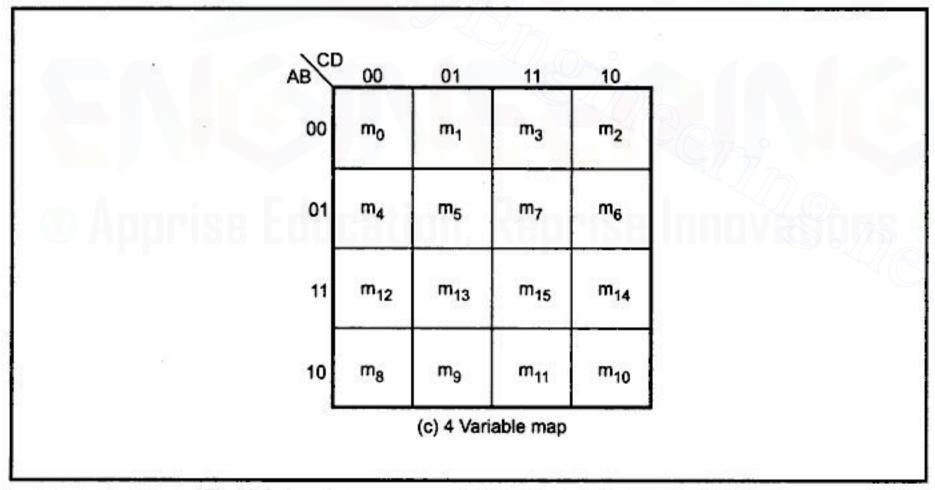

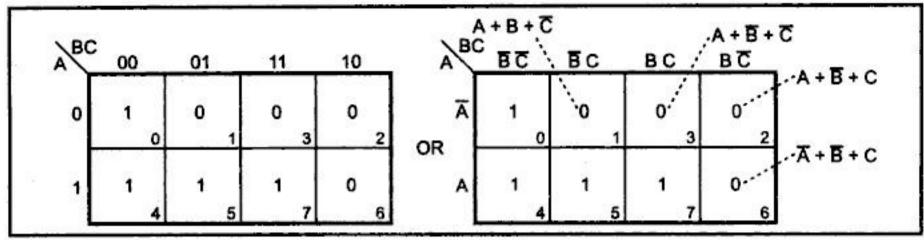

The Fig. 5.6 shows another way to label the rows and columns of a 2, 3 and 4 variable maps and the product terms corresponding to each cell. Here, instead of writing actual product terms, corresponding shorthand minterm notations are written in the cell, and row and columns are marked with 0s and 7s instead of variables.

Fig. 5.6 Another way to represent 2, 3 and 4 variable maps

## 5.5.2 Plotting A Karnaugh Map

We know that logic function can be represented in various forms such as truth table, SOP boolean expression and POS boolean expression. In this section we will see the procedures to plot the given logic function in any form on the Karnaugh map. Sol.: The expression has 3 variables and hence it can be plotted using 3-variable map as shown below.

173

$$(A + \overline{B} + C) = M_2$$

,  $(A + \overline{B} + \overline{C}) = M_3$ ,  $(\overline{A} + \overline{B} + C) = M_6$ ,  $(A + B + \overline{C}) = M_1$

Fig. 5.10

Ex. 5.13: Plot Boolean expression

$$Y = (A+B+C+\overline{D})(A+\overline{B}+\overline{C}+D)(A+B+\overline{C}+\overline{D})(\overline{A}+\overline{B}+C+\overline{D})(\overline{A}+\overline{B}+\overline{C}+D)$$

Sol.: The expression has 4 variables and hence it can be plotted using 4-variable map as shown below

Fig. 5.11

$$\begin{array}{ll} (A+B+C+\overline{D})=M_1,\,(A+\overline{B}+\overline{C}+D)=M_6,\,(A+B+\overline{C}+\overline{D})=M_3,\\ (\overline{A}+\overline{B}+C+\overline{D})=M_{13},\,(\overline{A}+\overline{B}+\overline{C}+D)=M_{14} \end{array}$$

## 5.5.3 Grouping Cells for Simplification